## Time-of-Flight 3D Imaging based on a SPAD-TDC Pixel Array in Standard 65 nm CMOS Technology

### Priyanka Kumar

## Time-of-Flight 3D Imaging based on a SPAD-TDC Pixel Array in Standard 65 nm CMOS Technology

#### THESIS

submitted in partial fulfilment of the requirements for the degree of

MASTER OF SCIENCE

in

MICROELECTRONICS

by

Priyanka Kumar born in Jhansi, India

Electronics Research Laboratory

Department of Microelectronics & Computer Engineering

Faculty of Electrical Engineering, Mathematics and Computer Science

Delft University of Technology

Several concepts used in this thesis are protected by patents.

Copyright © 2011 Priyanka Kumar All rights reserved.

# DELFT UNIVERSITY OF TECHNOLOGY DEPARTMENT OF

#### MICROELECTRONICS & COMPUTER ENGINEERING

The undersigned hereby certify that they have read and recommend to the Faculty of Electrical Engineering, Mathematics and Computer Science for acceptance a thesis entitled "Time-of-flight 3D Imaging based on a SPAD-TDC Pixel Array in Standard 65 nm CMOS Technology" by Priyanka Kumar in partial fulfillment of the requirements for the degree of Master of Science.

| Dated: September 9, 2011 |                               |

|--------------------------|-------------------------------|

| Chairman and Co-Advisor: | prof. dr. ir. Edoardo Charbon |

|                          | prof. dr. fr. Edoardo Charbon |

| Co-Advisor:              | dr. R. Bogdan Staszewski      |

| Committee Members:       |                               |

|                          | dr. ir. Nick van der Meijs    |

|                          | Andre Borowski                |

### Abstract

The interest in high performance three-dimensional (3D) imaging has grown in recent years due to immense demand in engineering, science, medicine and entertainment domains. The driving goals of state-of-the-art 3D imagers are high sensitivity to light and fine depth resolution at long range. Furthermore, high level of integration is desirable to achieve low system cost. To meet these demands, the industry has started to transition from traditional analog techniques to standard CMOS based solutions.

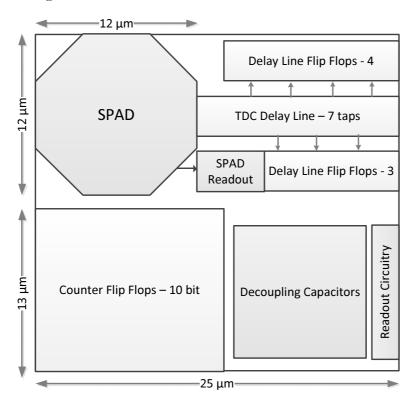

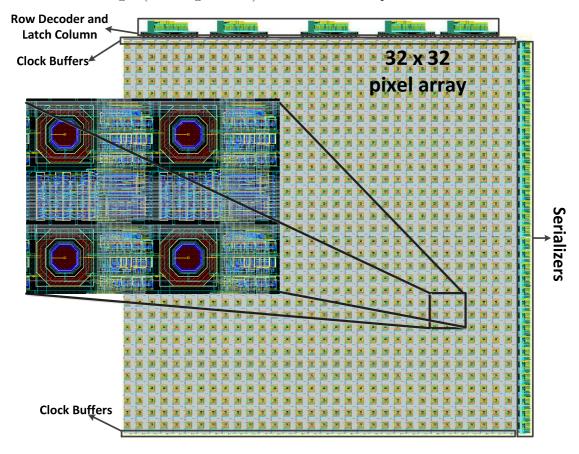

In this thesis, a novel time-of-flight 3D CMOS imager is proposed. The focus of the design is low power consumption while maintaining human-eye safety requirements. The imager targets security applications, primarily facial recognition, but is also suitable for automotive vision and robotics. In this work, a prototype of a 32x32 pixel array is designed, where each pixel consists of a single-photon avalanche diode as photodetector and a time-to-digital converter (TDC) for fast image acquisition. The imager is expected to achieve millimeter-level depth resolution for range as long as 30 m and has a maximum frame-rate of 1000 fps. Each pixel is constructed within 25x25  $\mu$ m² area and has a fill factor of 5.76%. The layout implementation has been carried out in a 65 nm CMOS technology and would be the first of its kind at this process node.

## Contents

| Abstract             | vi                                                 |

|----------------------|----------------------------------------------------|

| Contents             | X                                                  |

| List of Fig          | uresxv                                             |

| List of Tal          | oles xx                                            |

| $\mathbf{Acknowled}$ | gments xxii                                        |

| Acronyms             | xxv                                                |

| 1. Introd            | $\operatorname{uction}$                            |

| 1.1 Ap               | plications of 3D Imaging                           |

| 1.1.1                | Machine Vision                                     |

| 1.1.2                | Security                                           |

| 1.1.3                | Human-Computer Interaction                         |

| 1.1.4                | Biomedical Imaging                                 |

| 1.2 3D               | Imaging Techniques                                 |

| 1.2.1                | General Classification of Optical 3D Image Sensors |

| 1.2.2                | Solid-State Time-of-Flight Imagers                 |

| 1.3 Im               | ager Performance Parameters                        |

| 1.3.1                | Range $(Z_{max})$                                  |

| 1.3.2                | Depth Resolution ( $\Delta Z$ )                    |

| 1.3.3                | Lateral Resolution $(N_x \times N_y)$              |

| 1.3.4                | Field of View                                      |

| 1.3.5                | Fill Factor                                        |

| 1.3.6                | Repeatability                                      |

| 1.3.7                | Frame Rate (N fps)                                 |

| 1.3.8                | Constraints:                                       |

| 1.4 Mo               | tivation                                           |

| 1.5 De               | sign Methodology11                                 |

| 1.6 Or               | ganization                                         |

| o D 1                | J                                                  |

|   | 2.1   | Gen            | neric TCSPC Imager Architecture          | 13 |

|---|-------|----------------|------------------------------------------|----|

|   | 2.2   | Sing           | gle Photon Avalanche Diode               | 14 |

|   | 2.2.  | 1              | Device Structure                         | 14 |

|   | 2.2.  | 2              | SPAD Performance Parameters              | 15 |

|   | 2.2.  | 3              | SPAD Readout                             | 17 |

|   | 2.3   | Tim            | ne to Digital Converter                  | 19 |

|   | 2.3.  | 1              | Delay Line (DL) Based Architecture       | 20 |

|   | 2.3.  | 2              | Coarse-Fine Architecture                 | 22 |

|   | 2.3.  | 3              | Looped TDC Architectures                 | 24 |

|   | 2.4   | Sun            | nmary                                    | 25 |

| 3 | . Sys | $\mathbf{tem}$ | Design                                   | 27 |

|   | 3.1   | Ima            | ger Specifications                       | 27 |

|   | 3.2   | Ima            | ger Architecture                         | 29 |

|   | 3.2.  | 1              | At The Light Source                      | 29 |

|   | 3.2.  | 2              | At The Detector End                      | 30 |

|   | 3.2.  | 3              | Time of Flight Estimation                | 33 |

|   | 3.2.  | 4              | Reconnaissance [46]                      | 35 |

|   | 3.2.  | 5              | Improving Resolution                     | 36 |

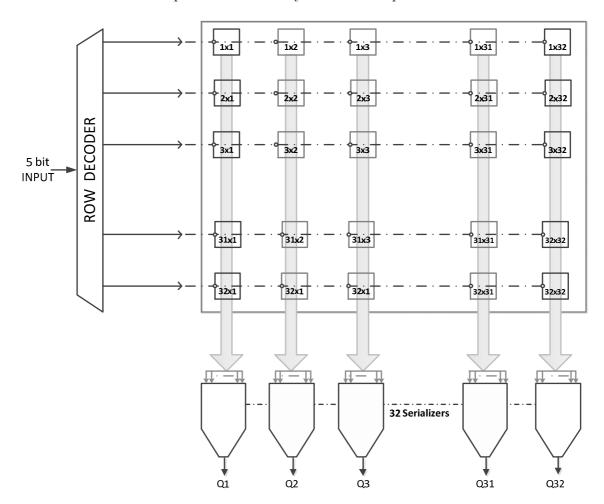

|   | 3.2.  | 6              | Readout in 32x32 Pixel Array             | 38 |

|   | 3.2.  | 7              | Readout Mechanisms                       | 38 |

|   | 3.2.  | 8              | Readout Blocks                           | 39 |

|   | 3.2.  | 9              | Estimation of Readout Speed              | 39 |

|   | 3.2.  | 10             | Power Consumption                        | 40 |

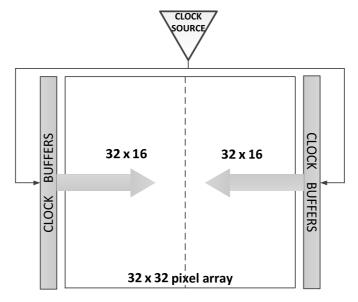

|   | 3.2.  | 11             | Clock Distribution                       | 41 |

|   | 3.2.  | 12             | Controller                               | 42 |

|   | 3.2.  | 13             | Imager Architecture                      | 43 |

|   | 3.3   | Sun            | nmary                                    | 44 |

| 4 | . Cir | cuit           | Design & Implementation                  | 45 |

|   | 4.1   | Pixe           | el Level Building Blocks                 | 45 |

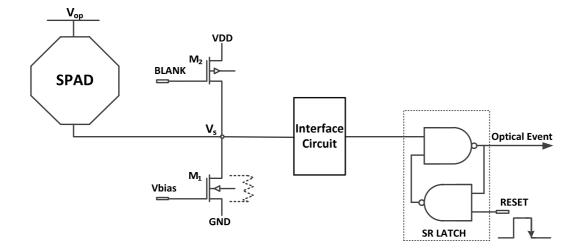

|   | 4.1.  | 1              | Design of SPAD – TDC Interface Circuitry | 45 |

|   | 4.1.  | 2              | Interface Circuitry                      | 46 |

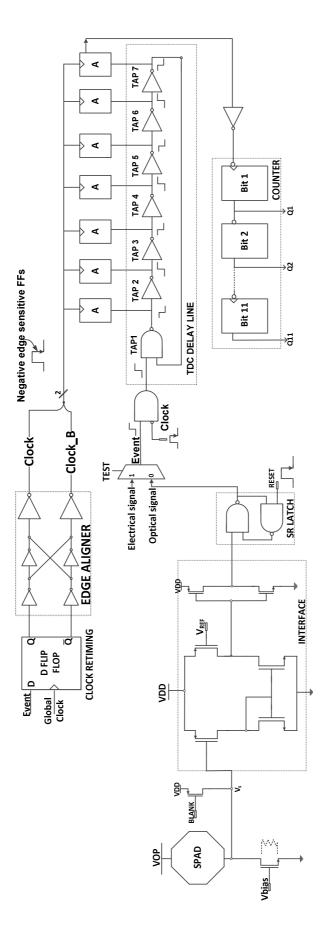

|   | 4.1.  | 3              | Design of TDC Architecture [46]          | 49 |

| 4.1.4      | Reducing Power Consumption                  | 60   |

|------------|---------------------------------------------|------|

| 4.1.5      | Simplifying Clock Distribution Network [46] | 61   |

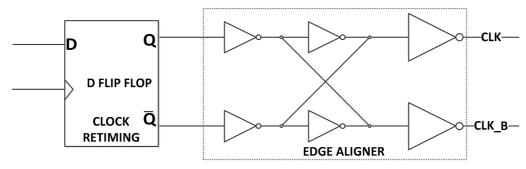

| 4.1.6      | Clock Retiming And Edge Aligner [46]        | 62   |

| 4.1.7      | Pixel Design                                | 63   |

| 4.2 Det    | ailed Design of Sub-Blocks                  | 65   |

| 4.2.1      | Parasitic Modeling                          | 65   |

| 4.2.2      | SPAD-TDC Interface Circuit                  | 69   |

| 4.2.3      | Photon Sensing Interface                    | 71   |

| 4.2.4      | Time to Digital Converter [46]              | 71   |

| 4.2.5      | Clock Retiming and Edge Aligner [46]        | 73   |

| 4.3 Imp    | plementation of Pixel Level Blocks          | 74   |

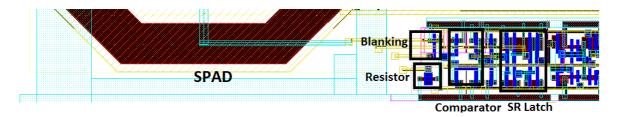

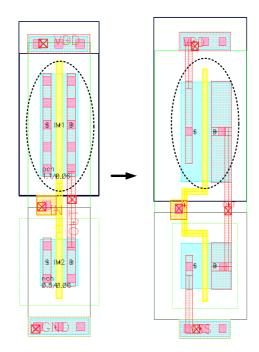

| 4.3.1      | Layout of SPAD -TDC Interface Circuitry     | 74   |

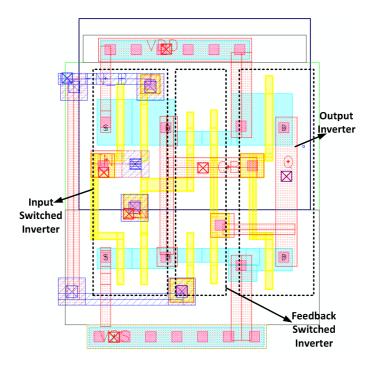

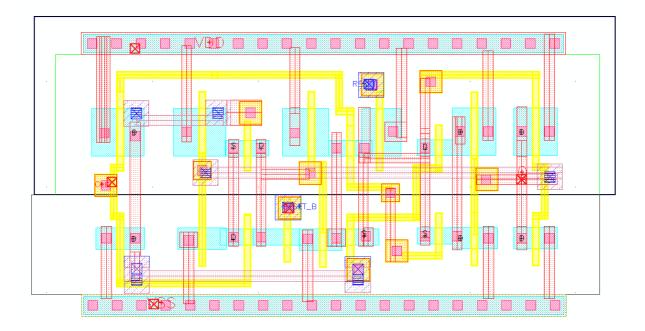

| 4.3.2      | Layout of TDC [46]                          | 75   |

| 4.3.3      | Layout of Clock Retiming Circuit[46]        | 79   |

| 4.3.4      | Decoupling Capacitors                       | 80   |

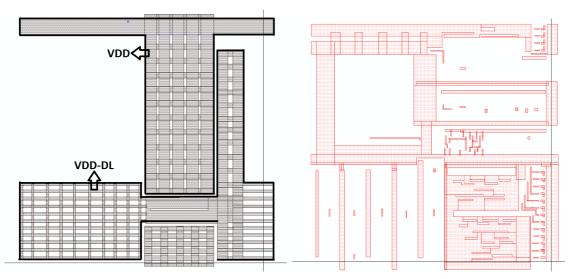

| 4.3.5      | Full Pixel Layout Assembly                  | 81   |

| 4.4 Sys    | tem Integration                             | 83   |

| 4.4.1      | Clock Distribution                          | 83   |

| 4.4.2      | System Readout Design                       | 86   |

| 4.4.3      | Building The Imager Array                   | 88   |

| 4.5 Sun    | nmary                                       | 89   |

| 5. Post-La | ayout Simulation Results                    | . 91 |

| 5.1 Per    | formance at Pixel Level                     | 91   |

| 5.1.1      | 65 nm SPAD Performance                      | 91   |

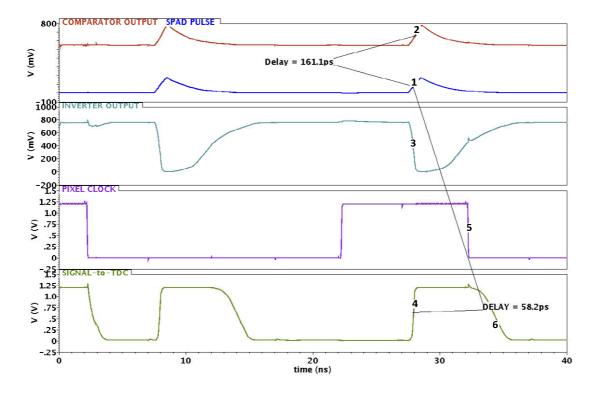

| 5.1.2      | SPAD-TDC Interface                          | 92   |

| 5.1.3      | Time-to-Digital Converter                   | 93   |

| 5.1.4      | Energy Consumption                          | 99   |

| 5.2 Sys    | tem Level Performance                       | 101  |

| 5.2.1      | IR Drop                                     | 101  |

| 5.2.2      | Row Decoder                                 | 104  |

| 5.2.3      | Serializer                                  | 105  |

| 5.3 Sun    | nmary                                       | 106  |

| 5.4     | Future Work | 106 |

|---------|-------------|-----|

| 6. Co   | onclusions  | 109 |

| Append  | dices       | 111 |

| Bibliog | graphy      | 117 |

## List of Figures

| Figure 1.1 - (a) Triangulation method used to calculate coordinates and distance of a point from baseline; (b) Moiré pattern                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2 - Basic holographic setup [3]                                                                                                           |

| Figure 1.3 - Classification of state-of-the-art solid-state optical ToF image sensors [1][9]                                                       |

| Figure 1.4 - Laser modulation techniques: (a) continuous wave modulation; (b) pulsed modulation                                                    |

| Figure 1.5 - Range estimation through phase measurement [9]                                                                                        |

| Figure 1.6 - Range estimation through time interval measurement                                                                                    |

| Figure 1.7 - Graphical representation of resolution [19].                                                                                          |

| Figure 1.8 - Graphical representation of accuracy and repeatability [19]                                                                           |

| Figure 2.1 - Block diagram of SPAD based TCSPC 3D imager                                                                                           |

| Figure 2.2 - I-V characteristic and gain of SPAD in Geiger mode of operation [23]14                                                                |

| Figure 2.3 - Device structure of SPAD [25].                                                                                                        |

| Figure 2.4 - Transmitted and received pulses [28]                                                                                                  |

| Figure 2.5 - Full width at half maximum.                                                                                                           |

| Figure 2.6 - SPAD operation with (a) passive quenching; (b) build-up of voltage and the concept of dead time [23]                                  |

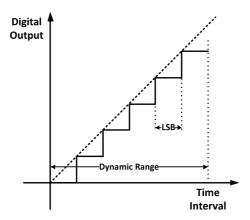

| Figure 2.7 - Ideal transfer characteristic of TDC.                                                                                                 |

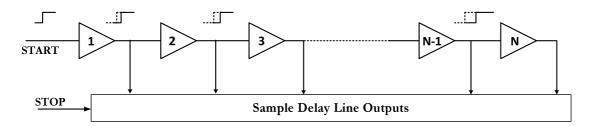

| Figure 2.8 - Conceptual diagram of delay line                                                                                                      |

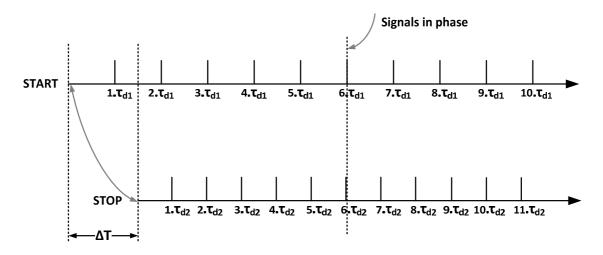

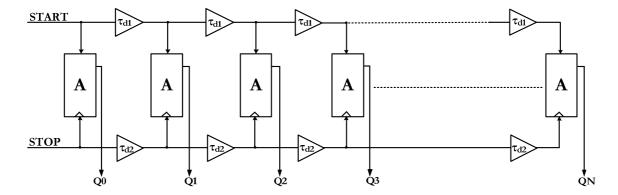

| Figure 2.9 - Operating principle of Vernier delay line based TDC                                                                                   |

| Figure 2.10 - A basic Vernier delay line based TDC architecture                                                                                    |

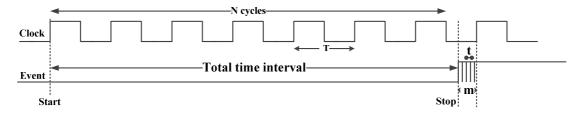

| Figure 2.11 - Concept of coarse-fine TDC.                                                                                                          |

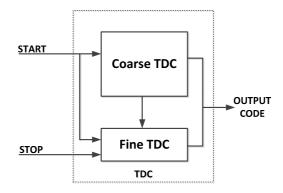

| Figure 2.12 - Block diagram of coarse-fine TDC.                                                                                                    |

| Figure 2.13 - Coarse-fine TDC: (a) conceptual diagram of time amplification; (b) time amplifier [35]                                               |

| Figure 2.14 - Concept of a looped TDC.                                                                                                             |

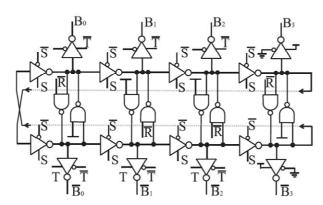

| Figure 2.15 - Ring oscillator based on cross coupled inverters [8]                                                                                 |

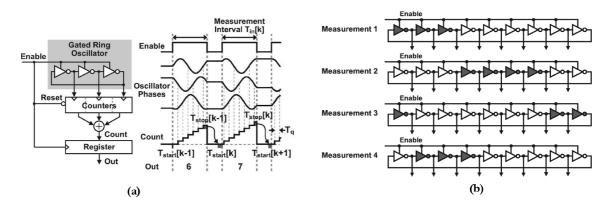

| Figure 2.16 - (a) Gated ring oscillator TDC; (b) the concept of barrel shifting of GRO delay elements to achieve first order mismatch shaping [42] |

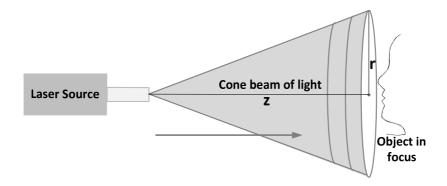

| Figure 3.1 - Illumination of the scene using cone beam of light                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

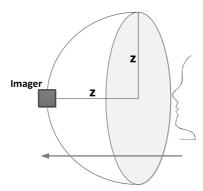

| Figure 3.2 - A side-view of the reflected light from the 3D object. The reflection forms a hemisphere with radius equal to object range                                                                                                                                  |

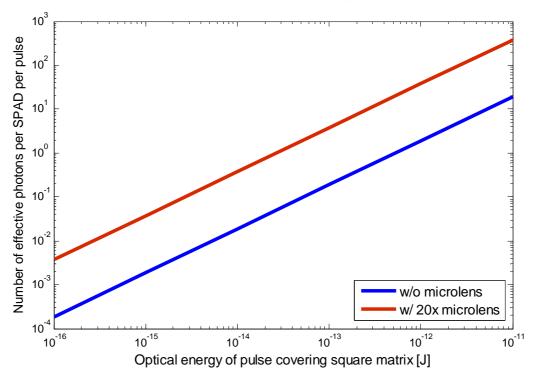

| Figure $3.3$ - Relationship between the number of effective photons impinging on a single detector and laser pulse energy covering the entire imaging matrix of $1000 \times 1000$ pixels [28]. The fill factor is assumed to be $5\%$ and PDP is approximated to $50\%$ |

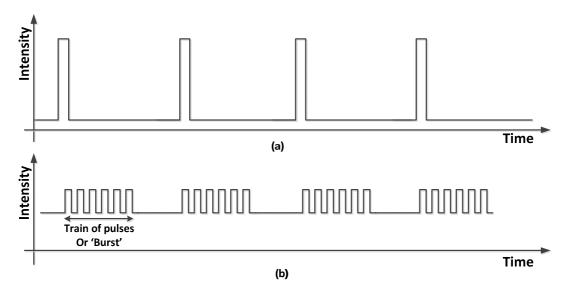

| Figure 3.4 - Pulsed mode of operation: (a) high intensity, low frequency pulses; (b) low intensity, high frequency pulses (a preferred mode of operation)                                                                                                                |

| Figure 3.5 - ToF measurement technique for lower power consumption                                                                                                                                                                                                       |

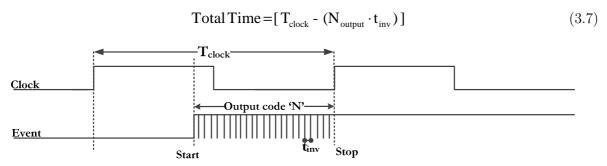

| Figure 3.6 - The concept of reconnaissance: (a) when the object is 200 ns apart, (b) when the object is 100 ns apart                                                                                                                                                     |

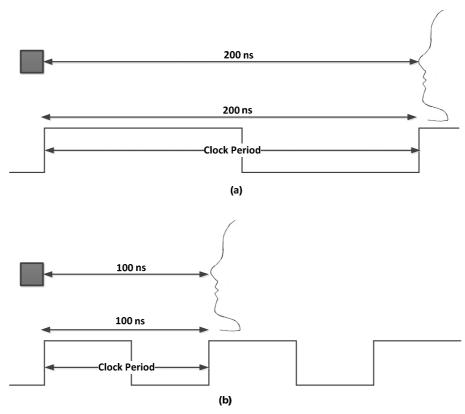

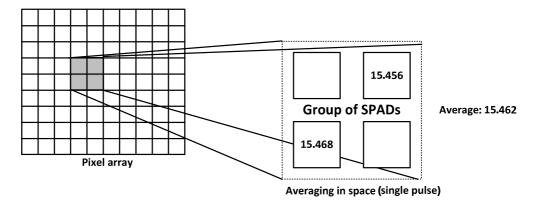

| Figure 3.7 - Averaging in space (single pulse)                                                                                                                                                                                                                           |

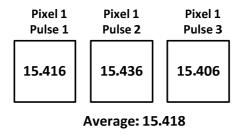

| Figure 3.8 - Averaging in time (multiple pulses hitting the same pixel)                                                                                                                                                                                                  |

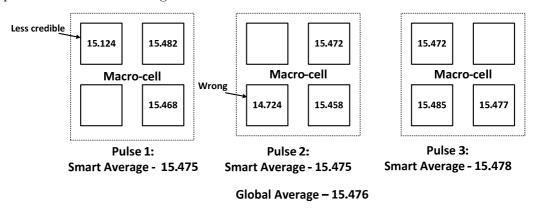

| Figure 3.9 - Averaging in time and space across multiple pulses                                                                                                                                                                                                          |

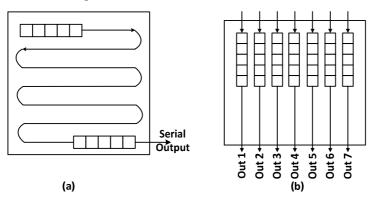

| Figure 3.10 - Sequential readout: (a) pixel based readout (no parallelism); (b) column readout (limited parallelism) [23]                                                                                                                                                |

| Figure 3.11 - Block diagram of system readout                                                                                                                                                                                                                            |

| Figure 3.12 - Clock distribution network                                                                                                                                                                                                                                 |

| Figure 3.13 - Imager architecture [28].                                                                                                                                                                                                                                  |

| Figure 4.1 - SPAD-TDC Interface circuit                                                                                                                                                                                                                                  |

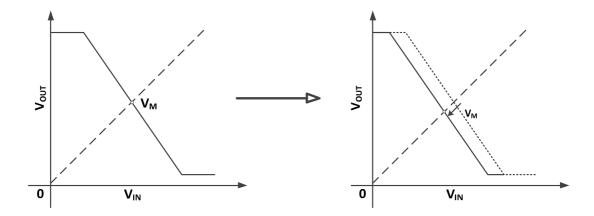

| Figure 4.2 - Transfer characteristic of an inverter. The inverter threshold is modified by shifting the curve left or right                                                                                                                                              |

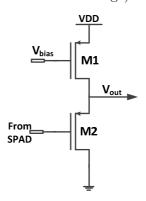

| Figure 4.3 - PMOS source follower. 47                                                                                                                                                                                                                                    |

| Figure 4.4 - Comparator circuits: (a) with current source; (b) without current source;48                                                                                                                                                                                 |

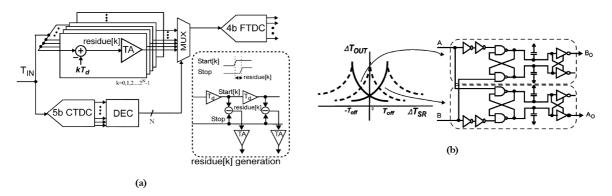

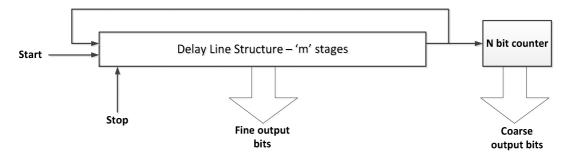

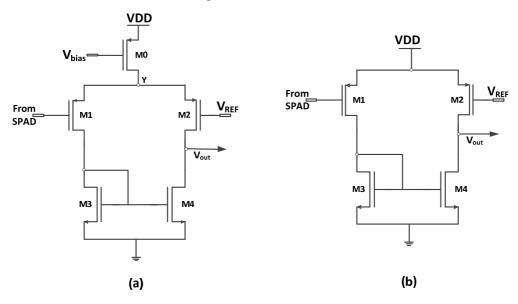

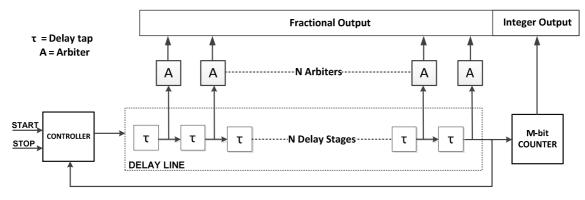

| Figure 4.5 - Block diagram of ring oscillator based TDC                                                                                                                                                                                                                  |

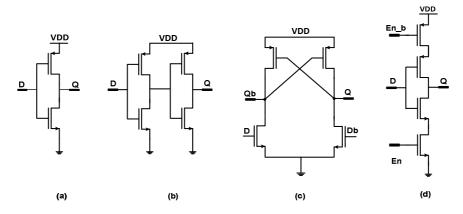

| Figure 4.6 - Different types of delay taps: (a) inverter; (b) buffer; (c) differential inverter; (d) switched inverter                                                                                                                                                   |

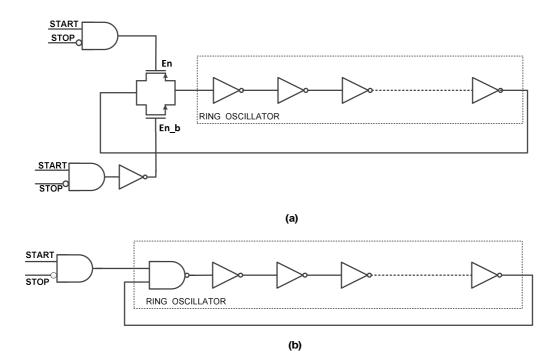

| Figure 4.7- Methods to control the ring oscillation: (a) using TG; (b) using AND gate 52                                                                                                                                                                                 |

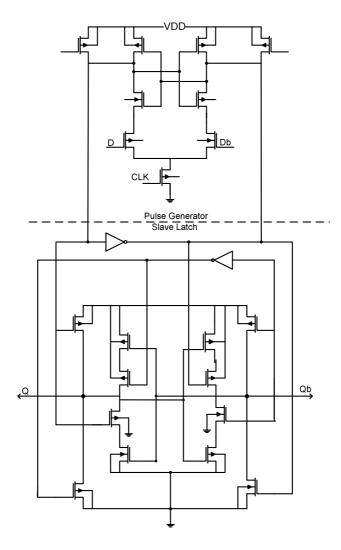

| Figure 4.8 - Circuit diagram of high resolution symmetric flip-flop [49]53                                                                                                                                                                                               |

| Figure 4.9 – Dynamic master-slave flip-flop                                                                                                                                                                                                                              |

| Figure 4.10 - SRAM based latch. 54                                                                                                                                                                                                                                       |

| Figure 4.11 - NAND based SR latch                                                                                                                                                                                                                                        |

| Figure 4.12 - Switches in delay line                                                                                                                                                                                                                                     |

| Figure 4.13 - Switched inverter based delay line                                                                                                                                                                                                                         |

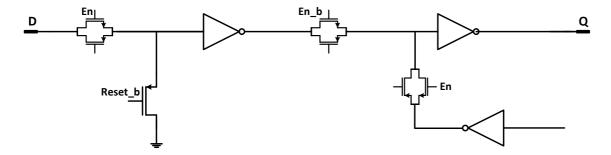

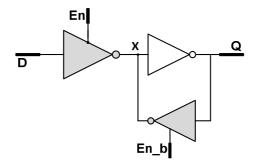

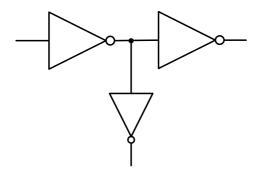

| Figure 4.14 - Switched inverter based latch                                                                                                                                                                                                                              |

| Figure 4.15 - Switched inverter based latch in delay line                                                                                                                                                                    | 57        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

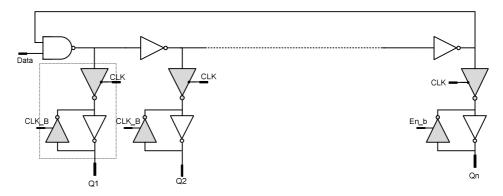

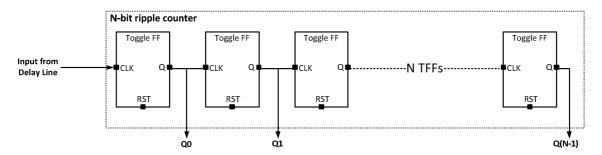

| Figure 4.16 - A toggle flip-flop circuit.                                                                                                                                                                                    | 58        |

| Figure 4.17 - Circuit of binary ripple counter                                                                                                                                                                               | 58        |

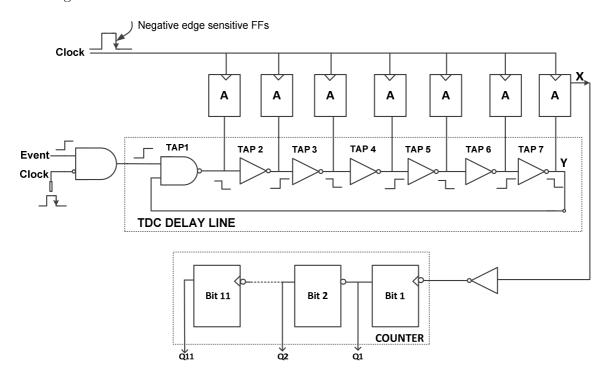

| Figure 4.18 - Ring oscillator based TDC.                                                                                                                                                                                     | 60        |

| Figure 4.19 - High energy consumption with clock having $50\%$ duty cycle                                                                                                                                                    | 61        |

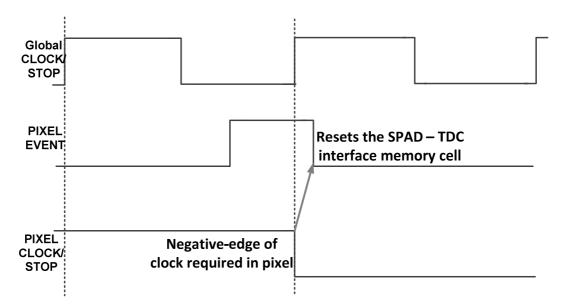

| Figure 4.20 - Low duty cycle clock generation.                                                                                                                                                                               | 61        |

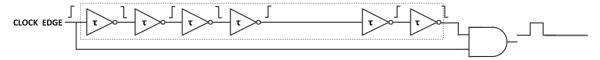

| Figure 4.21 - Clock retiming waveform.                                                                                                                                                                                       | 63        |

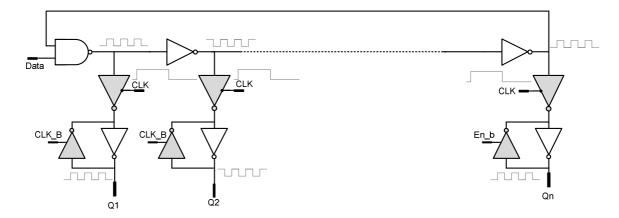

| Figure 4.22 - Clock retiming and edge aligner circuit                                                                                                                                                                        | 63        |

| Figure 4.23 - Full Pixel Circuit.                                                                                                                                                                                            | 64        |

| Figure 4.24 - Test-bench for parasitic modelling (single stage of TDC)                                                                                                                                                       | 65        |

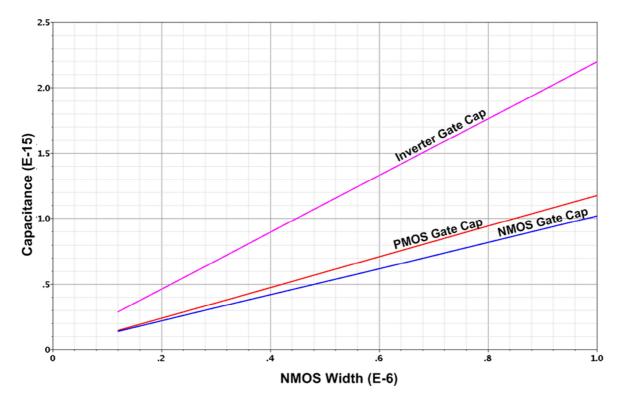

| Figure 4.25 - Variation in inverter gate capacitance with increasing gate width (PM = $2*NMOS-width$ ).                                                                                                                      |           |

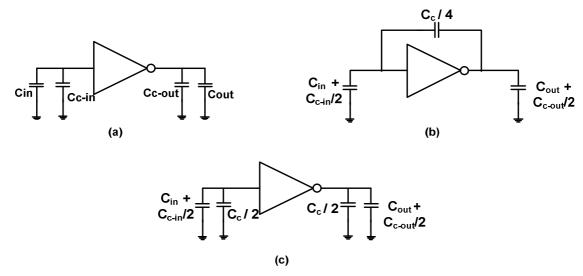

| Figure 4.26 - Parasitic modelling: (a) lumped components provided by Cadence PE back-annotation; (b) feedback capacitance to model coupling between input an nodes; (c) Miller effect to derive the complete parasitic model | ıd output |

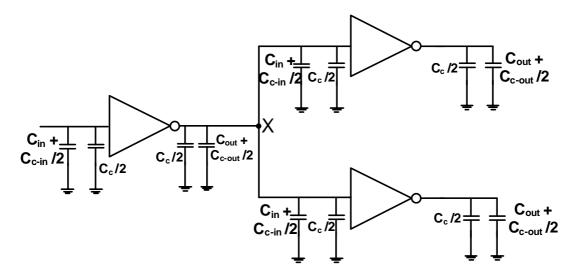

| Figure 4.27 - Lumped parasitic components in a single stage of TDC                                                                                                                                                           | 68        |

| Figure 4.28 - The parasitic modelling of TDC single stage where the plot shows the in delay with increasing size.                                                                                                            |           |

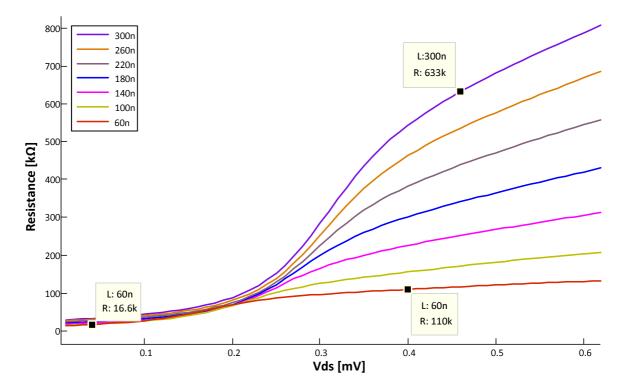

| Figure 4.29 - Change in resistance with increasing length with $V_{\rm GS} = 0.7~V$                                                                                                                                          | 69        |

| Figure 4.30 - Change in NMOS threshold voltage with increasing length                                                                                                                                                        | 70        |

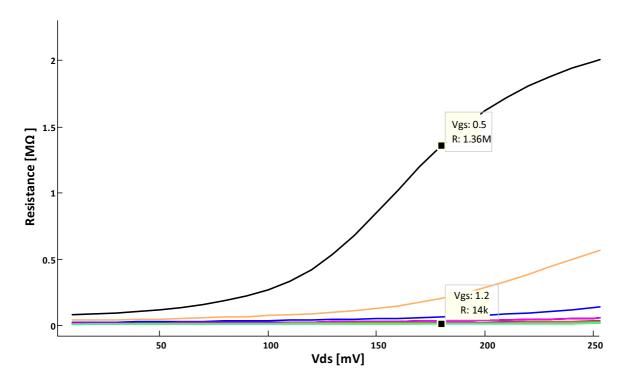

| Figure 4.31 - Range of tunable resistance by varying $V_{\text{GS}}$ with $L=250\ \text{nm}$                                                                                                                                 | 70        |

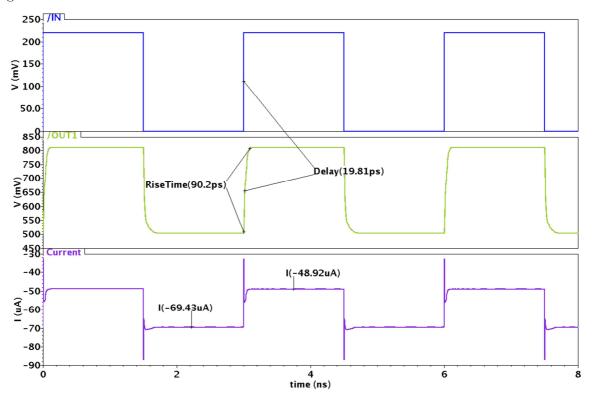

| Figure 4.32 - Transient response of comparator (pre-layout)                                                                                                                                                                  | 71        |

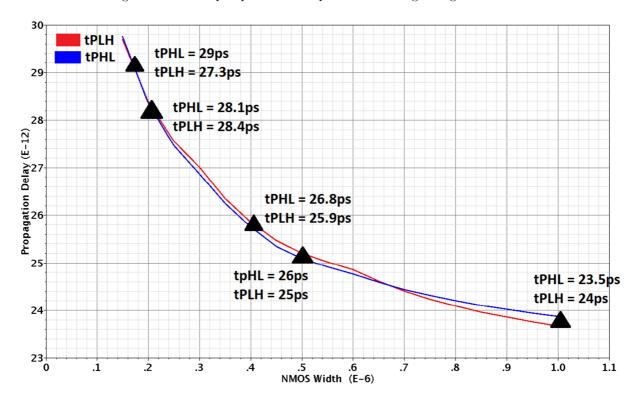

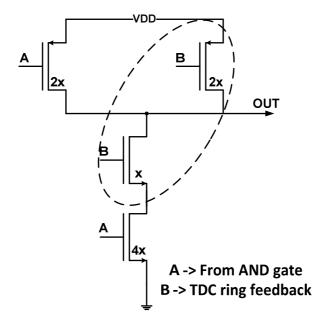

| Figure 4.33 - Sizing of NAND for the first delay tap                                                                                                                                                                         | 72        |

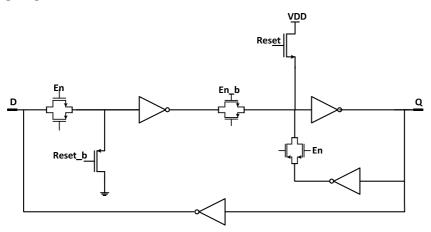

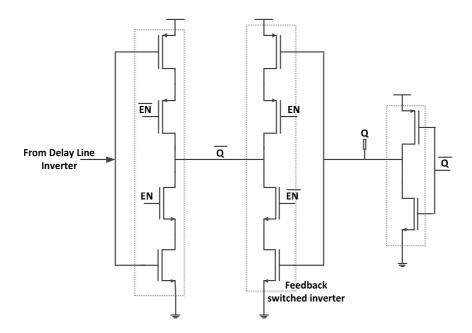

| Figure 4.34 - Circuit diagram of switched inverter based latch                                                                                                                                                               | 73        |

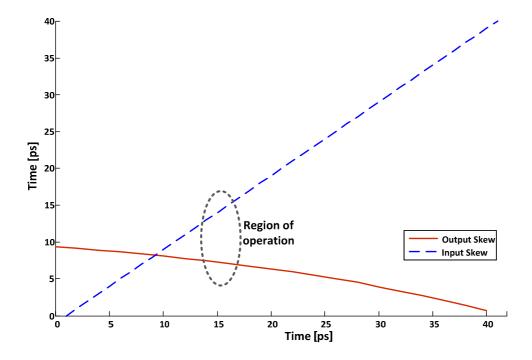

| Figure 4.35 - Output skew with increasing input skew                                                                                                                                                                         | 74        |

| Figure 4.36 - SPAD-TDC interface circuitry.                                                                                                                                                                                  | 75        |

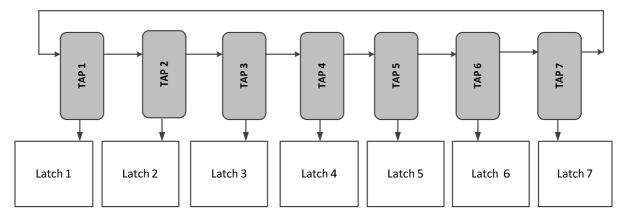

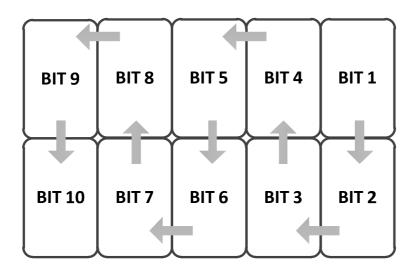

| Figure 4.37 - Placement of delay line taps - Configuration I                                                                                                                                                                 | 75        |

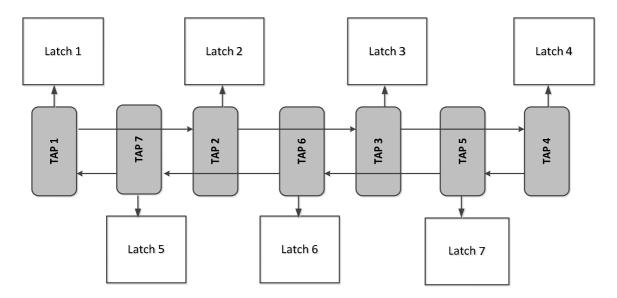

| Figure 4.38 - Placement of delay line taps - Configuration II.                                                                                                                                                               | 76        |

| Figure 4.39 - Pixel Floor-plan.                                                                                                                                                                                              | 76        |

| Figure 4.40 - Optimized inverter layout.                                                                                                                                                                                     | 77        |

| Figure 4.41 - Layout of switched inverter based latch                                                                                                                                                                        | 77        |

| Figure 4.42 - Layout of a toggle flip-flop.                                                                                                                                                                                  | 78        |

| Figure 4.43 - Placement of 10 bit ripple counter                                                                                                                                                                             | 78        |

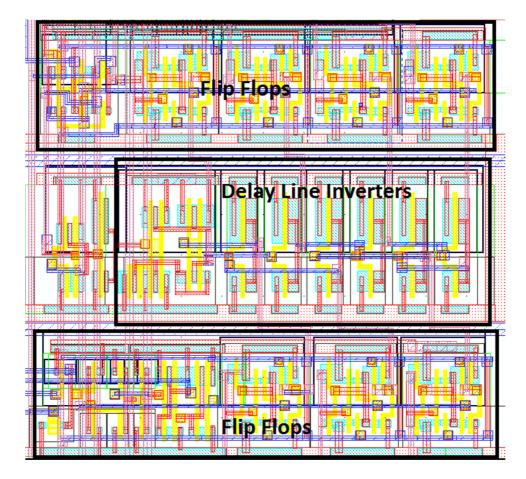

| Figure 4.44 - TDC delay line layout                                                                                                             |

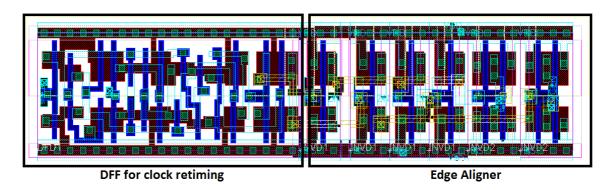

|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.45 - Placement and layout of edge aligner                                                                                              |

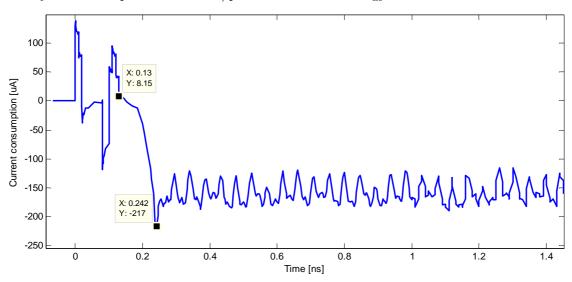

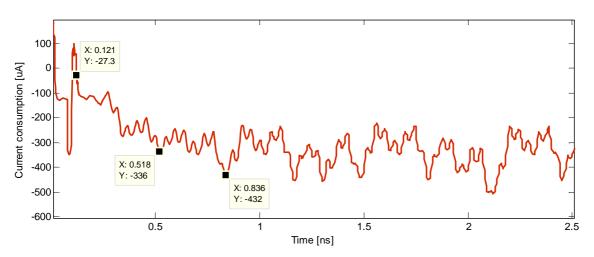

| Figure 4.46 - Current consumption at pixel level for delay line when it begins ring oscillation                                                 |

| Figure 4.47 - Current consumption at pixel level for whole circuit (apart from delay line) $80$                                                 |

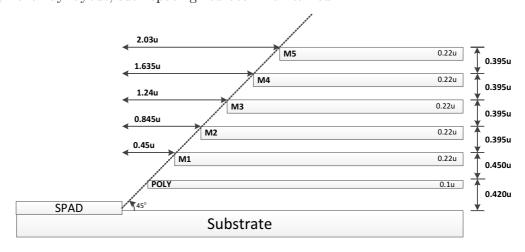

| Figure 4.48 - Metal Stack (upto metal 5) for 65 nm technology                                                                                   |

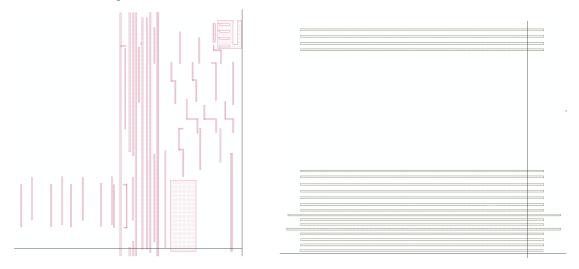

| Figure 4.49 - Routing across the pixel: metal 3 for control inputs (left); metal 4 for outputs (right)                                          |

| Figure 4.50 - Power lines across pixel: metal 5 for power lines (left); and metal 1 for GND (right)                                             |

| Figure 4.51 - Pixel layout.                                                                                                                     |

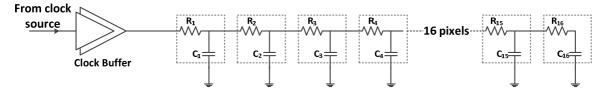

| Figure 4.52 - Elmore delay based RC modelling                                                                                                   |

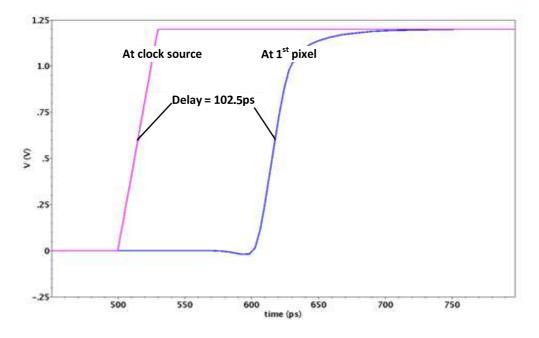

| Figure 4.53 - Clock skew between the $2^{\rm nd}$ and the $16^{\rm th}$ pixel of a column                                                       |

| Figure 4.54 - Logical effort based clock buffer sizing                                                                                          |

| Figure $4.55$ - Minimum clock delay between clock and the first pixel - with clock buffer $86$                                                  |

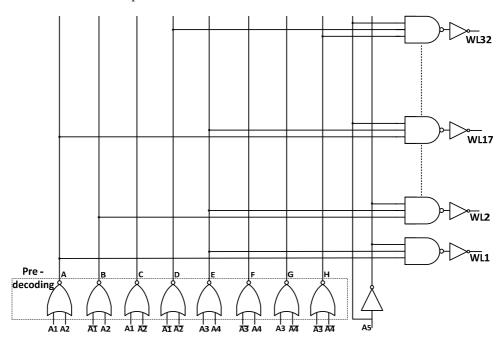

| Figure 4.56 - A 5-bit static row decoder                                                                                                        |

| Figure 4.57 - Serializer using scan flip-flops.                                                                                                 |

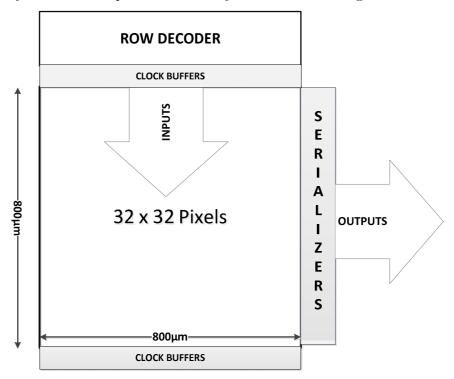

| Figure 4.58 - System floor-plan.                                                                                                                |

| Figure 4.59 - Top level layout (the inset shows the arrangement of pixels)                                                                      |

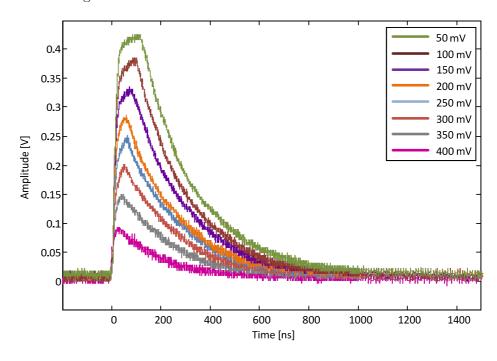

| Figure 5.1 - Change in SPAD signal amplitude with increasing excess bias voltage. The inset shows the excess bias voltage $(V_{OP}$ - $V_{BD})$ |

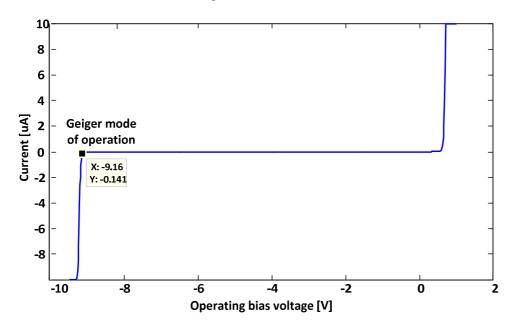

| Figure 5.2 - I-V characteristic of 65 nm SPAD device                                                                                            |

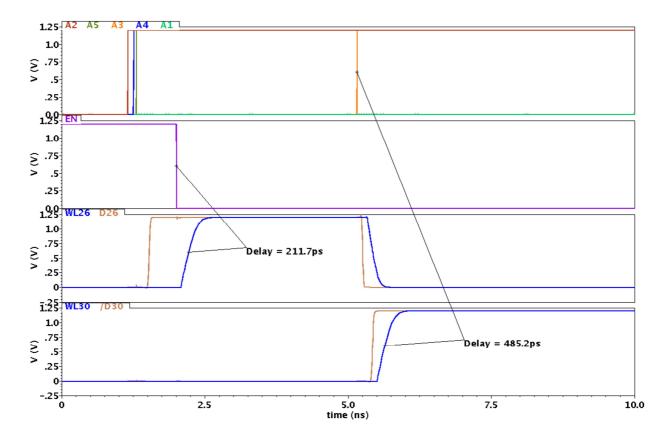

| Figure 5.3 - Transient response of SPAD-TDC interface circuit                                                                                   |

| Figure 5.4 - Output characteristic plot of proposed TDC                                                                                         |

| Figure 5.5 - Metastability curve of latch for $0\rightarrow 1$ input and $1\rightarrow 0$ input signal                                          |

| Figure 5.6 - Propagation delay across each delay tap in the ring oscillator at different corners                                                |

| Figure 5.7 - Differential non-linearity for TDC ring oscillation                                                                                |

| Figure 5.8 - Integral non-linearity for TDC ring oscillation                                                                                    |

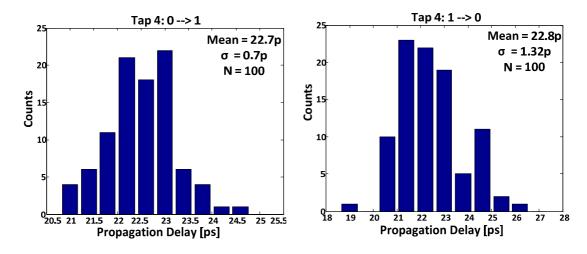

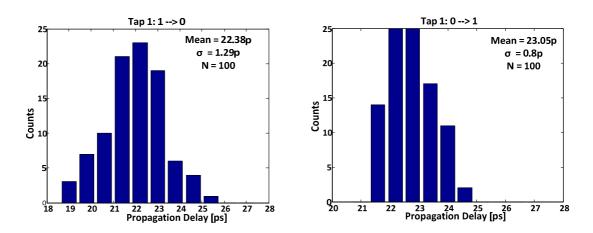

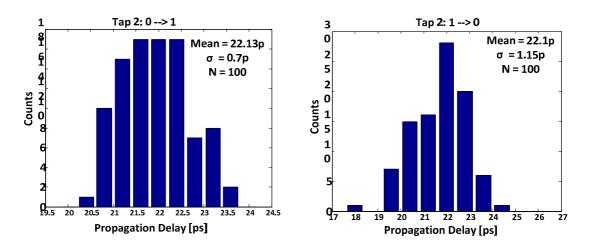

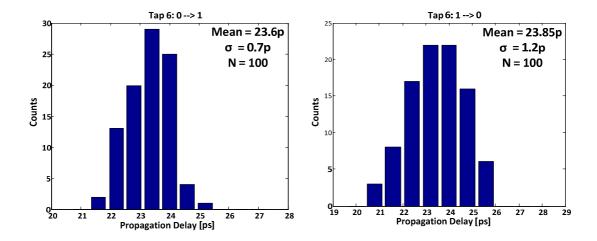

| Figure 5.9 - Mismatch in delay for the centre-most delay tap for $0\rightarrow 1$ (left) and $1\rightarrow 0$ (right) transition.               |

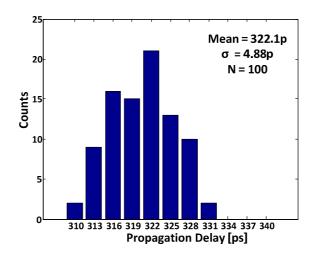

| Figure 5.10 - Mismatch in the delay of a single TDC cycle of 14 delay taps                                                                      |

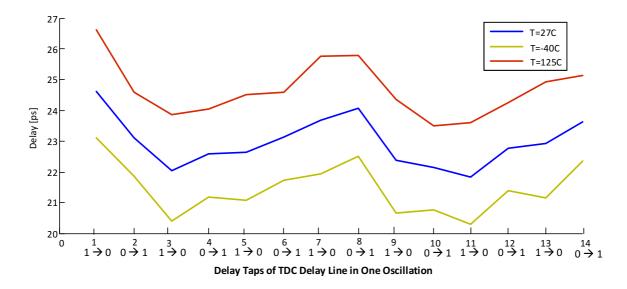

| Figure 5.11 - TDC delay line behaviour across different temperatures                                                                            |

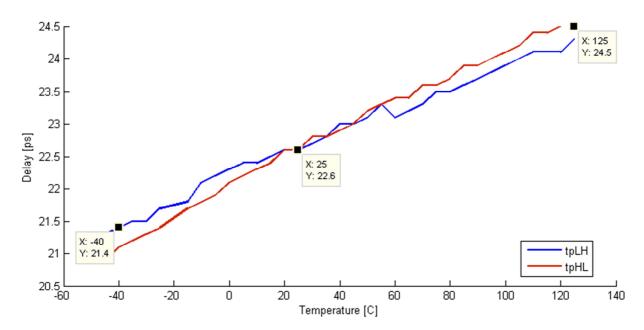

| Figure 5.12 - Change in delay across temperature range of -40° C to $125^{\circ}$ C                                                             |

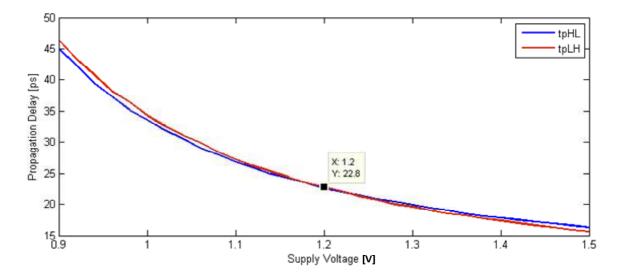

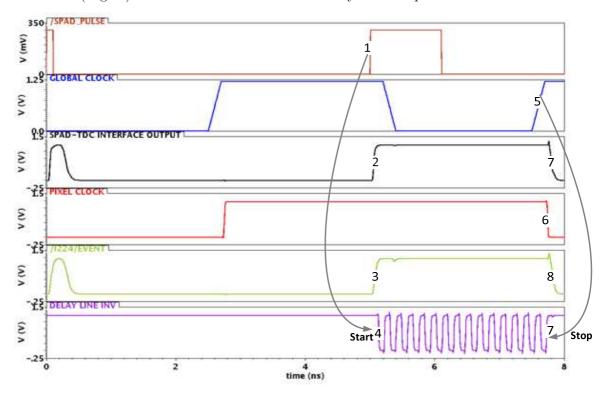

| Figure 5.13 - Variation in inverter propagation delay of centre-most delay tap with reducing supply voltage |

|-------------------------------------------------------------------------------------------------------------|

| Figure 5.14 - Variation of one ring oscillation delay (sum of all delay taps) with supply voltage           |

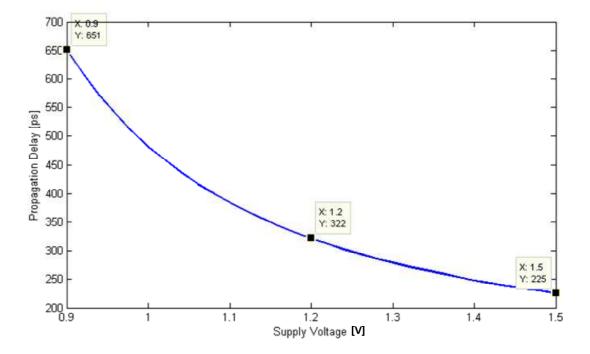

| Figure 5.15 - Energy consumption in pixel over time                                                         |

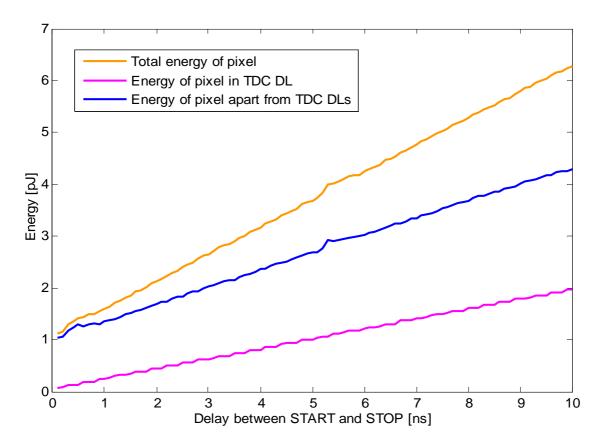

| Figure 5.16 - Sequence of steps indicating the operation of a pixel after the photon hit on the SPAD        |

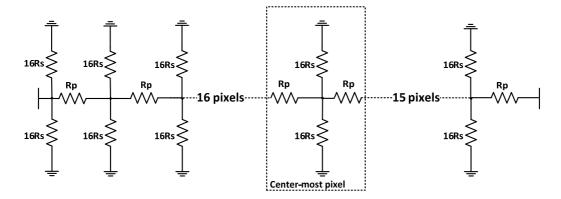

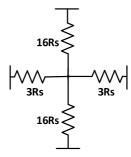

| Figure 5.17 - Resistive network of the centre-most pixel of the array                                       |

| Figure 5.18 - Equivalent resistive network as seen at the centre-most pixel                                 |

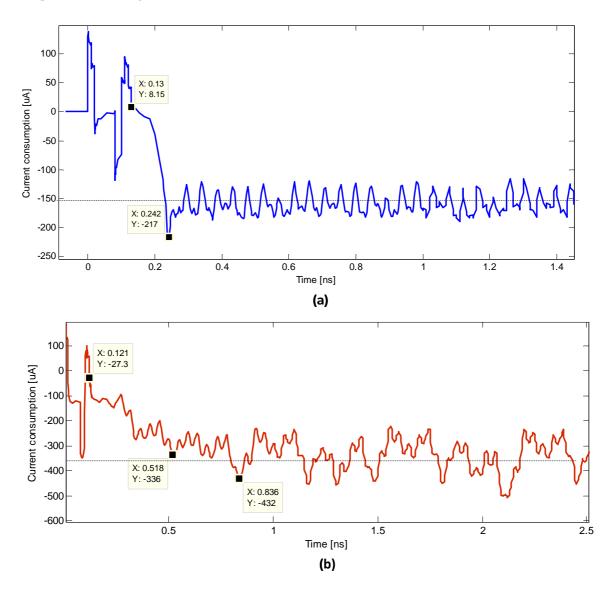

| Figure 5.19 - Current absorption in each pixel for: (a) VDD for delay line; (b) VDD for other circuitry     |

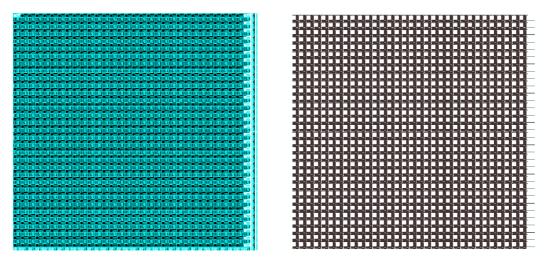

| Figure 5.20 - Layout of GND (left) and VDD (right) grids                                                    |

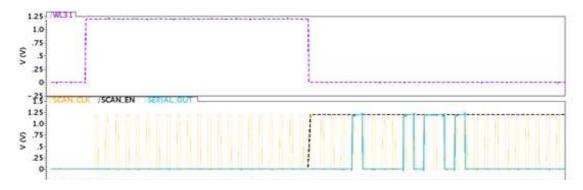

| Figure 5.21 - Operation of row decoder                                                                      |

| Figure 5.22 - A serializer shifting pixel bits. One pixel readout is completed in less than 100 ns          |

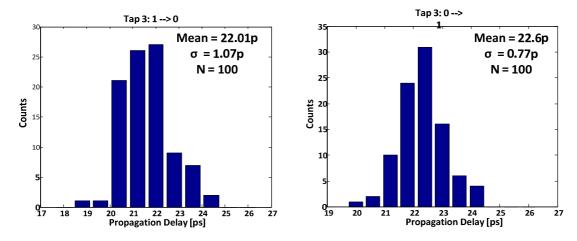

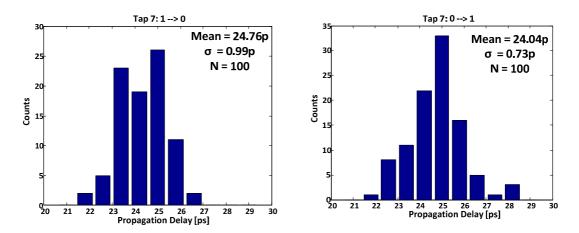

| Figure 6.1 - Mismatch in delay for delay tap 3 for low-to-high (left) and high-to-low (right) transition    |

| Figure 6.2 - Mismatch in delay for delay tap 4 for low-to-high (left) and high-to-low (right) transition    |

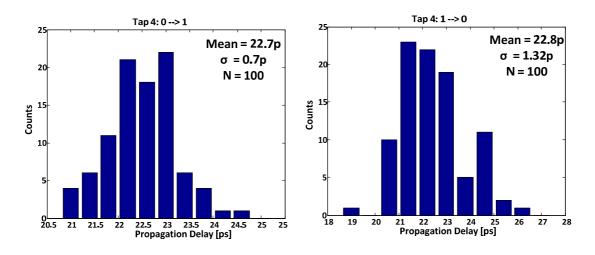

| Figure 6.3 - Mismatch in delay for delay tap 5 for low-to-high (left) and high-to-low (right) transition    |

| Figure 6.4 - Mismatch in delay for delay tap 6 for low-to-high (left) and high-to-low (right) transition    |

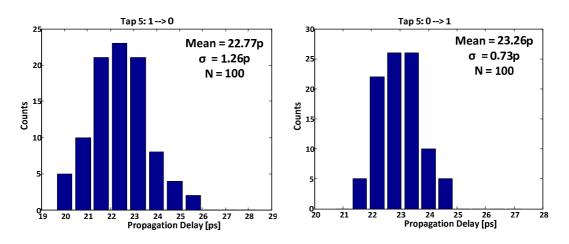

| Figure 6.5 - Mismatch in delay for delay tap 7 for low-to-high (left) and high-to-low (right) transition.   |

## List of Tables

| Table 1.1 - State-of-the-art in 3D TCSPC (SPAD) imaging. The shaded cell indicates th best result of the summary for a given parameter |

|----------------------------------------------------------------------------------------------------------------------------------------|

| Table 3.1 - Imager Specifications                                                                                                      |

| Table 3.2 - Performance parameters of TDC with variation in frequency                                                                  |

| Table 4.1 – Truth-table of SR latch                                                                                                    |

| Table 4.2 - Specifications for TDC                                                                                                     |

| Table 4.3- Comparison of different delay taps                                                                                          |

| Table 4.4 - Truth -table of 6T latch                                                                                                   |

| Table 4.5 - Truth table of 8T latch                                                                                                    |

| Table 4.6 - Extracted parasitic lumped components for different gate widths at input-output nodes                                      |

| Table 5.1 - TDC resolution at typical and 4 corners                                                                                    |

| Table 5.2 - Summary of mismatch in delay across all seven inverters for each type of propagation                                       |

| Table 5.3 - Power consumption analysis at system level                                                                                 |

| Table 5.4 - Summary of post-layout results                                                                                             |

| Table 6.1 - Summary of the performance with respect to state-of-the-art 3D SPAD imagers                                                |

## Acknowledgments

Working on my thesis has been a fascinating and an extremely rewarding experience. As I bring a closure to my research over the past one year, I agree with Sir Isaac Newton in saying that I was able to see so far only because I was standing on the 'shoulders of giants'. While the whole year was full of challenges and long working hours, it has been enveloped with the support and guidance of many a people. The new learnings from each of them has enriched me both personally and professionally.

First and foremost, I would like to express my utmost gratitude towards my supervisors - Prof. Edoardo Charbon and Dr. R. Bogdan Staszewski for giving me a wonderful opportunity to work on an interesting topic. Prof. Charbon's experience and knowledge in 3D imaging added a great deal to my learning in the past one year. His strong vision always inspired me to achieve better and his continuous motivation boosted my confidence greatly. Under his guidance, I have learnt to be meticulous and have practical thinking in my work. Dr. Bogdan gave me an initial motivation to work on this project and it proved extremely valuable to my graduate experience. The brain-storming sessions with him have enhanced my creative side in work. His industry exposure added a perspective of competitiveness in the project and his advice on corporate life would surely help me in my career ahead. I am fortunate to have received such supervision and I can say that I have learnt to dream bigger.

I would like to thank Andre Borowski for his idea to build an ambitious 3D camera and his financial support over the last one year. It really helped me to focus better to reach the desired goals.

I am thankful to Dr. Nick van der Meijs for serving on my defence committee and giving me an opportunity to work as his teaching assistant. It was an enriching experience which showed me the other side of student world. I am also grateful to Prof. Kofi A. Makinwa for his career guidance at the time I needed the most; it instilled confidence in me to make good decisions.

I am grateful to Antoon Frehe and Atef Akhnoukh for their technical support. It eased my working with 65nm technology in the initial phase of thesis project. I am also thankful to Marion de Vleiger for her warm smile every morning and her help in the administrative issues.

I would like to acknowledge the contributions of Yuki Maruyama, HyungJune Yoon, Shingo Mandai and Chockalingam Veerappan in SPAD related work. The technical discussions with them helped a great deal in my circuit design. Thanks to Matthew Fishburn for patiently solving all my doubts and for his valuable comments on my thesis report.

I am also grateful to my colleagues in ELCA group - Wanghua, Senad, Vincent, Wannaya, Akshay and Yi for their encouragement over last twelve months and their help in smallest of issues. The humorous coffee time discussions with them always left me with more energy to work. A special thanks to all my friends especially Harsh, Shishir, Vishwas and Parag for supporting me during my M.Sc. study and for good memories that I will always cherish.

One person whom I cannot thank enough is my dearest friend - Gaurav. It would have been difficult to understand electronic design without those endless technical discussions. A source of strength and encouragement, he believed in me always. I really hope we can together achieve the best in life.

I am truly amazed by the patience and encouragement from my family during the past few years. To venture out far from one's own land is not easy; and I was able to do so only because of my wonderful parents. My heart-felt gratitude for all the sacrifices they made, their words of inspiration and their belief that I could excel. My study and stay in Netherlands would not have been possible without their continuous support. I extend the same thankfulness to my little brother, my elder sister and my brother-in-law for always being there for me and motivating me during my study at Delft. Also to my nephew, Aditya, who taught me how simple life can be. A special thanks to Skype and Google technologies for they allowed remaining in touch with the dear ones and reduced distances to a great extent.

Finally, I would dedicate my thesis to my both sets of grand-parents who touched my life in countless ways. I wish I could spend more time with them...

### Acronyms

2D Two Dimensional3D Three Dimensional

ADC Analog-to-Digital Converter

APD Avalanche Photo-diode CCD Charge Coupled Device

CMOS Complementary Metal Oxide Semiconductor

CW Continuous Wave

DCR Dark Count Rate

DNL Differential Non-linearity

DL Delay Line

DSM Deep Sub-micron

DFF D Flip-flop

DLL Delay Locked Loop

FWHM Full Width at Half Maximum

INL Integral Nonlinearity

LPI Local Passive Interpolation

PDP Photon Detection Probability

PMT Photon Multiplier Tube

PET Positron Emission Tomography

PVT Process, Voltage and Temperature

PLL Phase Locked Loop

ToA Time-of-Arrival

TCSPC Time Correlated Single Photon Counting

TDC Time-to-Digital Converter

TFF Toggle Flip-flop

ToF Time-of-Flight

TG Transmission Gate

SPSD Single Photon Synchronous Detection

SPAD Single Photon Avalanche Diode

VDL Vernier Delay Line

### 1. Introduction

The ability to reproduce and extend the natural senses has always fascinated mankind and it has arguably been the most important factor for development of sensors and related technologies. One of the growing areas of interest is that of 3D imaging which is gaining popularity for its ability to capture the objects as we see them in the real world. Although 3D imaging techniques have existed for several decades, it has been mostly restricted to research domain and low volume applications till recently. The recent advent of low-cost solid-state 2D imagers along with technological progress has propelled the idea to build low-cost and compact three-dimensional (3D) imaging systems. Such systems have increasing demand in varied domains ranging from face recognition to machine vision, from 3D gaming to nuclear security and from molecular imaging to land and sea surveying. The diverse scope of applications makes the field of 3D imaging even more challenging as every application has stringent requirements in terms of performance and cost.

#### 1.1 Applications of 3D Imaging

The applications for depth map acquisition and evaluation are widespread. A depth map is an image consisting of information pertaining to the distance of the objects in a scene from a certain viewpoint. A 3D imaging imager creates depth maps through range estimation of the contours on the object. The challenge is to build a very fine depth measurement system in order to detect the surface reliefs on the object. In this section, some of the main applications of 3D imaging are presented.

#### 1.1.1 MACHINE VISION

One of the important functions of an imager is related to enhanced vision. While 2D cameras existing in market boast of high resolution, they cannot capture depth information of an object. The depth information is desirable for machine vision in several domains, the most notable being the automotive industry where 3D vision can be employed for pedestrian detection, rear vision for parking assistance, lane departure warning and adaptive cruise control. However, such applications are very sensitive to robustness and cost of the solution and therefore, there has not yet been widespread adoption of 3D vision systems in automobile industry.

3D vision is also useful in robotics to assist in better maneuvering of autonomous robots. Conventionally, ground robots rely only on 2D sensors to estimate their position with respect to environment and avoid collisions. But, the use of 2D sensors restricts the field of view to a single plane parallel to the floor. To enhance robot vision systems, multiple sensors need to be integrated to produce denser data. With use of 3D imaging, the process of depth map creation, self-localization and collision avoidance can be made more accurate [1]. Moreover, solid-state 3D imagers provide wide field of view along with compactness, speed and low power consumption, making it perfectly suitable for autonomous robots.

#### 1.1.2 SECURITY

One of the main advantages of 3D imagers in security is their ability to perform in dim-lit environment. Enhanced vision is desirable in security or surveillance applications for physical access control in homes, banks or production plants, border control surveillance, baggage checks at airports and e-passport programs. At present, CCTV cameras are generally employed for surveillance activities. A 3D camera adds value to the existing system by giving depth information to estimate the exact position of objects in focus. Similarly, 3D face recognition systems can boost the security in access control applications.

#### 1.1.3 Human-Computer Interaction

Advancements in 3D vision can lead to better experience in the human-computer interaction domain. The existing solid-state 3D sensors are capable of creating real-time depth maps and multiple functionalities can be built upon them to boost the user experience in consumer applications. Recognizing user gestures in gaming, virtual keyboards, mouse, and interactive home entertainment devices are some of the applications that can benefit from low-cost 3D imagers.

#### 1.1.4 BIOMEDICAL IMAGING

A number of medical applications based on time-resolved optical imaging have benefited from 3D imaging. In particular, sub-nanosecond timing resolution along with high sensitivity is useful for specific applications such as positron emission tomography (PET), fluorescence lifetime imaging microscopy (FLIM) and fluorescence correlation spectroscopy (FCS).

While the above discussed applications show the present scope of 3D imaging, the possible applications for 3D imaging will only grow with availability of low-cost solutions.

#### 1.2 3D Imaging Techniques

#### 1.2.1 GENERAL CLASSIFICATION OF OPTICAL 3D IMAGE SENSORS

The range-finding and acquisition of 3D images is enabled by different optical techniques. Various authors have presented several classifications based on the different physical principles involved. Besl [2] identifies six basic optical techniques which are shortly described below:

#### Triangulation

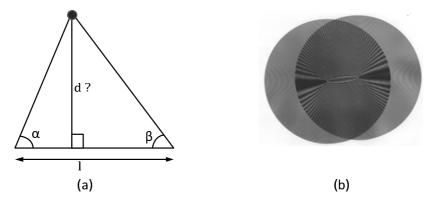

It is the oldest technique for measuring distance to a point in the scene. It determines the location of a point by measuring angles to it from two known points on either end of a known baseline. The point on the object is fixed as the third point of a triangle with one known side and two known angles (see Figure 1.1a). Nearly all animals obtain 3D information based on triangulation technique and it has been widely used in applications related to mobile robotics, navigation, surveying and 3D photography. The disadvantages of

this technique are that its measurement range is limited to millimeter range only and it has high dependency on the source of illumination.

Figure 1.1 - (a) Triangulation method used to calculate coordinates and distance of a point from baseline; (b) Moiré pattern.

#### Moiré

This technique extracts shape of an object from the interference patterns. A Moiré pattern is a superimposed image of highly regular interference patterns which differ in relative angle, size or spacing. An example of such a pattern is shown in Figure 1.1b. This method is well known for applications which need high resolution for smooth surfaces [1] but qualifies for limited dynamic range applications only.

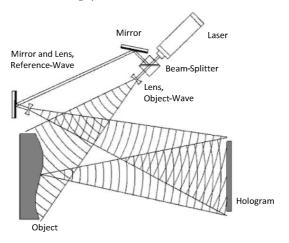

#### Holographic Interferometry

This technique has the ability to measure displacements in the order of a wavelength of light or better. Thus, it provides highest absolute accuracy and resolution. The setup, as shown in Figure 1.2, includes coherent light from laser sources which produces interference patterns due to phase-frequency differences in different optical paths [3], [4]. This produces two slightly different scenes with minute differences between them. It is a powerful scheme and is widely used in identification of vibrational modes, surface displacements, and motion geometries. Nevertheless, this technique is only suitable for short range applications (in the order of micrometres to millimeter range).

Figure 1.2 - Basic holographic setup [3].

#### **Focusing**

Various techniques exist in the literature for this approach to 3D imaging [5]. All of them share the basic concept of optical physics of imaging: the distance from the optical centre of the lens to a path on 3D scene is related to the degree of sharpness or blurring of the corresponding components of the image [2].

#### Fresnel Diffraction

It refers to the modification in the direction and intensity of a group of waves after passing by a slit or through an aperture whose size is of the order of the wavelength of the waves [2], [6].

#### Radar or Time-of-Flight

Acronym for 'Radio detection and ranging', this technique dates back to early 1900s when Christian Hülsmeyer first experimented with radio waves to detect the presence of ships in dense fog conditions. The underlying principle of radar based imaging is to measure the time elapsed between an emitted pulse of light and its reflected pulse from the object. It is suitable for objects at large distances, in the range of kilometres depending upon the wavelength used. The basic range equation for radars is:

$$\mathbf{v} \cdot \mathbf{\tau} = 2 \cdot \mathbf{d} \tag{1.1}$$

where 'v' s the velocity of signal propagation, 't' is the transit time taken for the pulse to hit the object and return and 'd' is the distance to the object. This technique is also known as Time-of-Flight (ToF).

Apart from [2], several other classifications of optical 3D image sensors exist in the literature. In [5], Jarvis classifies the range sensing methodology in three sets:

- (a) active vs. passive based on illumination technique e.g. ambient lighting or structured laser source;

- (b) image based vs. direct based on if image analysis is done for range extraction;

- (c) monocular vs. multiple view based on if single or multiple viewpoints are considered for range determination.

Originally, 3D imaging systems were based on non-solid-state devices. However in recent times, design of 3D imagers has significantly evolved due to the advances made in IC technology. Solid-state implementation of imagers allows low system cost, high lateral and depth resolution, short acquisition time, insensitivity to mechanical stress along with fast image processing. A discussion is made in the next section about the state-of-the-art solid-state ToF 3D imagers.

#### 1.2.2 SOLID-STATE TIME-OF-FLIGHT IMAGERS

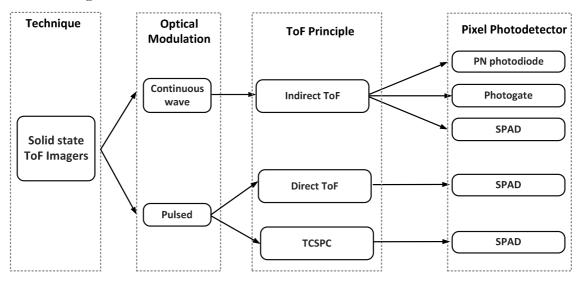

Much work has been carried out in the field of solid-state ToF 3D imagers [7], [8]. To analyze these contributions to the art, it is often useful to classify the existing work in ToF imagers as a function of (i) the type of laser modulation, (ii) the ToF principle, and (iii) the nature of

photo-detection. Although a mix of techniques is possible, a simple classification is made and is shown in Figure 1.3.

Figure 1.3 - Classification of state-of-the-art solid-state optical ToF image sensors [1][9].

#### 1.2.2.1 Laser Modulation Techniques

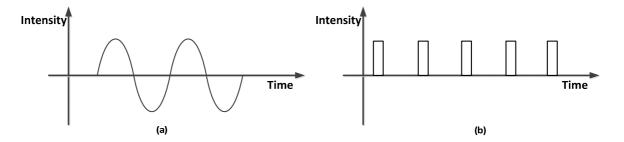

The two common modulation techniques used in ToF image sensors are continuous wave (CW) modulation methods and pulsed modulation methods. Both modulation schemes require dedicated detector architecture, measurement logic and an evaluation scheme.

In CW modulation technique (also known as 'lock-in'), the modulation signal is a periodic optical signal, typically a sine wave [9], [10] whereas in the pulsed modulation technique, the modulation signal is a sequence of pulses. A third modulation technique called 'Pseudo noise modulation' is described in [9] and is very robust in nature. Here, the modulation signal is a coded sequence of pulses and can be used to avoid interference between pulses from different 3D cameras.

Figure 1.4 - Laser modulation techniques: (a) continuous wave modulation; (b) pulsed modulation.

#### 1.2.2.2 ToF Measurement Principles:

The measurement principle defines the basic scheme and setup for ToF estimation. The main techniques used for ToF measurement are:

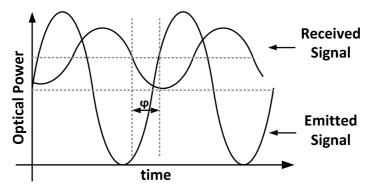

#### Indirect ToF:

It refers to the comparison of *phase* of the emitted modulating signal and the detected modulated signal. The range is measured by calculating the phase shift of the first harmonic in the returned wave and is estimated by:

$$z = \frac{c}{4\pi f} \phi \tag{1.2}$$

where  $\varphi$  is the phase shift due to time of flight and f is the modulation frequency.

Figure 1.5 - Range estimation through phase measurement [9].

The first implementation of lock-in photo-gate structure based on phase shift measurement was reported in [11], [12]. The traditional indirect ToF methods are analog in nature. They are also vulnerable to uncorrelated background illumination. A digital approach to phase detection, called 'single photon synchronous detection' (SPSD) was proposed in [13]. It achieves enhanced phase accuracy compared to analog approaches but suffers from harmonic distortion in the illumination system.

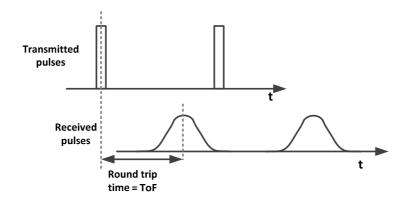

#### Direct ToF:

As the name suggests, it refers to the direct ToF measurement of optical *pulses* sent by a light source. The range is determined by time measurement between emitted and received pulse and is given by:

$$z = c \cdot \frac{t_{\text{TOF}}}{2} \tag{1.3}$$

where c is the speed of light and  $t_{ToF}$  is the time interval between emitted pulse and received photon.

The illumination sources required by direct ToF need to have extremely fast rise and fall times. Additionally, very fast photodetectors and front end circuits are required to detect precise optical pulses. For instance, if a single-shot distance resolution of 1 mm (~3 ps) is needed to be measured, a clock frequency of ~150 GHz is required for the counter to measure ToF. This is a very tough requirement to meet and is close to impossible in the existing technology nodes. This principle also suffers from high sensitivity to background light when single shot measurements are required [1]. A solid-state 3D image sensor that works on direct ToF principle is reported in [14].

Figure 1.6 - Range estimation through time interval measurement.

#### Time Correlated Single Photon Counting (TCSPC)

One of the concepts in 3D imaging is based on correlation of time-of-arrival (ToA) of incident photons [1]. It is a pulsed based scheme specific to the detection of single photons and correlation of their ToA to obtain the distance information.

In this scheme, generally, multiple single-photon measurements are obtained and high resolution can be achieved with statistical processing. This helps to realize millimeter level accuracy even at low photon counts or in the presence of large background illumination [15].

TCSPC is useful for a variety of applications such as measuring the lifetime of a fluorescent marker while studying a biological specimen or for understanding the metabolic activity in positron emission tomography (PET). Apart from this, this approach finds various other applications such as optical range-finding [15], fluorescence correlation spectroscopy (FCS) [16], Förster resonance energy transfer (FRET) [17], and fluorescence lifetime imaging microscopy (FLIM) [18].

The work presented in this thesis extends the art in TCSPC applications. The proposed 3D imager is aimed at security and surveillance applications and the system objectives can be met using TCSPC approach to design. The system is required to be sensitive to wavelengths in non-visible range and must work for low photon counts or dim lit areas with high resolution at low power. The next chapter discusses the building blocks of TCSPC based 3D imagers.

#### 1.3 Imager Performance Parameters

To evaluate the performance of state-of-the-art 3D imagers, it is important to understand the different performance parameters. Following is a brief description of the primary performance parameters.

#### 1.3.1 RANGE $(Z_{MAX})$

It is the maximum range that the imager can capture an image from. This may vary from few millimetres to hundreds of meters depending upon the application. For instance, in surveillance activities at airport or shopping malls, large range is desirable to capture movement of people at distances as large as 20-30 m.

#### 1.3.2 Depth Resolution ( $\Delta Z$ )

Also known as "step-size", it is the smallest change in depth that the sensor can measure. In face recognition systems, a fine depth resolution is required for identification of facial contours. In modern imaging systems, the resolution may be of the order of micrometres to millimetres.

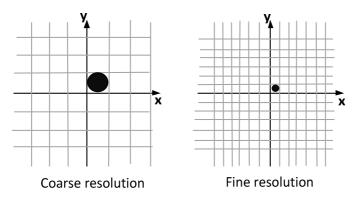

#### 1.3.3 Lateral Resolution $(N_x \times N_y)$

This parameter is a measure of density of information points in a unit area. In a colour 2D camera, the information in each point is the colour and brightness while in a 3D camera, it is the depth resolution of the device.

In consumer applications, this is also known as dots per inch (DPI). A 100x100 pixel image printed on a 1-inch square sheet is said to have 100 DPI. Good quality photographs usually require 300 dots per inch or higher when printed.

Figure 1.7 - Graphical representation of resolution [19].

#### 1.3.4 FIELD OF VIEW

It refers to the linear or angular extent of the scene of interest that can be seen by the imager at a particular position and orientation in space [Source: Wikipedia].

#### 1.3.5 FILL FACTOR

Fill factor in the context of imaging arrays is defined as the ratio of the photo-sensitive or active area to the total array area. Ideally, a 100% fill factor is desirable to avoid any information loss. However, high image acquisition rate mandates additional circuitry in the array which lowers the fill factor of an imaging array. Techniques such as back-side illumination allow 100% fill factor with photo-sensor and additional circuitry on different sides of wafer. But it involves a high manufacturing cost.

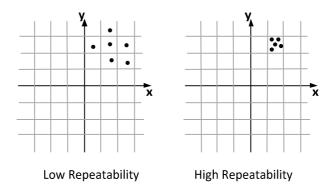

#### 1.3.6 REPEATABILITY

It refers to statistical variations when a sensor makes repeated measurements of the exact same distance under identical conditions. It indicates the reliability of the sensor and Figure 1.8 shows the basic concept of repeatability.

Figure 1.8 - Graphical representation of accuracy and repeatability [19].

#### 1.3.7 FRAME RATE (N FPS)

The rate at which the moving target is captured and an image is formed is referred to as the frame rate. In other words, it is the number of images or frames that can be produced per second.

Human eye can typically resolve 24 frames per second and any higher frame rate makes the motion appear more fluid to the human eye. The typical video frame rate is 30 fps and higher frame rates are desired for real time applications such as steering a guided missile, surveillance/security systems and biomedical imaging. Gaming industry is also increasingly demanding higher frame rates for high end action games such as Star Wars: Battlefront, FIFA and QUAKE. Frame rate in an imaging sensor is determined principally by the number of pixels and the pixel readout speed through an IO pad. If the number of pixels is greater, the image produced is finer but it leads to lower frame rate. On the other hand, if the pixel readout rate decreases, frame rate is decreased as well.

#### 1.3.8 CONSTRAINTS:

The above described concepts describe the performance of the imager. However, it is also important to consider the constraints presented by an application. The design of 3D imaging systems can drastically vary if the constraints are altered. The common constraints for imaging systems are:

#### Cost

Low-cost is always desirable in consumer applications for higher profitability. With CMOS technology, higher level of integration is possible and mass production leads to low-cost systems.

#### Size

This parameter directly implies the area occupied by the system. Although size is less significant in some applications such as cars or space-vehicles, it is a bottleneck in handheld devices and digital cameras. Thus, a highly compact imager with varied features is the goal of any low-cost imager.

#### Robustness

The ability of the system to work at desired performance in spite of undesirable magnetic fields, radiation, electro-magnetic interference, external vibrations or mechanical stress defines the robustness of the system.

#### Eye - safety

Some 3D imaging techniques require structured lighting in the form of lasers. The human eye is extremely sensitive to laser radiation and it is of extreme importance to cater to safety requirements.

#### 1.4 Motivation

The above discussion on the different performance parameters of 3D imagers helps to evaluate the performance of 3D imagers. In this section, the motivation to work on a ToF based 3D real-time imager is presented. The challenges faced during the execution of the project are also stated.

The CCD image sensors are a mature technology producing high quality images. But their high cost and low level of integration encourages the imaging industry to venture into CMOS based solutions. CMOS technology is cost-effective and allows the photodetector such as APDs or SPADs to be fabricated on a single chip along with imaging logic circuitry such as TDCs. Moreover, lithography and process control in CMOS fabrication have reached levels that allows CMOS sensor image quality to be comparable to that of CCDs.

The latest SPAD-TDC array reported in the literature uses 130 nm CMOS [8]. Although 90 nm SPADs had been developed, a SPAD-TDC imaging array in this technology does not exist in the literature till date. The state-of-the-art image sensors are summarized in Table 1.1.

In this thesis, an investigation of a 65 nm implementation of SPAD-TDC pixel array is carried out which is first of its kind. The small CMOS feature size allows better TDC resolution and therefore, a higher depth resolution. This also leads to a higher speed of image acquisition. Since CMOS dimensions are small, higher fill factor is possible. Furthermore, it leads to lower power consumption due to smaller supply voltage. However, design in deep submicron technology presents challenges in terms of parasitic dominance, performance degradation due to process variations and other related issues.

In this thesis, the challenge is to build a 3D imager specific to security applications. The goal of this work is to lay the ground-work for building a 1 Mpixel 3D real-time camera in 65 nm CMOS technology with less than 3 mm depth resolution. However, a 32x32 prototype is first implemented as a proof of concept and to verify the correctness of the proposed imager architecture.

Phase domain

$\Delta\Sigma$  approach

3.17%

2011

Ring

Oscillator

1%

2011

[20] [21] [22] [7][8] **Technology**  $0.13 \mu$ 0.13 μ  $0.35~\mu$  $0.18 \mu$ 0.13 μ **Array Size** 60x48340x96128x9632x32160x12815m (100 ns)  $45 \mathrm{m}$ Range 5m128m8m (55 ns) 38 mm (1σ 160 mm (1σ Resolution < 20 mm < 32 mm < 8.5 mmdistance distance resolution) resolution) Time Jitter 185 ps140 ps at FWHM Frame Rate 10 25k (raw) 20 (fps) Median Dark  $245~\mathrm{Hz}$ Below 50 Hz Below 100 Hz Count Rate DNL / INL INL: 110 mm INL: 5 mm  $\pm 0.4/\pm 0.2$ -0.52/0.73 $\pm 0.3/\pm 2$ (LSB) upto 2.4m upto 2.4 mm 94 mWChip power 35 mW550 mW40 mWdissipation (78 mA)Chip area  $6.5 \times 5.5 \text{ mm}^2$  $3.3 \times 3.3 \text{ mm}^2$  $11 \times 2.3 \text{ mm}^2$  $7.2 \times 7.5 \text{ mm}^2$ Pixel pitch 85 μ 85 μ 50 μ  $44.65 \mu$

Table 1.1 - State-of-the-art in 3D TCSPC (SPAD) imaging. The shaded cell indicates the best result of the summary for a given parameter.

# 1.5 Design Methodology

Phase domain

approach

0.5%

2009

Type of

TDC used

Fill factor

Year

A top-down design methodology was undertaken to realize the prototype. At first, an extensive literature survey of the existing work on TCSPC 3D imagers was carried out along with system analysis to understand the working and requirements of the system. The understanding gained from the study was used to draw out the overall system architecture, its different blocks, their functionality and the desired specifications. During this process, multiple new concepts were also incorporated to increase the efficiency of the system.

Flash TDC

70% (macrocells)

2011

Coarse-fine

2009

The system analysis was followed by circuit level implementation of the system. A bottom-up approach was employed in the circuit design in 65 nm technology. Each of the blocks identified in system level analysis was independently designed to meet the required specification. To achieve the desired performance after layout was one of the biggest challenges of the work. It required multiple iterations between circuit design and layout before the desired specifications could be realized.

The circuit and layout of the pixel was followed by integration at the system level. A modular approach to constructing a 2D array was chosen. The system level blocks were then integrated with the pixel array to realize the full implementation. At each step of circuit and layout design, the performance was verified against the desired system specifications. This

approach finally led to a successful design of the prototype which meets the desired system requirements.

# 1.6 Organization

The organization of the thesis report is along similar lines as the design methodology.

Chapter 2 explains the working of a SPAD photodetector and the conventional methods to build its front-end circuitry. It also describes the state-of-the-art TDC architectures and explains the choice of TDC architecture for a million pixel array.

Chapter 3 draws out the system specifications for a ToF-based 3D real-time camera. It also discusses the architecture of the imaging array and determines the required circuit performance.

Chapter 4 focuses on the design process of a single pixel with respect to desired system specifications. It also discusses the implementation issues at pixel as well as system level. Finally, the layout of the whole system is presented.

Chapter 5 demonstrates the design and post-layout simulation results obtained.

Chapter 6 concludes this dissertation providing the summary of the work done along with the contributions to the state of the art and its future scope.

# 2. Background

In this chapter, the background of the basic building blocks of a TCSPC SPAD based 3D imager is presented. A detailed discussion of imager architecture and pixel design is made in Chapter 3 and Chapter 4.

This chapter is organized as follows: Section 2.1 gives an introduction to the basic architecture of imager architecture. Section 2.2 describes the working of SPAD and how its front-end circuit is typically designed in the literature. Section 2.3 surveys various TDC architectures and discusses the choice of suitable TDC for a 3D imager.

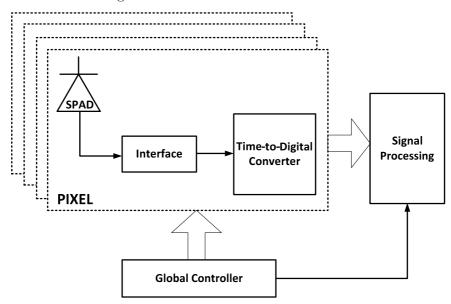

## 2.1 Generic TCSPC Imager Architecture

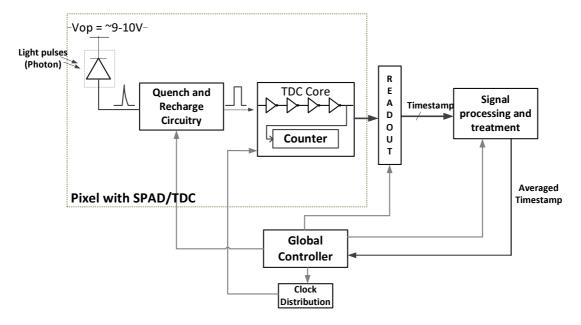

A TCSPC approach to 3D imaging involves statistical processing on the collection of a large number of measurements. Such processing helps to achieve picosecond level time resolution. Although the traditional photomultiplier tubes and multi-channel plates are capable of high time resolution, they are relatively bulky and costly. Single photon avalanche diodes in a multi-pixel array are increasingly being adopted for their small cost and comparable performance. Along with a SPAD, a TDC with picosecond resolution is employed for time interval measurement and thus, the structure allows for high-speed image acquisition.

The block diagram in Figure 2.1 shows the basic architecture of a SPAD based TCSPC 3D imager. Each pixel consists of a photo-detector along with its front-end circuitry. In order to measure the time-of-flight (ToF) of photons hitting the imager, a time-to-digital converter is employed in every pixel. The pixel receives inputs from the global controller w.r.t. better control of interface circuitry and its readout. The data readout from the pixel undergoes signal treatment for final image reconstruction.

Figure 2.1 - Block diagram of SPAD based TCSPC 3D imager.

# 2.2 Single Photon Avalanche Diode

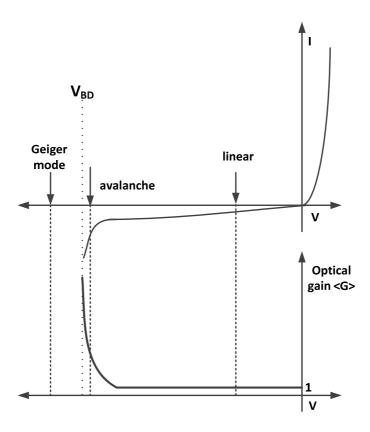

One of the integral blocks of any imager is a photodetector. In this work, a single-photon avalanche diode (SPAD) has been employed. A SPAD is a p-n junction diode biased above breakdown voltage V<sub>BD</sub>, commonly known as operating in *Geiger mode*. When biased in this mode, a high electric field exists within the junction. If a photon hits the semiconductor surface and is absorbed in the diode's depletion region, it may trigger an avalanche producing electron-hole pairs by impact ionization which discharge the depletion region capacitance rapidly [10].

Figure 2.2 - I-V characteristic and gain of SPAD in Geiger mode of operation [23].

SPADs offer a near-infinite gain as compared to the linear gain avalanche photo-diodes (APDs), as shown in Figure 2.2. Furthermore, SPADs have shown to achieve picosecond level resolution [24]. Thus, SPAD acts like a trigger device for a single photon producing a sharp current pulse on being hit by a photon. This current pulse can be measured to determine the exact arrival time of photon in TCSPC applications.

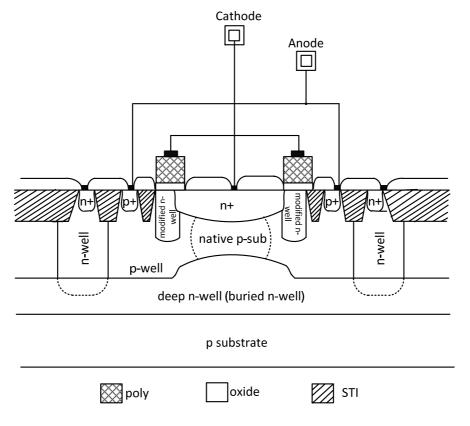

## 2.2.1 DEVICE STRUCTURE

The device structure used for building 65 nm SPADs is shown in Figure 2.3 [25]. The avalanche occurs in the depletion region on the edge of n+ layer and native p-substrate junction. It consists of a guard ring which helps to reduce electric field at the edges. The guard ring is built with low concentration n-well and helps to prevent edge breakdown. The

native p-substrate has low concentration allowing larger depletion width; thereby allowing higher sensitivity to longer wavelengths.

Figure 2.3 - Device structure of SPAD [25].

#### 2.2.2 SPAD PERFORMANCE PARAMETERS

To analyse the operation of SPAD and its interface, it is important to understand its performance determining factors. Few of the performance factors are influenced by excess bias voltage of SPAD ( $V_E$ ) which is the difference between the operating bias of SPAD  $V_{OP}$  and the breakdown voltage  $V_{BD}$ . Following is a brief discussion of the major influencing factors:

### Dark Count Rate (DCR)

Dark counts refer to the triggering of an avalanche by secondary carriers in the absence of illumination. These carriers produced through tunnelling or thermal generation effects can be captured in traps and their random release leads to avalanche current pulses unrelated to a photon event. Such dark counts have a Poissonian distribution and can be seen as a noise source of the device [26].

In Geiger mode, these spurious pulses cannot be distinguished from regular photon triggered pulses and are produced at a mean frequency known as DCR. The SPAD DCR increases with higher  $V_E$  because of two effects: (a) an increase in avalanche triggering probability and (b) higher emission rate from generation centers due to larger field. DCR is strongly dependent on temperature and defines the minimum detectable signal, thereby limiting the dynamic range of the imager.

## Photon Detection Probability (PDP)

PDP refers to the probability of a photon being absorbed in the detector active area to generate an electron-hole pair capable of triggering an avalanche. The probability of photon detection depends on diode's quantum efficiency as well as the excess bias voltage  $V_E$ . PDP increases with higher  $V_E$  since a higher electric field increases the sensitivity and thus its triggering probability. Usual values for PDP in CMOS SPADs are in the range of 1% to 30% [10][27].

## SPAD Timing Jitter

It refers to the statistical fluctuation of the time interval between photon arrival at the sensor and pulse generation by the interface circuitry. Also known as timing resolution of SPAD, it improves with increasing  $V_E$ . At higher  $V_E$ , the depletion width is greater and thus, only photons of longer wavelengths can be absorbed, giving a sharper timing jitter pulse. At smaller  $V_E$ , saturation occurs giving a large timing jitter.

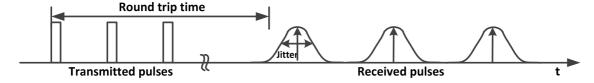

Figure 2.4 - Transmitted and received pulses [28].

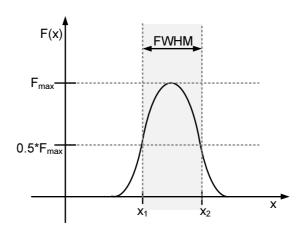

SPAD jitter is typically expressed at full width half maximum (FWHM) as shown in Figure 2.5. FWHM is a common expression in signal processing to define bandwidth and describes the extent of a function. It is given by the difference between two extreme values of the independent variable at which the dependent variable is equal to half of its maximum value.

Figure 2.5 - Full width at half maximum.

#### Afterpulsing

During a photon triggered avalanche, some carriers can be captured by deep levels in the junction depletion layer and be released at a later arbitrary time. These released carriers can retrigger the avalanche, generating false current pulses correlated with the previous

avalanche pulse. Such an after-effect is termed as afterpulsing and denotes the spurious pulses related to previous photon events.

The number of carriers captured by deep levels during an avalanche pulse depends on the trap concentration and the total number of carriers generated during a Geiger pulse i.e. the total charge of the pulse. Longer is the quenching time of avalanche current, higher is the total charge in the pulse and therefore, higher is the afterpulsing effects. To sum, afterpulsing increases with reducing quenching time or with higher avalanche current intensity.

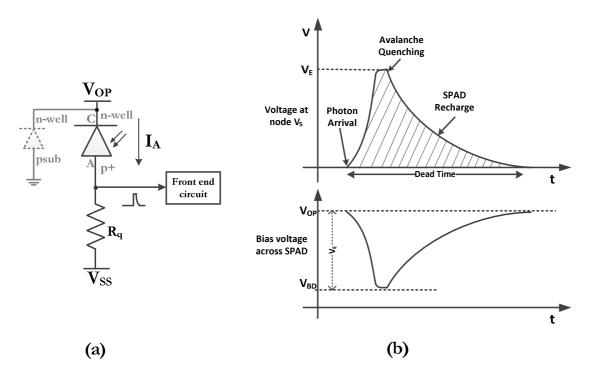

#### Dead time

After the onset of avalanche in SPAD device, the avalanche current needs to be controlled and the SPAD needs to be restored to its Geiger mode operating bias in order to detect subsequent photon arrival. The time required to quench the avalanche and recharge the diode upto 90% of its excess bias is defined as the dead time of SPAD [10]. Dead time should be as small as possible as it limits the rate of detection of photons, thus restricting the acquisition rate or imager. However, a small dead-time implies larger afterpulsing and therefore, a trade-off exists.

#### Cross-talk in SPAD farms

Cross-talk in SPAD farms can be both electrical and optical in nature. Electrical cross-talk occurs when photon absorbed in the substrate generates carriers which diffuse laterally in adjacent pixels and trigger avalanche. The mean penetration depth of photons depends strongly on the photon wavelength and therefore, photons in red and infrared ranges induce more electrical cross-talk than short wavelength photons [1]. However, electrical cross-talk can be eliminated by proper SPAD device design techniques.

Optical cross-talk refers to trigger of spurious avalanche current in the neighbouring SPADs. This is due to electroluminescence effect [10] where secondary photons can be emitted and absorbed by the nearby pixels in an array of SPADs. Optical isolation may be employed among the SPAD devices to reduce such an effect.

Optical cross-talk can be estimated by measuring the signal correlation between two adjacent pixels while electrical cross-talk needs sophisticated optical testing.

## 2.2.3 SPAD READOUT

Once the photon hit creates an avalanche effect in the SPAD device, its front-end circuitry has the following tasks:

- i. **Sensing:** The photon absorption indicates an event occurrence which needs to be propagated to time interval measurement circuitry.

- ii. **Quenching:** When avalanche occurs, it needs to be halted to avoid large flow of current.

- iii. **Recharge:** The SPAD needs to be recharged so that it is biased in Geiger mode and can detect a photon again.

#### 2.2.3.1 Sensing

The signal generated at the anode of SPAD needs to be sensed and propagated to the processing circuitry. Typically, an inverter is employed to capture the SPAD signal. However, different circuit topologies may be applied depending upon the signal amplitude of SPAD. A detailed discussion is made in Chapter 4.

## 2.2.3.2 Quenching

Quenching is the process of halting SPAD's avalanche breakdown effect. Different techniques have been proposed in the literature and fast quenching is preferred to avoid self-heating, trapping and optical cross-talk [29]. There are two approaches to quenching - passive and active, as described below.

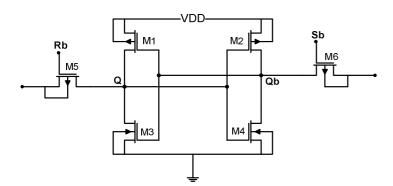

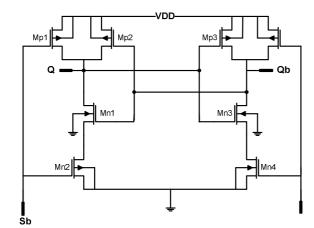

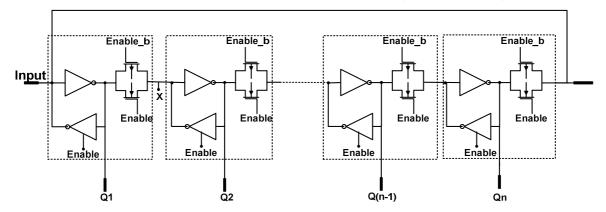

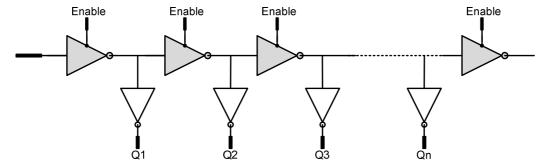

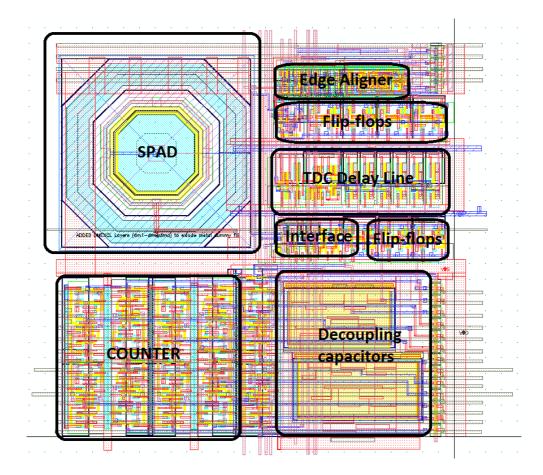

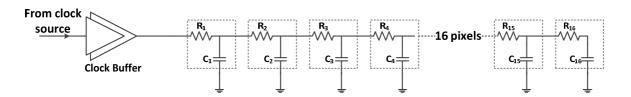

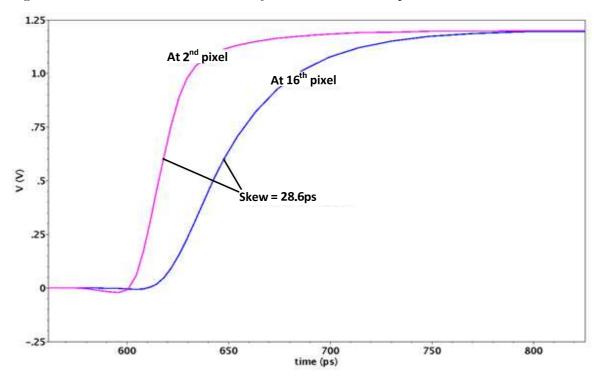

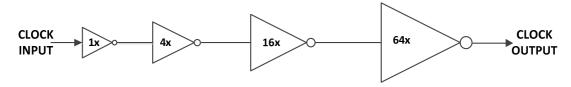

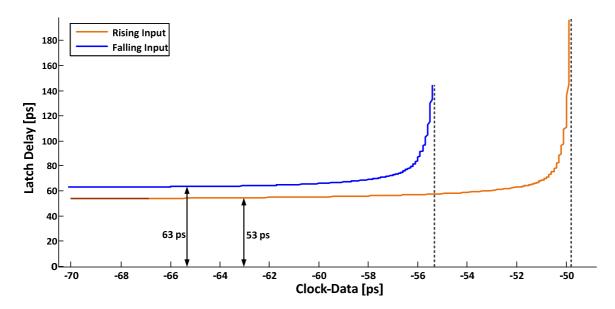

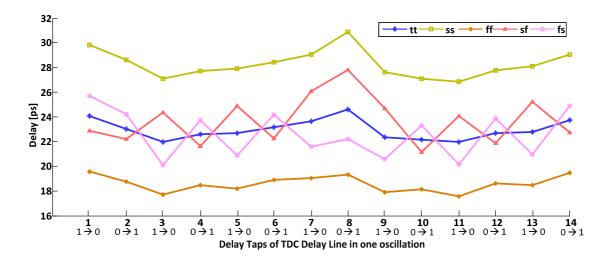

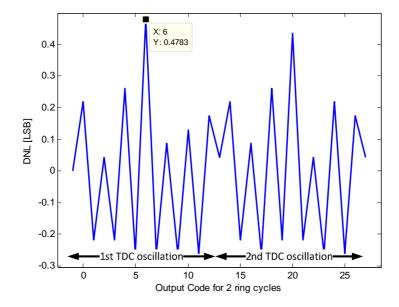

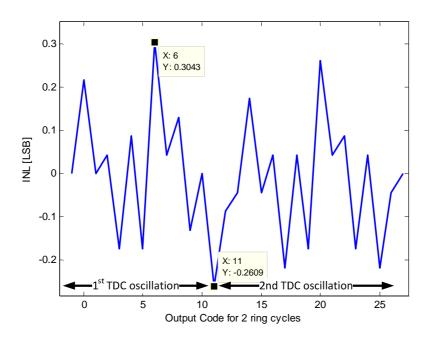

## Passive Quenching (PQ)