US008766719B2

### (12) United States Patent

### Lai et al.

### (54) DIGITALLY-CONTROLLED POWER AMPLIFIER WITH BANDPASS FILTERING/TRANSIENT WAVEFORM CONTROL AND RELATED DIGITALLY-CONTROLLED POWER AMPLIFIER CELL

- (75) Inventors: Jie-Wei Lai, Taipei (TW);

Meng-Hsiung Hung, Hsinchu (TW);

Robert Bogdan Staszewski, Delft (NL)

- (73) Assignee: Mediatek Inc., Science-Based Industrial Park, Hsin-Chu (TW)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 69 days.

- (21) Appl. No.: 13/484,268

- (22) Filed: May 30, 2012

### (65) Prior Publication Data

US 2013/0094611 A1 Apr. 18, 2013

### **Related U.S. Application Data**

- (60) Provisional application No. 61/548,095, filed on Oct. 17, 2011.

- (51) Int. Cl. *H03F 1/00* (2006.01)

(52) U.S. Cl.

### (56) References Cited

### U.S. PATENT DOCUMENTS

| 7,149,271 | B2   | 12/2006 | Yamada           |         |

|-----------|------|---------|------------------|---------|

| 7,759,992 | B2   | 7/2010  | Ibuka            |         |

| 7,929,637 | B2 * | 4/2011  | Staszewski et al | 375/295 |

## (10) Patent No.: US 8,766,719 B2

### (45) **Date of Patent:** Jul. 1, 2014

| 8,004,368    | B2 * | 8/2011  | Presti et al 330/10      |

|--------------|------|---------|--------------------------|

| 8,319,530    | B2   | 11/2012 | Zhao                     |

| 8,411,793    | B2 * | 4/2013  | Staszewski et al 375/297 |

| 2002/0030529 | A1   | 3/2002  | Lee                      |

| 2003/0042984 | A1   | 3/2003  | Moloudi                  |

| 2011/0200076 | A1   | 8/2011  | Mu                       |

| 2011/0276113 | Al   | 11/2011 | Cybulski                 |

### OTHER PUBLICATIONS

Lai, A World-Band Triple-Mode 802.11a/b/g SOC in 130-nm CMOS, pp. 2911-2921, vol. 44, No. 11, IEEE Journal of Solid-State Circuits, Nov. 2009.

Mehta, A 0.8mm2 All-Digital SAW-Less Polar Transmitter in 65nm EDGE SoC, pp. 58-59 and a page showing Figure 3.2.7, ISSCC 2010/ Session 3/ Cellular Techniques/ 3.2.

Jerng, A Wideband Delta-Sigma Digital-RF Modulator for High Data Rate Transmitters, pp. 1710-1722, vol. 42, No. 8, IEEE Journal of Solid-State Circuits, Aug. 2007.

Chowdhury, A 2.4GHz Mixed-Signal Polar Power Amplifier with Low-Power Integrated Filtering in 65nm CMOS, pp. 1-4, Custom Integrated Circuits Conference (CICC), 2010 IEEE.

Boos, A Fully Digital Multimode Polar Transmitter Employing 17b RF DAC in 3G Mode, pp. 376-377 and a page showing Figure 21.7.7, ISSCC 2011/ Session 21/ Cellular/ 21.7.

\* cited by examiner

Primary Examiner — Khanh V Nguyen

(74) Attorney, Agent, or Firm - Winston Hsu; Scott Margo

### (57) ABSTRACT

A digitally-controlled power amplifier (DPA) with bandpass filtering includes a radio-frequency (RF) clock input, an amplitude control word (ACW) input, and a plurality of DPA cells. The RF clock input is arranged for receiving an RF clock. The ACW input is arranged for receiving a digital ACW signal. The DPA cells are coupled to the RF clock and the digital ACW signal, wherein at least one of the DPA cells is gradually turned on and off in response to at least one bit of the digital ACW signal.

### 20 Claims, 22 Drawing Sheets

FIG. 1

FIG. 9

FIG. 13

FIG. 20

FIG. 22

FIG. 23

15

### DIGITALLY-CONTROLLED POWER **AMPLIFIER WITH BANDPASS** FILTERING/TRANSIENT WAVEFORM CONTROL AND RELATED **DIGITALLY-CONTROLLED POWER** AMPLIFIER CELL

### CROSS REFERENCE TO RELATED APPLICATIONS

This application claims the benefit of U.S. provisional application No. 61/548,095, filed on Oct. 17, 2011 and incorporated herein by reference.

### BACKGROUND

The disclosed embodiments of the present invention relate to power amplification, and more particularly, to a digitallycontrolled power amplifier with bandpass filtering/transient 20 waveform control and related digitally-controlled power amplifier cell.

A polar transmitter offers some advantages, such as a potential for reducing complexity and current consumption in the modulator path as well as eliminating the problem of 25 image rejection, thus the polar transmitter is more suitable for implementation in advanced complementary metal oxide semiconductor (CMOS) processing technologies. More specifically, the polar transmitter is a transmitting device that splits a complex baseband signal explicitly represented by an 30 amplitude-modulated (AM) contented component and a phase-modulated (PM) contented component, instead of an explicit in-phase component and a quadrature component. These two orthogonal components are then recombined into a radio-frequency (RF) output signal to be transmitted over 35 the air

An all-digital radio-frequency (RF) transmitter front-end circuit may be employed by the polar transmitter to enhance power efficiency, reduce the hardware cost and reduce the chip size. One conventional implementation of the all-digital 40 RF transmitter front-end circuit is a digitally-controlled power amplifier (DPA), acting as an RF digital-to-analog converter (RF-DAC). The DPA may include a plurality of DPA cells for combining the AM signal and the PM signal and delivering an integral signal having a desired RF carrier fre- 45 quency and a required power level. Therefore, how to arrange and control these DPA cells to achieve the desired DPA functionality is a significant concern in the pertinent field.

Regarding a conventional design of a DPA cell, a highefficiency switching-mode (inverse class-D/class-E) power 50 amplifier is employed. However, current switching-mode DPAs are inductor-loaded. Thus, due to the inherent characteristics of the inductor-loaded switching-mode amplifier, the voltage swing will be greater than  $\pi \times V_{DD}$ , where  $V_{DD}$  is the supply voltage. To reduce the voltage swing, a lower supply 55 voltage  $V_{DD}$  must be used. For example, a DC-DC converter and/or a low-dropout (LDO) regulator may be used to convert a high DC voltage provided by a battery into a low supply voltage  $V_{DD}$  needed by the DPA. Unfortunately, the battery efficiency would be degraded due to the power conversion.

Besides, the AM sampling using a periodic sampling clock would introduce out-of-band (OOB) noise/replica. One conventional solution to reduce the OOB noise/replica is to use a higher sampling rate. However, this would lead to larger power consumption. Another conventional solution is to use a 65 ture of a multi-stage digitally-controlled power amplifier higher digital-to-analog converter (DAC) resolution. However, this would have layout and physical limit. Yet another

conventional solution is to use an RF bandpass filter. However, such an RF bandpass filter has a low quality factor and consumes a large area.

Thus, there is also a need for an innovative DPA cell design which has improved efficiency and can effectively reduce the undesired OOB noise/replica.

Moreover, due to the feedback path established by magnetic coupling and/or direct coupling (e.g., coupling via the printed circuit board (PCB) ground and/or the package ground), the transmitter output may be fed back to a clock source in the transmitter, which may degrade the transmitter performance. Thus, there is also a need for a pulling mitigation mechanism employed to improve the transmitter performance.

### SUMMARY

In accordance with exemplary embodiments of the present invention, a digitally-controlled power amplifier with bandpass filtering/transient waveform control and related digitally-controlled power amplifier cell are proposed.

According to a first aspect of the present invention, an exemplary digitally-controlled power amplifier (DPA) with bandpass filtering is disclosed. The exemplary DPA includes a radio-frequency (RF) clock input, an amplitude control word (ACW) input, and a plurality of DPA cells. The RF clock input is arranged for receiving an RF clock. The ACW input is arranged for receiving a digital ACW signal. The DPA cells are coupled to the RF clock and the digital signal, wherein at least one of the DPA cells is gradually turned on and off in response to at least one bit of the digital signal.

According to a second aspect of the present invention, an exemplary digitally-controlled power amplifier (DPA) with transient waveform control is disclosed. The exemplary DPA includes a radio-frequency (RF) clock input, an amplitude control word (ACW) input, and a plurality of DPA cells. The RF clock input is arranged for receiving an RF clock. The ACW input is arranged for receiving a digital ACW signal. The DPA cells are coupled to the RF clock and the digital signal, wherein at least one of said DPA cells is abruptly turned on and off in response to at least one bit of said digital ACW signal.

According to a third aspect of the present invention, an exemplary digitally-controlled power amplifier (DPA) cell is disclosed. The exemplary DPA cell includes a controller and an output driver. The controller is arranged for generating a plurality of intermediate control signals according to a plurality of bias voltages, a radio-frequency (RF) input, and a bit of a digital amplitude control word (ACW) signal. The output driver is arranged for generating an RF output according to said intermediate control signals. The output driver includes a P-type block, having at least a P-type MOS transistor responsive to a first intermediate control signal of said intermediate control signals; and an N-type block, having at least an N-type MOS transistor responsive to a second intermediate control signal of said intermediate control signals.

These and other objectives of the present invention will no doubt become obvious to those of ordinary skill in the art after reading the following detailed description of the preferred embodiment that is illustrated in the various figures and draw-60 ings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

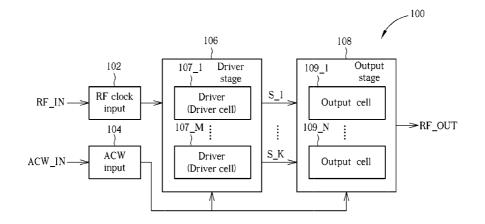

FIG. 1 is a block diagram illustrating a generalized struc-(DPA) according to an exemplary embodiment of the present invention.

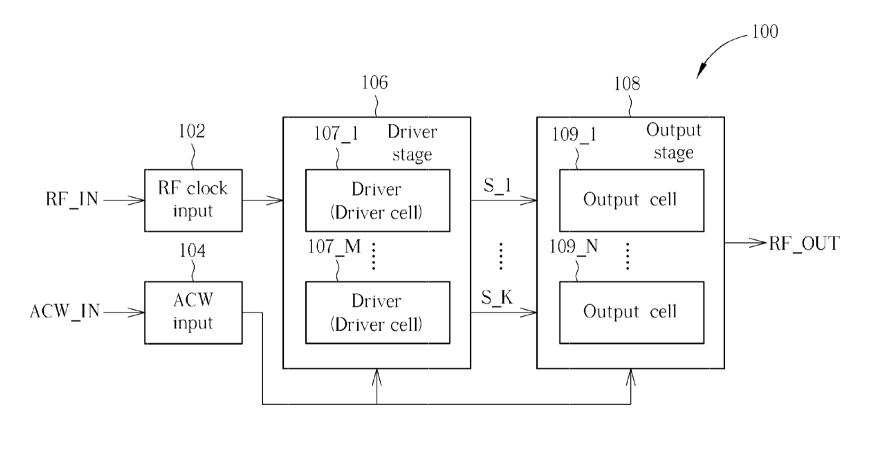

FIG. **2** is a diagram illustrating a first implementation of a multi-stage DPA according to an embodiment of the present invention.

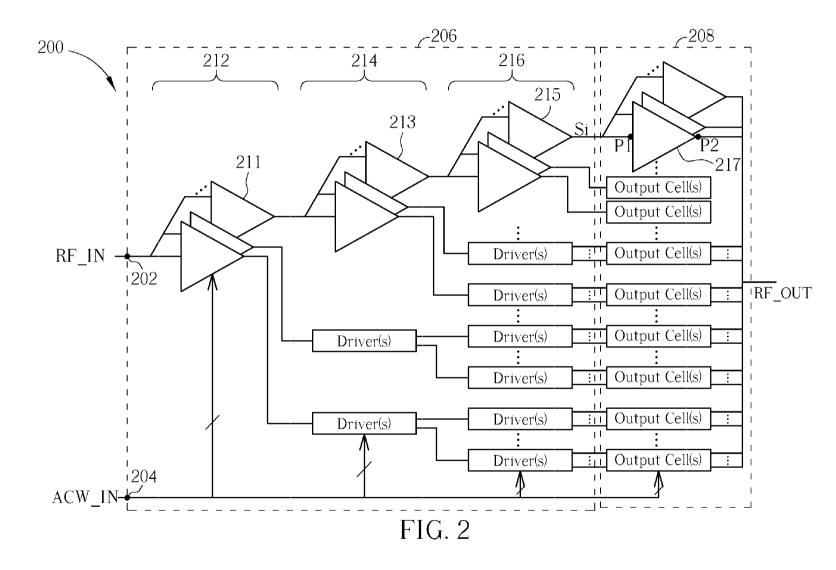

FIG. **3** is a diagram illustrating a second implementation of a multi-stage DPA according to an embodiment of the present 5 invention.

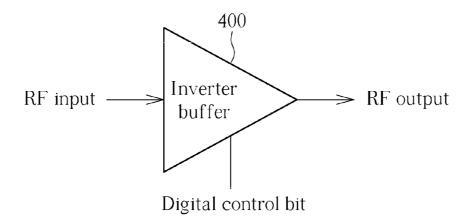

FIG. **4** is a diagram illustrating an inverter buffer according to an embodiment of the present invention.

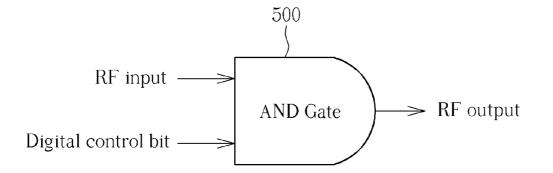

FIG. **5** is a diagram illustrating an AND gate according to an embodiment of the present invention.

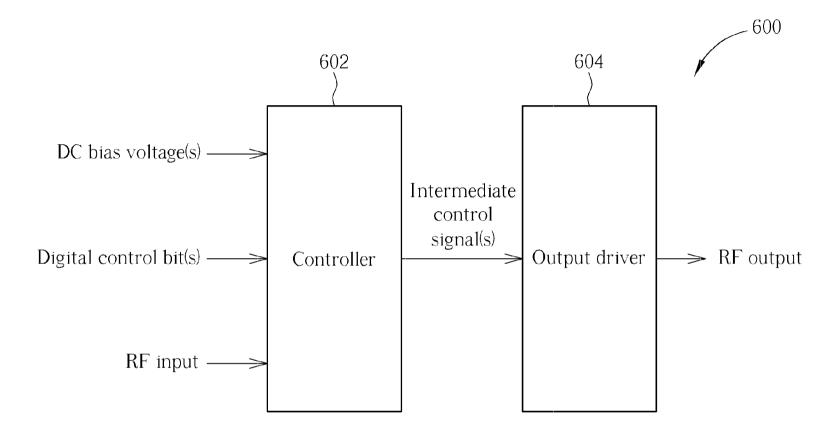

FIG. **6** is a diagram illustrating an output cell employed in an output stage of a multi-stage DPA according to an exemplary embodiment of the present invention.

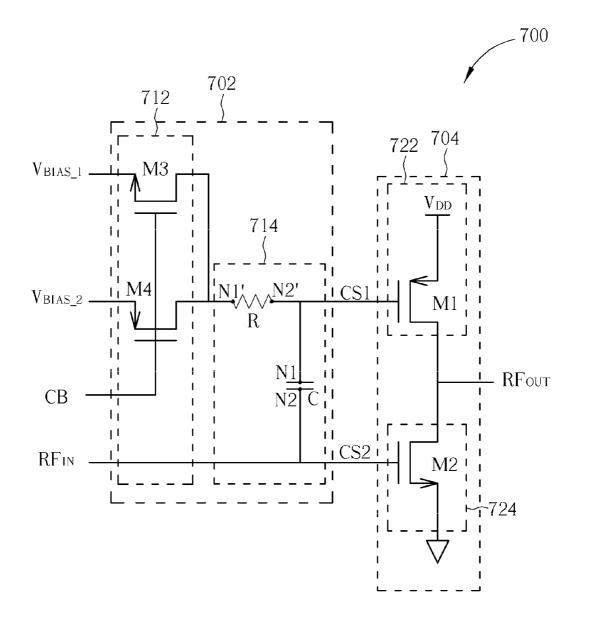

FIG. **7** is a diagram illustrating a first circuit implementation of the output cell shown in FIG. **6** according to an exem- <sup>15</sup> plary embodiment of the present invention.

FIG. **8** is a diagram illustrating a second circuit implementation of the output cell shown in FIG. **6** according to an exemplary embodiment of the present invention.

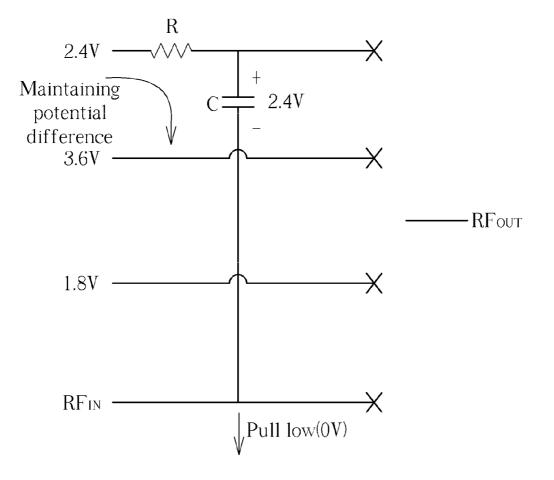

FIG. **9** is a diagram illustrating a time-domain waveform of <sup>20</sup> a single bit operation of the output cell shown in FIG. **7**.

FIG. **10** is a diagram illustrating a third circuit implementation of the output cell shown in FIG. **6** according to an exemplary embodiment of the present invention.

FIG. **11** is a diagram illustrating an equivalent circuit of the <sup>25</sup> output driver shown in FIG. **10** that is operating in an ON state.

FIG. **12** is a diagram illustrating an equivalent circuit of the output driver shown in FIG. **10** that is operating in an OFF state.

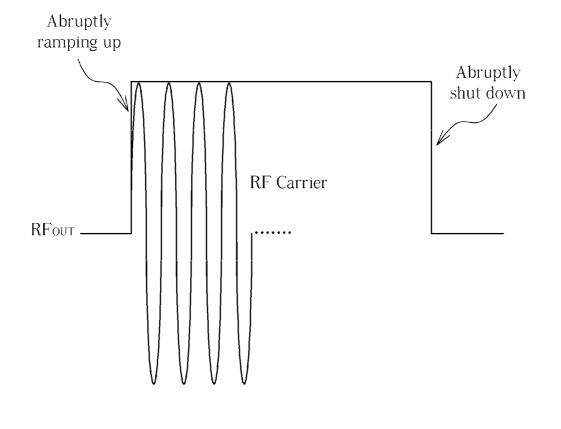

FIG. 13 is a diagram illustrating a time-domain waveform of a single bit operation of the output cell shown in FIG. 10.

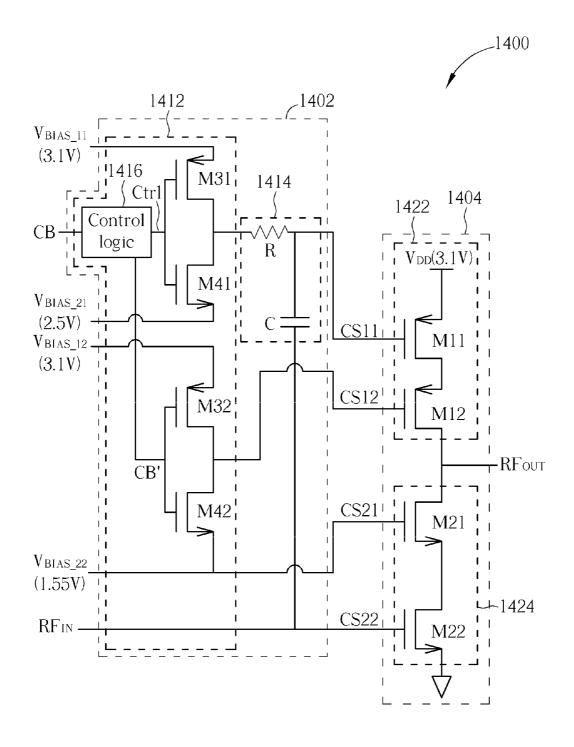

FIG. **14** is a diagram illustrating a fourth circuit implementation of the output cell shown in FIG. **6** according to an exemplary embodiment of the present invention.

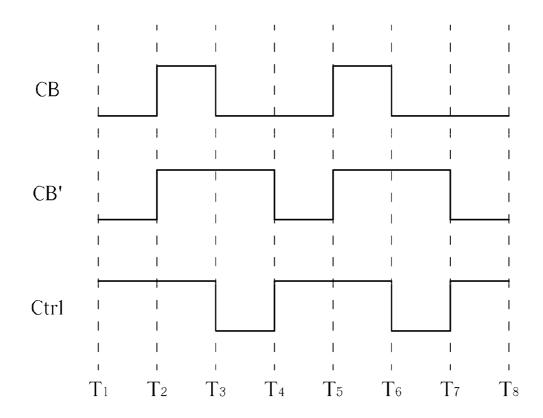

FIG. **15** is a waveform diagram of the digital control bit and the control outputs according to an exemplary embodiment of the present invention.

FIG. **16** is a diagram illustrating an equivalent circuit of the output driver shown in FIG. **14** that is operating in an ON <sup>40</sup> state.

FIG. **17** is a diagram illustrating an equivalent circuit of the output driver shown in FIG. **14** that is operating in a pre-charging state.

FIG. **18** is a diagram illustrating an equivalent circuit of the <sup>45</sup> output driver shown in FIG. **14** that is operating in an OFF state.

FIG. **19** is a diagram illustrating a time-domain waveform of a single bit operation of the output cell shown in FIG. **14**.

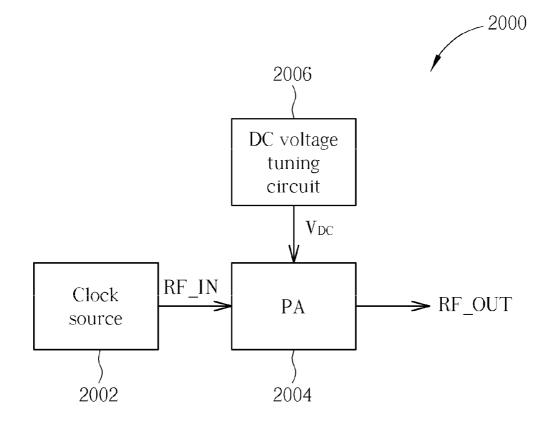

FIG. **20** is a diagram illustrating a transmitter employing an <sup>50</sup> exemplary pulling mitigation mechanism according to an embodiment of the present invention.

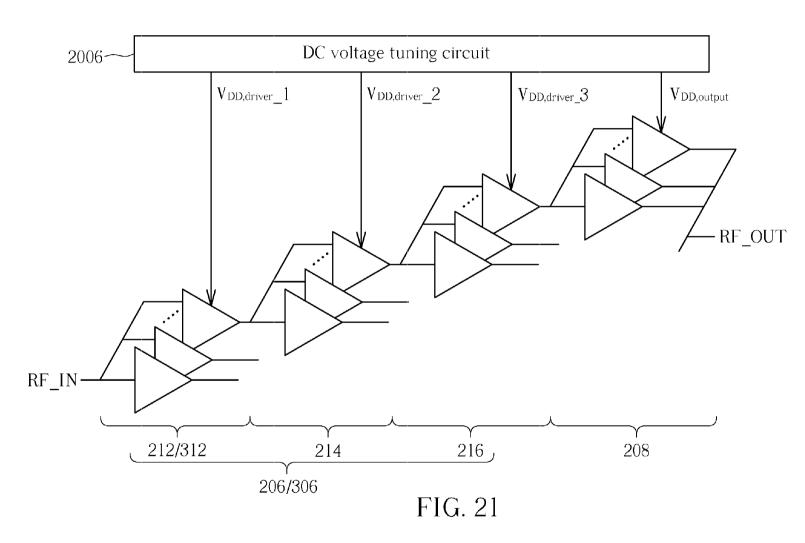

FIG. **21** is a diagram illustrating a multi-stage DPA with supply voltages tuned by a DC voltage tuning circuit for pulling mitigation of a clock source.

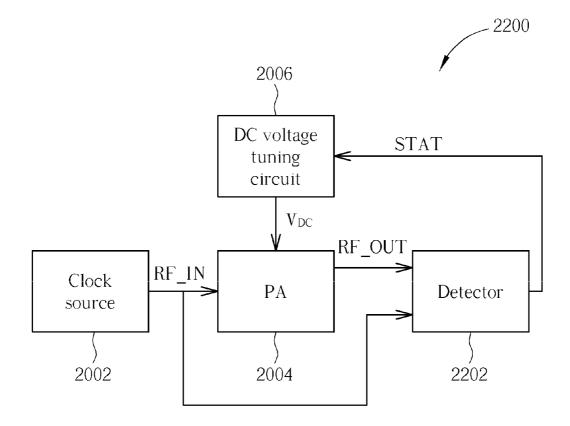

FIG. **22** is a diagram illustrating a transmitter employing another exemplary pulling mitigation mechanism according to an embodiment of the present invention.

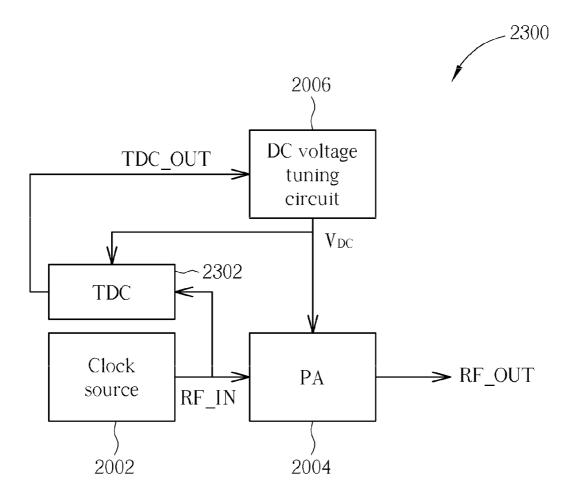

FIG. **23** is a diagram illustrating a transmitter employing yet another exemplary pulling mitigation mechanism accord- <sup>60</sup> ing to an embodiment of the present invention.

#### DETAILED DESCRIPTION

Certain terms are used throughout the description and fol- 65 lowing claims to refer to particular components. As one skilled in the art will appreciate, manufacturers may refer to a 4

component by different names. This document does not intend to distinguish between components that differ in name but not function. In the following description and in the claims, the terms "include" and "comprise" are used in an open-ended fashion, and thus should be interpreted to mean "include, but not limited to . . . ". Also, the term "couple" is intended to mean either an indirect or direct electrical connection. Accordingly, if one device is electrically connected to another device, that connection may be through a direct electrical connection, or through an indirect electrical connection via other devices and connections.

FIG. 1 is a block diagram illustrating a generalized structure of a multi-stage digitally-controlled power amplifier (DPA) according to an exemplary embodiment of the present invention. The exemplary multi-stage DPA 100 includes, but is not limited to, a radio-frequency (RF) clock input 102, an amplitude control word (ACW) input 104, a driver stage 106 having a plurality of drivers (i.e., driver cells) 107\_1-107\_M included therein, and an output stage 108 having a plurality of output cells 109 1-109 N included therein. The RF clock input 102 is arranged for receiving an RF clock RF\_IN. For example, the RF clock RF\_IN is a phase-contented (PM) signal in a polar transmitter, and therefore carries phaserelated information. The ACW input 104 is arranged for receiving a digital ACW signal (e.g., a digital control word) ACW\_IN. For example, the digital ACW signal ACW\_IN is an amplitude-contented (AM) signal in a polar transmitter, and therefore carries amplitude-related information. The drivers 107\_1-107\_M are coupled to the RF clock RF\_IN, and arranged for producing a plurality of intermediate signals S 1-S K. Regarding the output stage 108, it is coupled to the driver stage 106 for receiving the intermediate signals S\_1-S\_K and producing an output signal RF\_OUT according to the received intermediate signals S 1-S K.

In this exemplary design, at least one of the drivers 107\_1-107\_M is responsive to at least one bit of the digital ACW signal ACW\_IN, and/or at least one of the output cells 109\_1-109\_N is responsive to at least one bit of the digital ACW signal. That is, at least one of the drivers 107\_1-107\_M is controlled according to at least one bit of the digital ACW signal ACW\_IN, and/or at least one of the output cells 109\_1-109\_N is controlled according to at least one bit of the digital ACW signal. By way of example, but not limitation, one or more output cells may be directly controlled by bit(s) of the digital ACW signal ACW\_IN, or may be controlled by control bit(s) derived from processing bit(s) of the digital ACW signal ACW IN.

In one exemplary design, the DPA cells 107\_1-107\_M and 109\_1-109\_N included in the driver stage 106 and the output stage 108 may be arranged in a tree topology or a chain topology, depending upon the interconnections among the DPA cells. Please refer to FIG. 2, which is a diagram illustrating a first implementation of a multi-stage DPA according to an embodiment of the present invention. The multi-stage DPA 200 is based on the hardware configuration shown in FIG. 1, and therefore has a driver stage 206 and an output stage 208, where the driver stage 206 receives an RF clock RF\_IN (e.g., a PM signal) from an RF clock input 202, and the output stage 208 receives an ACW input ACW\_IN from an ACW input 204. The driver stage 206 has a plurality of cascaded stages 212, 214 and 216. It should be noted that the number of the cascaded stages employed in the driver stage 206 is for illustrative purposes only. The stage 212 includes a plurality of drivers 211, the stage 214 includes a plurality of drivers 213, and the stage 216 includes a plurality of drivers 215. Each driver 211 in stage 212 may be coupled to one or more drivers 213 in the next stage 214. Besides, the number of drivers 213 coupled to one driver 211 may be equal to or different from the number of drivers 213 coupled to another driver 211, depending upon actual design requirement/consideration. In a case where a tree topology is employed, the number of drivers 213 coupled to one driver 211 may be 5 greater than one.

Similarly, each driver 213 in the stage 214 may be coupled to one or more drivers 215 in the next stage 216. Besides, the number of drivers 215 coupled to one driver 213 may be equal to or different from the number of drivers 215 coupled to 10 another driver 213, depending upon actual design requirement/consideration. In a case where a tree topology is employed, the number of drivers 215 coupled to one driver **213** may be greater than one.

Regarding the output stage 208, it includes a plurality of 15 output cells 217. Each driver 215 in the driver stage 206 is coupled to one or more output cells 217 in the output stage 208. As shown in FIG. 2, each output cell 217 has an input port P1 and an output port P2. The input port P1 is coupled to one of the intermediate signals S, generated from the drivers 20 215 located at the last stage 216. Output ports P2 of all output cells 217 are coupled to each other (directly, as shown here, although an indirect coupling could also be used) such that the output signal RF\_OUT is derived from a summation of signal outputs of enabled output cells 217. In a case where a tree 25 topology, the number of output cells 217 coupled to one driver **215** may be greater than one.

By way of example, but not limitation, all of the drivers 211, 213, 215 and output cells 217 shown in FIG. 2 may be configured to be responsive to the digital ACW signal 30 ACW\_IN for controlling the power level of the output signal RF\_OUT. Hence, the discrete drivers 211, 213, 215 included in the driver stage 206 may be controlled independently, and the discrete output cells 217 included in the output stage 208 may be controlled independently. As mentioned above, the 35 is to provide an innovative multi-stage arrangement of DPA driver stage 206 is used to couple the phase-contented and amplitude-contented RF carrier to the output stage 208, and the output stage 208 is used to deliver the integral signal at the RF carrier frequency and required power level. Hence, with proper setting of bits transmitted via the digital ACW signal 40 ACW\_IN, the power of the output signal RF\_OUT would be set to the required power level.

In the example shown in FIG. 2, all of the drivers 211, 213, 215 and output cells 217 included in the multi-stage DPA 200 are responsive to the digital ACW signal ACW\_IN. However, 45 this is for illustrative purposes only, and is not meant to be a limitation of the present invention. Please refer to FIG. 3. which is a diagram illustrating a second implementation of a multi-stage DPA according to an embodiment of the present invention. The multi-stage DPA 300 is also based on the 50 hardware configuration shown in FIG. 1. The major difference between the multi-stage DPAs 200 and 300 is that at least one of drivers directly connected to the RF clock input 202 is not responsive to any bit of the digital ACW signal ACW\_IN. By way of example, but not limitation, all of the drivers (i.e., 55 driver cells) 311 disposed at the stage 312 shown in FIG. 3 are not controlled by the digital ACW signal ACW\_IN. In other words, all of the drivers 311 are enabled when the multi-stage DPA **300** is operative to generate the output signal RF\_OUT. One benefit/advantage of such a design is that the load viewed 60 by a preceding circuit component (e.g., a DCO which generates the RF clock RF\_IN) would be constant, thus improving stability and accuracy of the overall transmitter system.

The aforementioned DPA driver cell employed in the driver stage may be simply implemented using an inverter 65 buffer 400, as shown in FIG. 4. The inverter buffer 400 is arranged to generate an RF output according to an RF input,

6

where a digital control bit decides whether the inverter buffer 400 is enabled or disabled. Alternatively, the aforementioned DPA driver cell employed in the driver stage may be implemented using a logic gate, such as an AND gate 500 shown in FIG. 5. Therefore, the AND gate 500 generates an RF output by mixing an RF input and a digital control bit, where a logic gating operation is controlled by the digital control bit.

The aforementioned DPA output cell employed in the output stage may be simply implemented using the inverter buffer 400 shown in FIG. 4. Therefore, the DPA output cell is directly controlled by the digital control bit. Alternatively, the DPA output cell may be indirectly controlled by the digital control bit. FIG. 6 is a diagram illustrating an output cell employed in an output stage of a multi-stage DPA according to an exemplary embodiment of the present invention. The output cell 600 includes a controller 602 and an output driver 604. The controller 602 receives one or more DC bias voltages, one or more digital control bits and an RF input, and generates one or more intermediate control signals to the following output driver 604 according to the actual design of the output driver 604. For example, the output driver 604 may be a class-D amplifier, including a P-type block with P-type transistor(s) and an N-type block with N-type transistor(s). Hence, the controller 602 is configured to generate intermediate controls signals to gate terminals of transistors employed in the output driver 604. The output driver 604 generates an RF output according to intermediate control signal(s).

The DPA driver cell/output cell may be configured in a single-ended topology to meet the requirement of a singleended application. Alternately, the DPA driver cell/output cell may be configured in a differential topology to meet the requirement of a differential application.

Please note that the main concept of the present invention cells, including driver cells in a driver stage and output cells in an output stage, rather than an implementation of the DPA cell. Any DPA cell design capable of achieving the desired functionality of the driver cell/output cell may be employed to realize the DPA cells employed in the multi-stage DPA 100/ 200/300. This also obeys the spirit of the present invention, and falls within the scope of the present invention.

By way of example, but not limitation, the proposed multistage DPA 100/200/300 may have one or all of the following features. Each stage is fully operated in a switching mode for highest efficiency. There is no DC level biasing needed. Each unit has a single RF input containing phase information only. Each unit has a single RF output containing phase and partial amplitude information.

Regarding the output cell 600 shown in FIG. 6, several circuit implementations are provided hereinafter for illustrative purposes. FIG. 7 is a diagram illustrating a first circuit implementation of the output cell 600 shown in FIG. 6 according to an exemplary embodiment of the present invention. The output cell 700 includes a controller 702 and an output buffer 704. The controller 702 is arranged for receiving a plurality of bias voltages  $\mathrm{V}_{\mathit{BIAS}\_1}$  and  $\mathrm{V}_{\mathit{BIAS}\_2},$  an RF input  $RF_{TN}$ , and a digital control bit CB (i.e., one bit of a digital ACW signal), and generating a plurality of intermediate control signals CS1 and CS2. In this embodiment, the controller 702 includes a control block 712 and a coupling block 714. The control block 712 is arranged for controlling the intermediate control signals CS1 and CS2 according to the bias voltages  $V_{BLAS-1}$  and  $V_{BLAS-2}$ , the RF input RF<sub>IN</sub>, and the digital control bit CB. The output driver 704 is arranged for generating an RF output  $RF_{OUT}$  according to the intermediate control signals CS1 and CS2. In this embodiment, the

output driver **704** has cascoded blocks **722** and **724**, where the block **722** is a P-type block and the block **724** is an N-type block. The P-type block **722** has a P-type metal-oxide-semiconductor (MOS) transistor M1 responsive to the intermediate control signal CS1, and the N-type block M2 has an 5 N-type MOS transistor M2 responsive to the intermediate control signal CS2.

Regarding the control block **712**, it includes an N-type MOS transistor **M3** and a P-type MOS transistor **M4** both controlled by the digital control bit CB. For example, when 10 the N-type MOS transistor **M3** is enabled (i.e., switched on), the P-type MOS transistor **M4** is disabled (i.e., switched off), and when the N-type MOS transistor **M3** is disabled (i.e., switched off), the P-type MOS transistor **M3** is disabled (i.e., switched on). As can be seen from FIG. **7**, the DC bias voltage 15 of the MOS transistor **M1** is set by  $V_{BLAS_{-1}}$  when the MOS transistor **M3** is enabled by the digital control bit CB (i.e., CB='1'), and the DC bias voltage of the MOS transistor **M1** is set by  $V_{BLAS_{-2}}$  when the MOS transistor **M4** is enabled by the digital control bit CB (i.e., CB='1'). Besides, the control 20 block **712** directly transmits the RF input RF<sub>IN</sub> as the intermediate control signal CS**2**.

The coupling block **714** includes a capacitor C and a resistor R, where the capacitor C has a first end N1 coupled to gate of the P-type MOS transistor M1 and a second end N2 25 coupled to gate of the N-type MOS transistor M2, and the resistor R has a first end N1' coupled to the preceding control block **712** and a second end N2' coupled to the first end N1 of the capacitor C. The capacitor C is used for AC coupling such that AC signal components carried by the RF input RF<sub>IN</sub> is 30 coupled to the gate of the MOS transistor M1. To put it another way, each of the intermediate control signals CS1 and CS2 would have AC signal components, and DC levels of the intermediate control signal CS2 as 5 may be 0.6V, whereas the DC level of the intermediate control signal CS1 is either V<sub>BIAS\_1</sub> or V<sub>BIAS\_2</sub>.

As can be readily seen from FIG. 7, the output driver **704** is not inductor-loaded. Hence, no class- $D^{-1}$ /class-E amplifier is employed in the output cell **700**. By way of example, the 40 output driver **704** is implemented using a class-D amplifier, thus avoiding the voltage swing problem encountered by the conventional class- $D^{-1}$ /class-E DPA cell structure. Specifically, the voltage swing of the output cell **700** is limited within the  $V_{DD}$  rail. The supply voltage  $V_{DD}$  of the output cell **700** is 45 therefore allowed to be increased to approach the nominal voltage value of the battery, which improves the battery efficiency accordingly. Besides, as the voltage swing of the output cell **700** is limited within the  $V_{DD}$  rail, reliability of core devices and I/O devices are ensured. 50

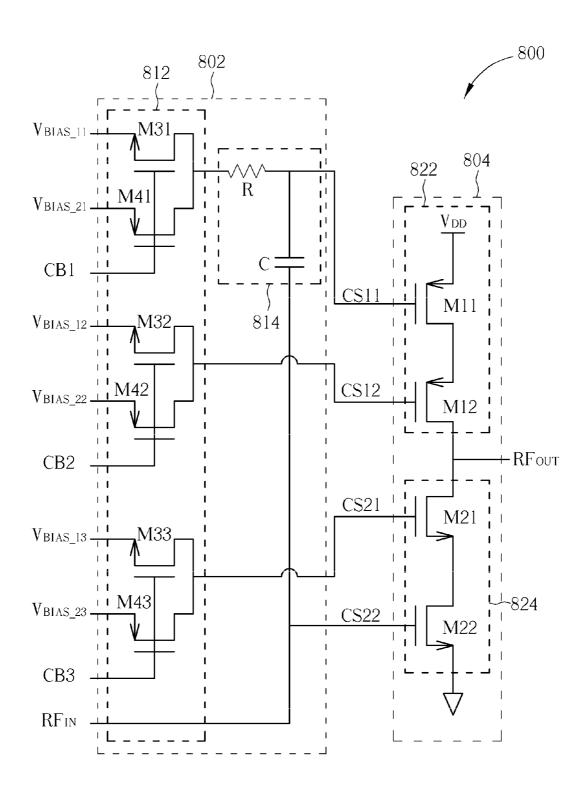

The number of P-type MOS transistors included in the P-type block 722 shown in FIG. 7 and the number of N-type MOS transistors included in the N-type block 724 shown in FIG. 7 are for illustrative purposes. Using multiple intermediate control signals to control multiple inputs of the N-type 55 block and/or the P-type block is possible. FIG. 8 is a diagram illustrating a second circuit implementation of the output cell 600 shown in FIG. 6 according to an exemplary embodiment of the present invention. The exemplary output cell 800 includes a controller 802 and an output buffer 804. The P-type 60 block 822 has multiple P-type MOS transistors M11 and M12, and the N-type block 824 has multiple N-type MOS transistors M21 and M22. As each of the P-type block 822 and N-type block 824 has more than one MOS transistor, the controller 802 is therefore configured to provide multiple 65 intermediate control signals CS11, CS12, CS21, CS22 to multiple inputs of the output driver 804. In this embodiment,

8

the controller 802 includes a control block 812 and a coupling block 814. The coupling block 814 has a capacitor C coupled between gates of the MOS transistors M11 and M22, and a resistor R coupled between the preceding control block 812 and the following output driver 804. Regarding the control block 812, it includes a plurality of N-type MOS transistors M31, M32, M33 and a plurality of P-type MOS transistors M41, M42, M43, where MOS transistors M31 and M41 are controlled by a digital control bit CB1 to determine which one of the bias voltages  $V_{BIAS_{-11}}$  and  $V_{BIAS_{-21}}$  should be outputted to the following resistor R, MOS transistors M32 and M42 are controlled by a digital control bit CB2 to determine which one of the bias voltages  $V_{BLAS\_12}$  and  $V_{BLAS\_22}$  should be outputted as the intermediate control signal CS12, and MOS transistors M33 and M43 are controlled by a digital control bit CB3 to determine which one of the bias voltages  $V_{BIAS_{-13}}$  and  $V_{BIAS_{23}}$  should be transmitted as the intermediate control signal CS21. Besides, the RF input RF<sub>IN</sub> is directly transmitted as the intermediate control signal CS22. The same objective of avoiding the voltage swing problem is achieved as the output driver 804 is not an inductor-loaded class-D<sup>-1</sup>/class-E amplifier.

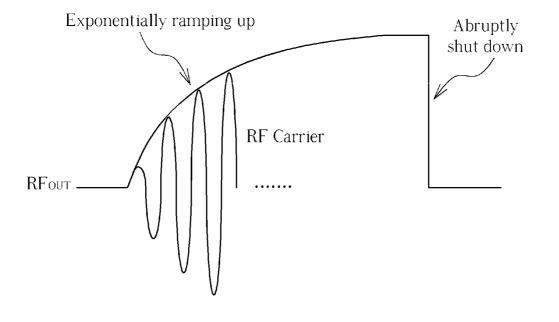

It should be noted that the coupling block 714/814, including the resistor R and the capacitor C, may have impact on the intermediate control signal, thus affecting the transient waveform of the RF output  $RF_{OUT}$ . Please refer to FIG. 9, which is a diagram illustrating a time-domain waveform of a single bit operation of the output cell 700 shown in FIG. 7. The timedomain waveform has a negative exponential ramping up at the positive edge due to the RC circuit boot-strapping effect resulting from charging via the resistor R and the capacitor C, and has an abrupt shutdown at the negative edge due to the immediate shutdown of the MOS transistors M1 and M2. If the positive edge can also show an abrupt ramping up, an ideal zero-order-hold (ZOH) DAC behavior can be obtained. The present invention therefore proposes a solution which achieves the objective of setting the output cell 700 to have the ZOH DAC behavior by using a digitally-controlled charging technique such as a ZOH charging control.

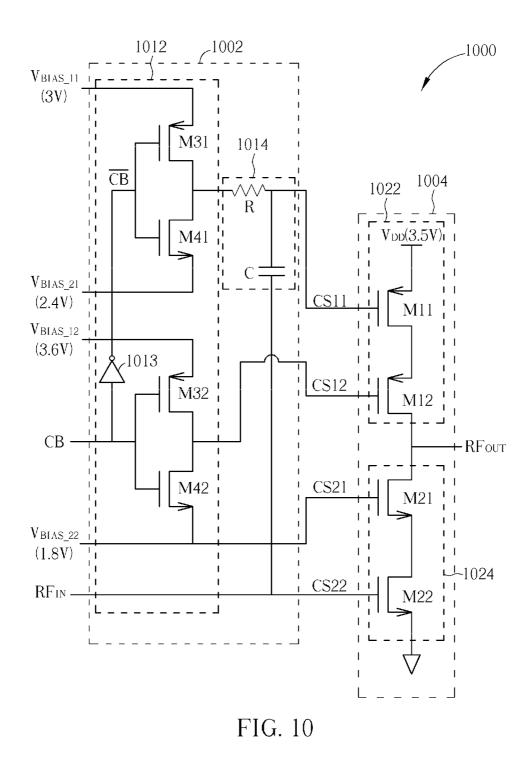

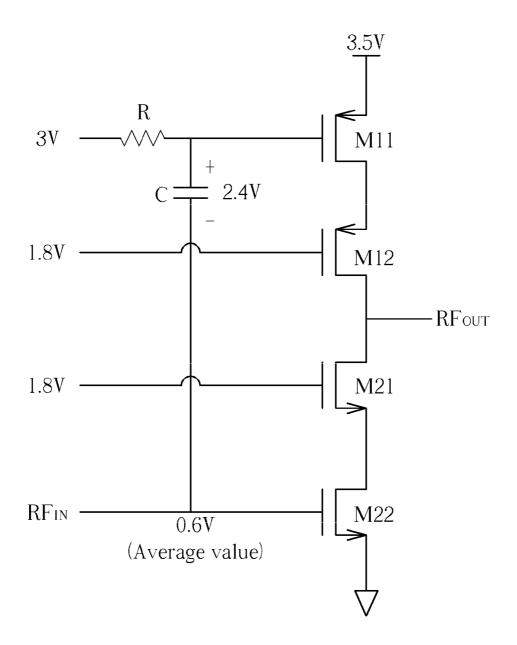

FIG. 10 is a diagram illustrating a third circuit implementation of the output cell 600 shown in FIG. 6 according to an exemplary embodiment of the present invention. The exemplary output cell 1000 has a controller 1002 and an output driver 1004. The output driver 1004 operates under a supply voltage  $V_{DD}$  (e.g., 3.5V), and generates an RF output RF<sub>OUT</sub> according to intermediate control signals CS11, CS12, CS21, CS22. The P-type block 1022 has cascoded P-type MOS transistors M11 and M12, and the N-type block 1024 has cascoded N-type MOS transistors M21 and M22. In this embodiment, the output cell 1000 realizes the transient waveform control by changing the circuitry and control sequence of the controller 1002. Specifically, the output cell 1000 is abruptly turned on and off in response to one bit of the digital ACW signal. Regarding the controller 1002, it includes a control block 1012 and a coupling block 1014. The coupling block 1014 has a resistor R and a capacitor C, where the desired abrupt turning on is performed through resistive precharging of the capacitor C. Further details are described as below.

Regarding the control block **1012**, it includes a plurality of P-type MOS transistors M**31**, M**32** and a plurality of N-type MOS transistors M**41**, M**42**, where MOS transistors M**32** and M**42** are controlled by a digital control bit CB to determine which one of the bias voltages  $V_{BL4S_{-12}}$  (e.g., 3.6V) and  $V_{BL4S_{-22}}$  (e.g., 1.8V) should be outputted as the intermediate control signal CS**12**, and the MOS transistors M**31** and M**41** are controlled by an inverse version of the digital control bit

CB (e.g.,  $\overline{CB}$  generated by an inverter **1013**) to determine which one of the bias voltages  $V_{BIAS_{-11}}$  (e.g., 3V) and  $V_{BIAS_{-21}}$  (e.g., 2.4V) should be outputted to the following resistor R. Besides, the RF input RF<sub>IV</sub> is directly provided as the intermediate control signal CS**22**, and the bias voltage  $V_{BIAS_{-22}}$  is directly provided as the intermediate control signal CS**21**. It should be noted that the high impedance 3V node (i.e., 3V supplied to source of the P-type MOS transistor M**31**) is necessary for clamping a DC voltage level from leakage discharging at the positive supply rail due to AC signal coupling.

The digital control bit CB controls the output driver 1004 to operate in either an ON state or an OFF state. When the digital control bit CB is logic high (i.e., CB='1"), the MOS transistors M31, M42, M11, M12, M21, M22 are enabled (i.e., switched on) and MOS transistors M41 and M32 are disabled (i.e., switched off), the output driver 1004 operates in the ON state. It should be noted that ON/OFF states of the MOS transistors M11, M12, M21, M22 may also be controlled by 20 the RF input RF<sub>IN</sub>. For example, when RF<sub>IN</sub>=0, the MOS transistor M22 is off no matter what CB is. Please refer to FIG. 11, which is a diagram illustrating an equivalent circuit of the output driver 1004 operating in an ON state. Supposing the average value of the RF input  $RF_{IN}$  is 0.6V resulting from <sup>25</sup> the DC level toggling between 0V and 1.2V, the voltage across the AC coupling capacitor C is 2.4V. When the digital control bit CB is logic low (i.e., CB='0"), the MOS transistors M41 and M32 are enabled (i.e., switched on) and the MOS transistors M31, M42, M11, M12, M21, M22 are disabled (i.e., switched off), the output driver 1004 operates in the OFF state. Please refer to FIG. 12, which is a diagram illustrating an equivalent circuit of the output driver 1004 operating in an OFF state. When the output driver 1004 enters the OFF state, 35 the controller 1002 is operative to maintain the potential difference of the capacitor C. As the bottom terminal of the capacitor C would be pulled low to 0V due to the RF input RF<sub>IN</sub> gated off by earlier stages, a pre-charging voltage potential 2.4V is developed at the top terminal of the capacitor C.  $_{40}$ As can be readily seen from FIG. 11 and FIG. 12, no matter whether the output driver 1004 is operating in the ON state or the OFF state, the voltage across the capacitor C is fixed at 2.4V. When the digital control bit CB has a transition from '0' to '1', the output driver 1004 would leave the OFF state and 45 enters the ON state. As the bottom terminal of the capacitor C would be increased to the average value of the RF input  $\mathrm{RF}_{IN}$ (e.g., 0.6V), the top terminal of the capacitor C would be correspondingly boosted to 3.0V (e.g., 2.4V+0.6V), which is identical to the desired DC bias level needed under the ON 50 state. In this way, the RC boot-strapping effect resulting from charging via the resistor R and the capacitor C is avoided.

FIG. **13** is a diagram illustrating a time-domain waveform of a single bit operation of the output cell **1000** shown in FIG. **10**. As a potential difference maintenance phase for the AC 55 coupling capacitor C is added during the OFF state to eliminate the long transient settling resulting from the RC bootstrapping effect, the output cell **1000** is abruptly turned on and off in response to the digital control bit CB (i.e., one bit of the digital ACW signal). Hence, with a proper change of the 60 controller circuitry as well as related control sequence, the output cell **1000** may have an ideal ZOH DAC behavior as shown in FIG. **13**.

It should be noted that the proposed ZOH capacitor charging control technique is not limited to the DPA cell design shown in FIG. **10**. For example, the proposed ZOH capacitor charging control technique may be applied to any of the output cells **700** and **800** for transient waveform control. These alternative designs all fall within the scope of the present invention.

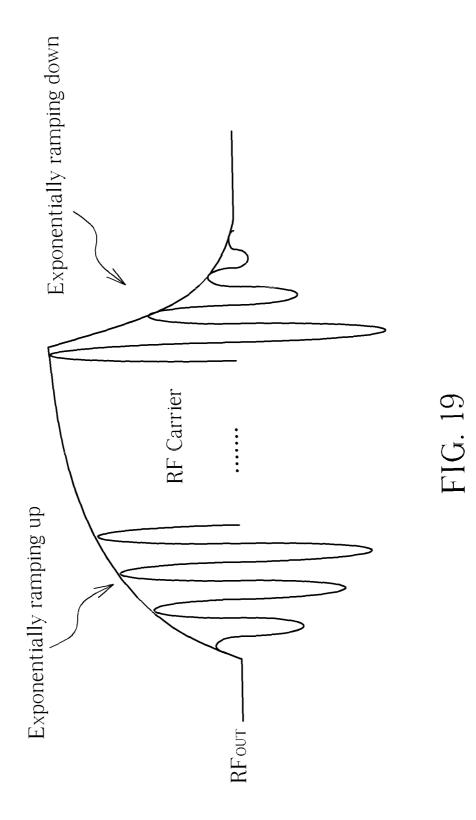

As shown in FIG. 9, the time-domain waveform has a negative exponential ramping up at the positive edge due to the RC boot-strapping effect, and has an abrupt shutdown at the negative edge due to the immediate shutdown of the MOS transistors M1 and M2. If the negative edge can also show a corresponding exponential ramping down, the one-bit pulse is roughly equivalently 1st order low-pass filtered at the baseband or bandpass filtered at the RF carrier. That is, reduction of the out-of-band (OOB) noise/replica may be achieved when the output cell is capable of generating a one-bit pulse having a negative exponential ramping up at the positive edge and a corresponding negative exponential ramping down at the negative edge. The present invention proposes a solution which achieves the objective by using a digitally-controlled charging technique such as an RC-interpolation charging control.

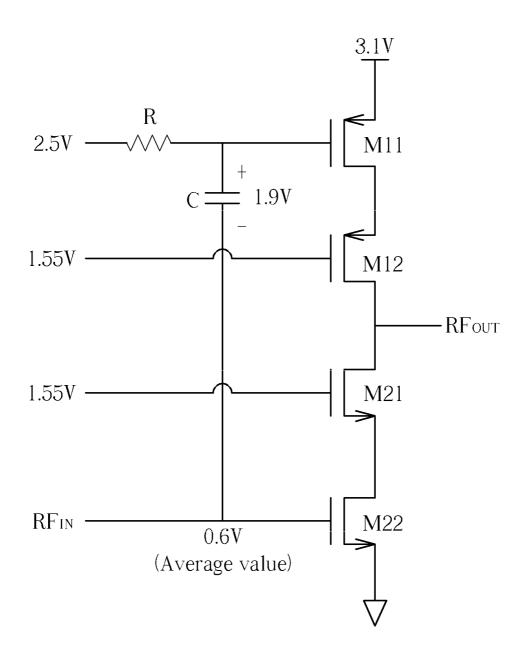

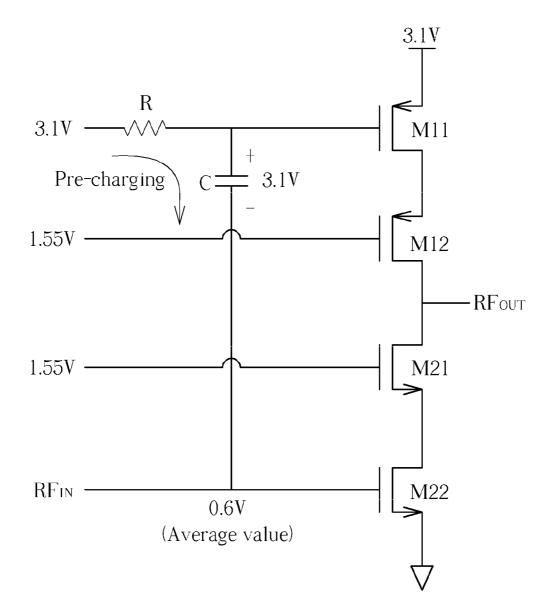

FIG. 14 is a diagram illustrating a fourth circuit implementation of the output cell 600 shown in FIG. 6 according to an exemplary embodiment of the present invention. The exemplary output cell 1400 has a controller 1402 and an output driver 1404. The output driver 1404 operates under a supply voltage  $V_{DD}$  (e.g., 3.1V), and generates an RF output RF<sub>OUT</sub> according to intermediate control signals CS11, CS12, CS21, CS22. The P-type block 1422 has cascoded P-type MOS transistors M11 and M12, and the N-type block 1424 has cascoded N-type MOS transistors M21 and M22. In this embodiment, the output cell 1400 realizes the RF bandpass filtering by changing the circuitry and control sequence of the controller 1402. Specifically, the output cell 1400 is gradually turned on and off in response to one bit of the digital ACW signal (i.e., a digital control bit CB). Regarding the controller 1402, it includes a control block 1412 and a coupling block 1414. The coupling block 1414 has a resistor R and a capacitor C, where the desired gradual turning on and off is performed through resistive charging of the capacitor C. Further details are described as below.

Regarding the control block 1412, it includes a control logic 1416, a plurality of P-type MOS transistors M31, M32 and a plurality of N-type MOS transistors M41, M42. The control logic 1416 is arranged to generate a plurality of control outputs Ctrl and CB' according to a digital control bit CB (e.g., one bit of a digital ACW signal). Please refer to FIG. 15, which is a waveform diagram of the digital control bit CB and the control outputs CB' and Ctrl according to an exemplary embodiment of the present invention. In one exemplary design, the control output CB' may be derived from delaying the transition from a logic high level to a logic low level of the digital control bit CB. Hence, compared to the digital control bit CB, the control output CB' has extended logic-high periods. Regarding the control signal Ctrl, it may be derived from delaying an inverse version of the digital control bit CB. However, this is for illustrative purposes only, and is not meant to be a limitation of the present invention.

The MOS transistors M32 and M42 are controlled by the control output CB' to determine which one of the bias voltages  $V_{BLAS\_12}$  (e.g., 3.1V) and  $V_{BLAS\_22}$  (e.g., 1.55V) should be outputted as the intermediate control signal CS12. The MOS transistors M31 and M41 are controlled by the control output Ctrl to determine which one of the bias voltages  $V_{BLAS\_11}$  (e.g., 3.1V) and  $V_{BLAS\_21}$  (e.g., 2.5V) should be outputted to the following resistor R. Besides, the RF input RF<sub>IN</sub> is directly transmitted as the intermediate control signal CS22, and the bias voltage  $V_{BLAS\_22}$  is directly transmitted as the intermediate control signal CS21.

The control outputs Ctrl and CB' control the output driver **1404** to operate in an ON state, a pre-charging stage or an OFF state. When the control output CB' is logic high (i.e., CB'='1") and the control output Ctrl is also logic high (i.e., Ctrl='1') during the period between  $T_2$  and  $T_3$ , the MOS transistors 5 **M41**, M42, M11, M12, M21, M22 are enabled (i.e., switched on) and MOS transistors M31 and M32 are disabled (i.e., switched off), the output driver **1404** operates in the ON state as shown in FIG. **16**, which is a diagram illustrating an equivalent circuit of the output driver **1404** operating in an 10 ON state.

When the control output CB' is logic high (i.e., CB'='1") and the control output Ctrl is logic low (i.e., Ctrl='0'), the MOS transistors M31, M42, M11, M12, M21, M22 are enabled (i.e., switched on) and the MOS transistors M41, 15 M32 are disabled (i.e., switched off) during the period between  $T_3$  and  $T_4$ , the output driver 1404 operates in the pre-charging state. Specifically, when a negative edge of the digital control bit CB is indicative of an ON-to-OFF state transition of the output driver 1404 at  $T_3$ , the control block 20 1412 is operative to delay the ON-to-OFF state transition and pre-charge the capacitor C concurrently. Please refer to FIG. 17, which is a diagram illustrating an equivalent circuit of the output driver 1404 operating in a pre-charging state. When the output driver 1404 enters the pre-charging state, the con- 25 troller 1402 is operative to pre-charge the capacitor C. It should be noted that the bottom terminal of the capacitor C is not pulled low to 0V right away, otherwise the abrupt shutdown causes no slow transient at the ON-to-OFF transition. The pre-charging voltage 3.1V is intentionally supplied to the 30 capacitor C, thereby allowing the output driver 1404 to have an exponential RC behavior at the negative edge.

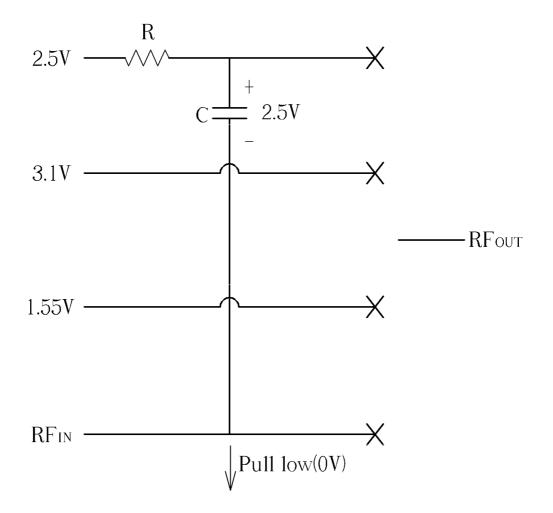

When the control output CB' is logic low (i.e., CB'='0") and the control output Ctrl is logic high (i.e., Ctrl='1"), the MOS transistors M32, M41 are enabled (i.e., switched on) 35 and the MOS transistors M31, M42, M11, M12, M21, M22 are disabled (i.e., switched off) during the period between T<sub>4</sub> and T<sub>5</sub>, the output driver 1404 operates in the OFF state. Specifically, when the control output CB' has a transition from '1' to '0' and the control output CB' has a transition from '0' to '1', the output driver 1004 would leave the pre-charging state and enters the OFF state and the bottom terminal of the capacitor C would be pulled low to 0V as shown in FIG. 18, which is a diagram illustrating an equivalent circuit of the output driver 1404 operating in an OFF state.

FIG. 19 is a diagram illustrating a time-domain waveform of a single bit operation of the output cell 1400 shown in FIG. 14. As the shutdown operation is delayed due to a pre-charging state inserted between the ON state and the OFF state, the negative exponential RC ramping down is allowed to occur at 50 the negative edge. In this way, the output cell 1400 is gradually turned on and off in response to the digital control bit CB (i.e., one bit of the digital ACW signal). Hence, with a proper change of the controller circuitry as well as control sequence, the output cell 1400 having bandpass filtering is realized. The 55 output cell 1400 may achieve maximum available efficiency of the battery and reduces the OOB noise floor for multi-radio coexistence.

It should be noted that the proposed RC-interpolation charging control technique is not limited to the DPA cell 60 design shown in FIG. **14**. For example, the proposed RCinterpolation charging control technique may be applied to any of the output cells **700** and **800** for transient waveform control. These alternative designs all fall within the scope of the present invention. 65

The exemplary DPA output stage cell mentioned above may be employed for implementing the output stage **208** in the proposed multi-stage DPA **200/300**. However, this is not meant to be a limitation of the present invention. Any DPA design using the exemplary DPA output stage cell mentioned above falls within the scope of the present invention.

Furthermore, the exemplary DPA output stage cell mentioned above may be used in a DPA coupled to a jointed transmission/reception (T/R) RF port. For example, the output signal RF\_OUT shown in FIG. 2/FIG. 3 is directly coupled to a balun. In the transmitting mode, the limited voltage rail-to-rail swing ensures that transmitter device and receiver devices are ensured to be reliable for all allowable battery voltage levels. Hence, the proposed battery-efficient design can be realized without any constraint on circuit reliability. In the receiving mode, the DPA is turned off through gates of cascoded MOS transistors in each output cell. High balun Z-transformation ratio increases the matching gain of the low-noise amplifier (LNA), resulting in high voltage gain, low noise figure (NF), and low power consumption. To put it simply, the proposed DPA design has several advantages/ benefits, such as limited voltage rail-to-rail swing and higher load-line impedance. The limited voltage rail-to-rail swing ensures the reliability of core devices and I/O devices. The higher load-line impedance allows smaller transistor sizes, which reduces driven load. Thus, the current consumption of the driver stage may be highly reduced while maintaining the phase noise requirements.

Due to the feedback path established by magnetic coupling and/or direct coupling (e.g., coupling via the printed circuit board (PCB) ground and/or the package ground), the transmitter output may be fed back to a clock source in the transmitter, which may degrade the transmitter performance. Thus, there is a need for a pulling mitigation mechanism employed to improve the transmitter performance. FIG. 20 is a diagram illustrating a transmitter employing an exemplary pulling mitigation mechanism according to an embodiment of the present invention. The transmitter 2000 includes a clock source 2002, a power amplifier (PA) 2004, and a direct current (DC) voltage tuning circuit 2006. The PA 2004 is arranged for receiving a radio-frequency (RF) clock RF\_IN derived from the clock source 2002, and producing an output signal RF\_OUT according to at least the RF clock RF\_IN. By way of example, but not limitation, the clock source 2002 may include a local oscillator (LO) such as a digitally controlled oscillator (DCO). The DC voltage tuning circuit 2006 is arranged for tuning at least one DC voltage  $V_{DC}$  supplied to the PA 2004 for pulling mitigation of the clock source 2002. Specifically, the phase of the output signal RF\_OUT is adjusted in response to the at least one DC voltage  $V_{DC}$  tuned by the DC voltage tuning circuit 2006. In this way, the undesired pulling of the clock source 2002 can be mitigated by applying phase tuning upon the feedback loop from the transmitter output (i.e., the output signal RF\_OUT of the PA 2004) to the clock source 2002. By way of example, but not limitation, the at least one DC voltage  $V_{DC}$  may include a supply voltage or a bias voltage.

The proposed pulling mitigation mechanism may be applied to the above-mentioned multi-stage DPA. In one exemplary design, the PA 2004 shown in FIG. 20 includes a DPA such as the exemplary multi-stage DPA 100/200/300, and the at least one DC voltage  $V_{DC}$  includes supply voltage(s) of the driver stage 106/206/306 and/or the output stage 108/208. FIG. 21 is a diagram illustrating a multi-stage DPA with supply voltages tuned by a DC voltage tuning circuit for pulling mitigation of a clock source (e.g., a DCO). As shown in FIG. 21, the aforementioned multi-stage DPA 200/300 is modified to have supply voltage(s) tuned by the DC voltage tuning circuit 2006, where a first driver-stage

supply voltage  $V_{DD,driver_{-1}}$  is supplied to drivers in the first cascaded stage 212/312 of the driver stage 206/306, a second driver-stage supply voltage  $V_{DD,driver_2}$  is supplied to drivers in the second cascaded stage 214 of the driver stage 206/306, a third driver-stage supply voltage  $V_{DD,driver_3}$  is supplied to drivers in the third cascaded stage 216 of the driver stage 206/306, and an output-stage supply voltage  $V_{DD,output}$  is supplied to output cells in the output stage 208. It should be noted that driver-stage supply voltages  $V_{DD,driver_1}$ -10  $V_{DD,driver_3}$  and output-stage supply voltage  $V_{DD,output}$  may have the same DC voltage level or different DC voltage levels.

In this example, all of the cells in the multi-stage DPA 200/300 are reused for feedback phase control via propagational delay adjustment. However, this is for illustrative purposes only, and is not meant to be a limitation of the present invention. In other words, the same objective of controlling the phase of the output signal RF\_OUT for clock source pulling mitigation may be achieved by tuning supply voltage of at least one of the stages 212/312, 214, 216, and 208.

As mentioned above, the phase of the output signal RF\_OUT dominates the pulling mitigation performance. With a proper setting of the at least one DC voltage  $V_{DC}$ supplied to the PA 2004, the pulling mitigation of the clock source 2002 may be optimized by optimally setting the 25 aggressing phase generated by the PA versus the victim phase. The present invention therefore proposes adding a calibration element to the proposed pulling mitigation mechanism. Alternative designs of the transmitter 2000 shown in FIG. 20 are described as below. 30

FIG. 22 is a diagram illustrating a transmitter employing another exemplary pulling mitigation mechanism according to an embodiment of the present invention. The transmitter 2200 includes a detector 2202 and the aforementioned clock source 2002, PA 2004 and DC voltage tuning circuit 2006. 35 The detector 2202 is operable of producing a statistic STAT of a delay (or the phase) between the RF clock  $RF_{IN}$  and the output signal RF\_OUT. The DC voltage tuning circuit 2006 refers to the statistic STAT to adjust the at least one DC voltage V<sub>DC</sub> 40

FIG. 23 is a diagram illustrating a transmitter employing yet another exemplary pulling mitigation mechanism according to an embodiment of the present invention. The transmitter 2300 includes a time-to-digital converter (TDC) 2302 and the aforementioned clock source 2002, PA 2004 and DC 45 voltage tuning circuit 2006. For example, the transmitter 2300 is an ADPLL-based transmitter, and the TDC 2303 is reused in the feedback phase control. The DC voltage  $V_{DC}$ supplied to the PA 2004 is also shared with the TDC 2302. The timing delay characteristics of the TDC 2302 and the PA 50 2004 are highly correlated hence the TDC could be used as a 'proxy' for the PA delay. The TDC 2302 is arranged to digitally output the quantized time difference between the generated RF\_IN clock and a reference clock (not shown). Thus generated TDC output TDC\_OUT can be used to estimate the 55 inverter delay. The DC voltage tuning circuit 2006 is arranged to operate in response to calculating of the TDC output TDC\_OUT, where the calculating of the TDC output TDC\_OUT is operable to provide an estimate of the TDC element delay characteristic (e.g., an inverter delay). Hence, 60 based on the estimate of the TDC element delay characteristic, the DC voltage tuning circuit 2006 is arranged to adjust the DC voltage  $V_{DC}$  for substantially maintaining the TDC element delay characteristic.

Those skilled in the art will readily observe that numerous 65 modifications and alterations of the device and method may be made while retaining the teachings of the invention.

Accordingly, the above disclosure should be construed as limited only by the metes and bounds of the appended claims.

What is claimed is:

- 1. A digitally-controlled power amplifier (DPA) with bandpass filtering, comprising:

- a radio-frequency (RF) clock input, arranged for receiving an RF clock;

- an amplitude control word (ACW) input, arranged for receiving a digital ACW signal; and

- a plurality of DPA cells, coupled to said RF clock and said digital ACW signal, wherein at least one of said DPA cells is gradually turned on and off in response to at least one bit of said digital ACW signal.

- 2. The DPA of claim 1, wherein gradual turning on and off is performed through resistive charging of a capacitor.

3. The DPA of claim 1, wherein said at least one of said DPA cells comprises.

- a controller, arranged for receiving at least a bit of said digital ACW signal, and generating a plurality of intermediate control signals; and

- an output driver, arranged for generating an RF output according to said intermediate control signals, said output driver comprising:

- a P-type block, having at least a P-type MOS transistor responsive to a first intermediate control signal of said intermediate control signals; and

- an N-type block, having at least an N-type MOS transistor responsive to a second intermediate control signal of said intermediate control signals.

- 4. The DPA of claim 3, wherein said controller comprises:

- a coupling block, comprising a capacitor having a first end coupled to a gate of said P-type MOS transistor and a second end coupled to a gate of said N-type MOS transistor: and

- a control block, arranged for controlling said intermediate control signals according to at least said bit of said digital ACW signal.

5. The DPA of claim 4, wherein said coupling block further comprises a resistor having a first end coupled to said control block and a second end coupled to said first end of said capacitor.

6. The DPA of claim 4, wherein when said bit of said digital ACW signal is indicative of an ON-to-OFF state transition of said output driver, said control block is operative to delay said ON-to-OFF state transition and pre-charge said capacitor concurrently.

7. The DPA of claim 3, wherein said output driver is a class-D amplifier.

8. A digitally-controlled power amplifier (DPA) with transient waveform control, comprising:

- a radio-frequency (RF) clock input, arranged for receiving an RF clock;

- an amplitude control word (ACW) input, arranged for receiving a digital ACW signal; and

- a plurality of DPA cells, coupled to said RF clock and said digital ACW signal, wherein at least one of said DPA cells is abruptly turned on and off in response to at least one bit of said digital ACW signal.

- 9. The DPA of claim 8, wherein abrupt turning on is performed through resistive charging of a capacitor.

- 10. The DPA of claim 8, wherein said at least one of said DPA cells comprises:

- a controller, arranged for receiving at least a bit of said digital ACW signal, and generating a plurality of intermediate control signals; and

30

- an output driver, arranged for generating an RF output according to said intermediate control signals, said output driver comprising:

- a P-type block, having at least a P-type MOS transistor responsive to a first intermediate control signal of said <sup>5</sup> intermediate control signals; and

- an N-type block, having at least an N-type MOS transistor responsive to a second intermediate control signal of said intermediate control signals.

11. The DPA of claim 10, wherein said controller comprises:

- a coupling block, comprising a capacitor having a first end coupled to a gate of said P-type MOS transistor and a second end coupled to a gate of said N-type MOS tranistor; and

- a control block, arranged for controlling said intermediate control signals according to at least said bit of said digital ACW signal.

12. The DPA of claim 11, wherein said coupling block  $_{20}$  further comprises a resistor having a first end coupled to said control block and a second end coupled to said first end of said capacitor.

**13**. The DPA of claim **11**, wherein when said output driver enters an OFF state, said control block is operative to maintain a potential difference of said capacitor.

14. The DPA of claim 10, wherein said output driver is a class-D amplifier.

**15**. A digitally-controlled power amplifier (DPA) cell, comprising:

- a controller, arranged for generating a plurality of intermediate control signals according to a plurality of bias voltages, a radio-frequency (RF) input, and a bit of a digital amplitude control word (ACW) signal; and

- an output driver, arranged for generating an RF output <sup>35</sup> according to said intermediate control signals, said output driver comprising:

- a P-type block, having at least a P-type MOS transistor responsive to a first intermediate control signal of said intermediate control signals; and 40

- an N-type block, having at least an N-type MOS transistor responsive to a second intermediate control signal of said intermediate control signals;

- wherein said controller refers to said bit of said ACW signal to select at least one of said bias voltages to set at least one of said intermediate control signals.

16. The DPA cell of claim 15, wherein said controller comprises:

- a coupling block, comprising a capacitor having a first end coupled to a gate of said P-type MOS transistor and a second end coupled to a gate of said N-type MOS transistor; and

- a control block, arranged for controlling said intermediate control signals according to said bias voltages, said RF input, and said bit of said digital ACW signal.

- 17. The DPA cell of claim 16, wherein when said bit of said digital ACW signal is indicative of an ON-to-OFF state transition of said output driver, said control block is operative to delay said ON-to-OFF state transition and pre-charge said capacitor concurrently.

**18**. The DPA cell of claim **16**, wherein when said output driver enters an OFF state, said control block is operative to maintain a potential difference of said capacitor.

**19**. The DPA cell of claim **15**, wherein said output driver is a class-D amplifier.

- **20**. A digitally-controlled power amplifier (DPA) cell, comprising:

- a controller, arranged for generating a plurality of intermediate control signals according to a plurality of bias voltages, a radio-frequency (RF) input, and a bit of a digital amplitude control word (ACW) signal; and

- an output driver, arranged for generating an RF output according to said intermediate control signals, said output driver comprising:

- a P-type block, having at least a P-type MOS transistor responsive to a first intermediate control signal of said intermediate control signals; and

- an N-type block, having at least an N-type MOS transistor responsive to a second intermediate control signal of said intermediate control signals;

wherein said controller comprises:

a control block, arranged for controlling said intermediate control signals according to said bias voltages, said RF input, and said bit of said digital ACW signal; and

a coupling block, comprising:

- a capacitor having a first end coupled to a gate of said P-type MOS transistor and a second end coupled to a gate of said N-type MOS transistor; and

- a resistor having a first end coupled to said control block and a second end coupled to said first end of said capacitor.

\* \* \* \* \*