US008742808B2

## (12) United States Patent

## Staszewski et al.

## (10) Patent No.: US 8,742,808 B2 (45) Date of Patent: Jun. 3, 2014

### (54) DIGITAL PHASE LOCKED LOOP

(71) Applicant: Texas Instruments Incorporated,

Dallas, TX (US)

(72) Inventors: Robert Bogdan Staszewski, Delft (NL);

Dirk Leipold, San Jose, CA (US)

(73) Assignee: Texas Instruments Incorporated,

Dallas, TX (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 24 days.

(21) Appl. No.: 13/710,691

(22) Filed: **Dec. 11, 2012**

(65) Prior Publication Data

US 2013/0093480 A1 Apr. 18, 2013

## Related U.S. Application Data

- (62) Division of application No. 10/131,523, filed on Apr. 24, 2002, now Pat. No. 8,385,476.

- (60) Provisional application No. 60/286,572, filed on Apr. 25, 2001.

- (51) **Int. Cl. H03L** 7/06

(2006.01)

(52) U.S. Cl.

USPC ...... **327/156**; 327/147

(58) Field of Classification Search

## (56) References Cited

## U.S. PATENT DOCUMENTS

| 3,683,277 A | 8/1972 | Kuller et al. |

|-------------|--------|---------------|

| 4,068,199 A | 1/1978 | Madoff        |

| 4,259,644 A | 3/1981 | Iimura        |

| 8/1983  | Wakinson                                                                                                      |

|---------|---------------------------------------------------------------------------------------------------------------|

| 4/1986  | Carney et al.                                                                                                 |

| 12/1986 | Koga et al.                                                                                                   |

| 3/1989  | Martin                                                                                                        |

| 9/1989  | Thomas                                                                                                        |

| 10/1991 | Hietala et al.                                                                                                |

| 7/1992  | Mutz                                                                                                          |

| 7/1992  | Freeburg et al.                                                                                               |

| 4/1994  | Nakamura                                                                                                      |

| 11/1996 | Oura et al.                                                                                                   |

| 6/1998  | Boerstler                                                                                                     |

| 8/1998  | Kawabata                                                                                                      |

| 9/1998  | Tajima et al.                                                                                                 |

| 6/1999  | Yokota et al.                                                                                                 |

| (Con    | tinued)                                                                                                       |

|         | 4/1986<br>12/1986<br>3/1989<br>9/1989<br>10/1991<br>7/1992<br>4/1994<br>11/1996<br>6/1998<br>8/1998<br>9/1998 |

### FOREIGN PATENT DOCUMENTS

| DE | 198 40 030 | 12/1999  |

|----|------------|----------|

| EP | 0 484 158  | 5/1992   |

|    | (Co        | ntinued) |

Primary Examiner — Adam Houston

(74) Attorney, Agent, or Firm — Ronald O. Neerings; Wade James Brady; Frederick J. Telecky, Jr.

## (57) ABSTRACT

A phase locked loop circuit (30, 100, 110) includes a controllable oscillator (42) for generating an output signal of desired frequency responsive to a control signal, a first phase detection circuit (32, 102, 112) for generating an output indicative of phase differential responsive to the output signal and a first edge of a reference signal and a second phase detection circuit (34, 104, 114) for generating an output indicative of phase differential responsive to the output signal and a second edge of a reference signal. The control signal to the controllable oscillator (42) is driven by the outputs of the first and second phase detections circuits.

## 22 Claims, 7 Drawing Sheets

# US 8,742,808 B2 Page 2

| (56) |           |      | Referen | ces Cited      | 2003/0118142<br>2005/0286505 |       | 6/2003<br>12/2005 | Xiu et al.<br>Harrison |

|------|-----------|------|---------|----------------|------------------------------|-------|-------------------|------------------------|

|      | -         | U.S. | PATENT  | DOCUMENTS      | 2006/0087346                 | A1*   | 4/2006            | Ishida et al 327/3     |

|      |           |      |         |                | 2006/0176089                 |       | 8/2006            | Yamane et al 327/156   |

|      | 5,950,115 | A    | 9/1999  | Momtaz et al.  | 2007/0030043                 |       | 2/2007            | Takai et al            |

| :    | 5,995,552 | A    | 11/1999 | Moriyama       | 2007/0041483                 |       | 2/2007            | Iwata et al            |

|      | 5,018,275 |      | 1/2000  | Perrett et al. | 2007/0279134                 |       | 12/2007           | Yamane et al           |

| (    | 5,094,078 | A *  | 7/2000  | Suzuki 327/156 | 2008/0136485                 |       | 6/2008            | Takai et al            |

|      | 5,104,222 |      | 8/2000  | Embree         | 2008/0279323                 |       | 11/2008           | Harrison 375/374       |

| (    | 5,112,308 | A    | 8/2000  | Self et al.    | 2010/0007383                 |       | 1/2010            | Harrison               |

|      | 5,122,336 |      | 9/2000  | Anderson       | 2010/0061499                 |       | 3/2010            | Mijuskovic             |

|      | 5,148,215 |      | 11/2000 | Doi et al.     | 2010/0225372                 |       | 9/2010            | Satoh et al            |

|      | 5,317,006 |      | 11/2001 | Welland et al. | 2010/0226188<br>2010/0321120 |       | 9/2010<br>12/2010 | Kim et al              |

|      | 5,321,074 |      | 11/2001 | Lemay          | 2010/0321120                 |       |                   | Kim et al              |

|      | 5,483,880 |      | 11/2002 | Moriyama       | 2011/0204948                 |       | 8/2011            | Satoh et al            |

|      | 5,526,270 |      | 2/2003  | Nakashima      | 2011/0304371                 |       | 12/2011<br>8/2012 | Ravi et al             |

|      | 5,704,380 |      | 3/2004  | Kaewell        |                              |       |                   |                        |

|      | 5,704,383 |      | 3/2004  | Lee et al.     | 2012/0223754                 |       |                   |                        |

|      | 5,724,265 |      | 4/2004  | Humphreys      | 2012/0274373                 |       | 11/2012           | Ku                     |

|      | 5,728,526 |      | 4/2004  | Yamada et al.  | 2013/0093480                 |       | 4/2013            |                        |

|      | 5,741,577 |      |         | Henon          | 2013/0135011                 | A1 *  | 5/2013            | Chen et al 327/12      |

|      | 5,891,906 |      | 5/2005  | Sogabe et al.  |                              |       |                   |                        |

|      | 5,914,935 |      | 7/2005  | Eklof          | FO                           | REIG  | N PATE            | NT DOCUMENTS           |

|      | 5,965,753 |      | 11/2005 | Miller et al.  |                              |       |                   |                        |

|      | 7,076,217 |      |         | Luff et al.    | EP                           | 0 519 | 892               | 12/1992                |

|      | /0020866  |      | 9/2001  | Toshinori      | EP                           | 0 708 | 398               | 4/1996                 |

|      | /0094034  |      | 7/2002  | Moriyama       | EP                           | 0 952 | 669               | 10/1999                |

|      | /0137460  |      | 9/2002  | Sun et al.     |                              |       |                   |                        |

| 2003 | /0090328  | A1   | 5/2003  | McDowell       | * cited by exar              | niner |                   |                        |

Jun. 3, 2014

## DIGITAL PHASE LOCKED LOOP

## CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a divisional of prior application Ser. No. 10/131,523, filed Apr. 24, 2002, which claims the benefit of provisional application U.S. Ser. No. 60/286,572, filed Apr. 25, 2001.

## STATEMENT OF FEDERALLY SPONSORED RESEARCH OR DEVELOPMENT

Not Applicable

## BACKGROUND OF THE INVENTION

## 1. Technical Field

This invention relates in general to electronics and, more  $_{20}$ particularly, to a digital phase locked loop.

## 2. Description of the Related Art

A great reduction of the transistor features in recently developed deep-submicron CMOS processes shifts the design paradigm towards more digitally-intensive tech- 25 niques. In a monolithic implementation, the manufacturing cost of a design is measured not in terms of a number of devices used but rather in terms of the occupied silicon area, no matter what the actual circuit complexity.

Analog and RF circuits used in communication circuits, 30 however, are not easily implemented in a deep-submicron CMOS process. For example, in Texas Instruments' CMOS process (C035) of 0.08 µm L-effective features a digital gate density of 150K equivalent (2-input NAND) gates per mm<sup>2</sup>. An average-size inductor for an integrated LC oscillator 35 occupies about 0.5 mm<sup>2</sup> of silicon area. A low-noise charge pump, or a low-distortion image-reject modulator, both good examples of classical RF transceiver components, occupy roughly about the same area, which could be traded for tens of thousands of digital gates.

Migrating to a digitally-intensive synthesizer architecture brings forth the following well-known advantages: (1) fast design turn-around cycle using automated CAD tools (VHDL or Verilog hardware-level description language, synthesis, auto-place and auto-route with timing-driven algorithms, 45 parasitic backannotation and postlayout optimization), (2) much lower parameter variability than with analog circuits, (3) ease of testability, (4) lower silicon area and dissipated power that gets better with each CMOS technology advancement (also called a "process node") and (5) excellent chances 50 of first-time silicon success. Commercial analog circuits usually require several design iterations to meet marketing

There is a wide array of opportunities that integration presents. The most straightforward way would be to merge vari- 55 ous digital sections into a single silicon die, such as DRAM or Flash memory embedded into DSP or controller. More difficult would be integrating the analog baseband with the digital baseband. Care must be taken here to avoid coupling of digital noise into the high-precision analog section. In addition, the 60 low amount of voltage headroom challenges one to find new circuit and architecture solutions. Integrating the analog baseband into RF transceiver section presents a different set of challenges: the conventional Bi-CMOS RF process is tuned for high-speed operation with a number of available passive 65 tion, and the advantages thereof, reference is now made to the components and does not fundamentally stress high precision.

2

Sensible integration of diverse sections results in a number of advantages: (1) lower total silicon area—in a deep-submicron CMOS design, the silicon area is often bond-pad limited; consequently, it is beneficial to merge various functions on a single silicon die to maximize the core to bond-pad ratio, (2) lower component count and thus lower packaging cost, (3) power reduction—no need to drive large external inter-chip connections and (4) lower printed—circuit board (PCB) area, thus saving the precious "real estate."

Deep-submicron CMOS processes present new integration opportunities on one hand, but make it extremely difficult to implement traditional analog circuits, on the other. One such problem involves the design of a digital phase locked loop (DPLL). A PLL loop is a fixed-point phase domain architecture whose purpose is to generate a stable RF signal at a 15 desired frequency. The underlying frequency stability of the system is derived from a reference clock generated by a crystal oscillator, such as a temperature-compensated crystal oscillator (TCXO) used in mobile phones. Phase information between the output signal and the reference signal is used to update a controllable oscillator. This information is generated at an active edge of the reference clock. However, greater accuracy could be obtained by more frequent determinations of the phase information, leading to more frequent updates of the controllable oscillator.

Therefore, a need has arisen for a method and apparatus for a phase locked loop design that provides for increase accuracy in the output signal.

## BRIEF SUMMARY OF THE INVENTION

In a first aspect of the present invention, a phase locked loop circuit includes a controllable oscillator for generating an output signal of desired frequency, a first phase detection circuit for generating an output indicative of phase differential responsive to the output signal and a first edge of a reference signal and a second phase detection circuit for generating an output indicative of phase differential responsive to the output signal and a second edge of a reference signal. The controllable oscillator is driven responsive to the outputs of the first and second phase detections circuits.

This aspect of the invention increases the timing updates for the phase-locked loop since both edges of the reference clock are used for phase detection.

In a second aspect of the present invention, a mobile communication device comprises a frequency synthesizer for generating a carrier frequency output responsive to a local reference clock, circuitry for generating multiple clock signals of different frequencies synchronous to the carrier frequency output and digital baseband circuitry operating responsive to one or more of the multiple clock signals.

This aspect of the present invention allows for a plurality of clocks to be derived from the output of a frequency synthesizer. By reducing the number of phase-locked loop circuits use to generate clocks, unnecessary circuitry can be eliminated. Further, by providing a number of clocks synchronous to the RF carrier frequency, spurious noise throughout the mobile communication device can be controlled to reduce the effect on communications. An additional benefit is that complex circuitry for synchronizing the local reference signal to a master clock signal can be eliminated, and the carrier frequency can be synchronized to the master clock through minor adjustments to a phase error signal.

## BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWINGS

For a more complete understanding of the present invenfollowing descriptions taken in conjunction with the accompanying drawings, in which:

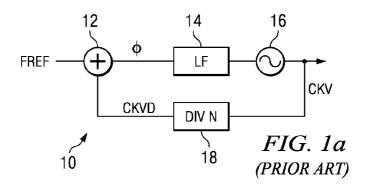

FIG. 1a illustrates a block diagram of a prior art phase locked loop circuit;

FIG. 1b illustrates a timing diagram showing the operation of the circuit of FIG. 1a;

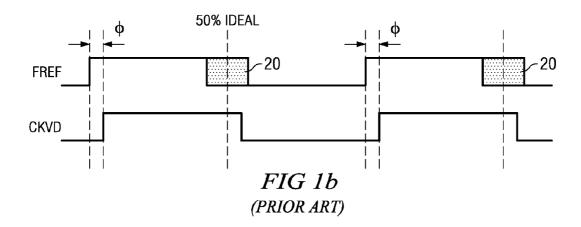

FIG. 2 illustrates a timing diagram showing relationships <sup>5</sup> between the rising and falling edges of a reference clock;

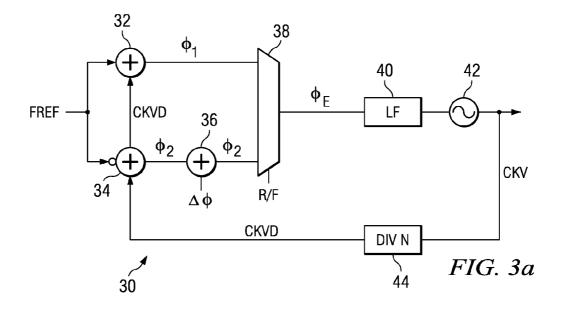

FIG. 3a illustrates a block diagram of a phase locked loop circuit capable of sampling on both edges of a reference clock:

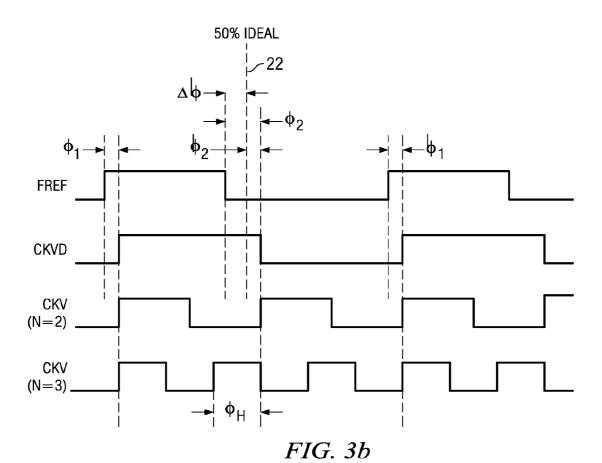

FIG. 3b illustrates a timing diagram showing the operation of the phase locked loop circuit of FIG. 3a;

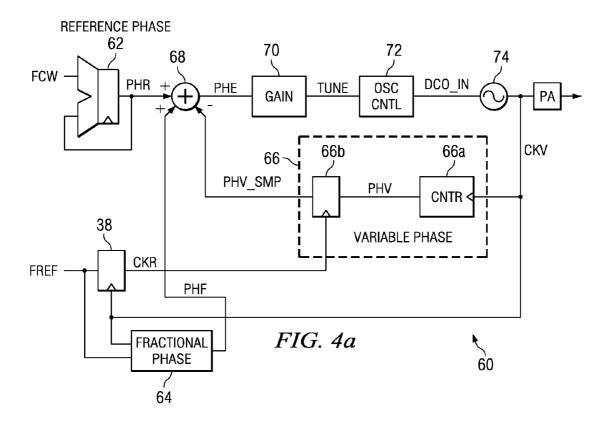

FIG. 4a illustrates a block diagram of an all digital phase locked loop (ADPLL);

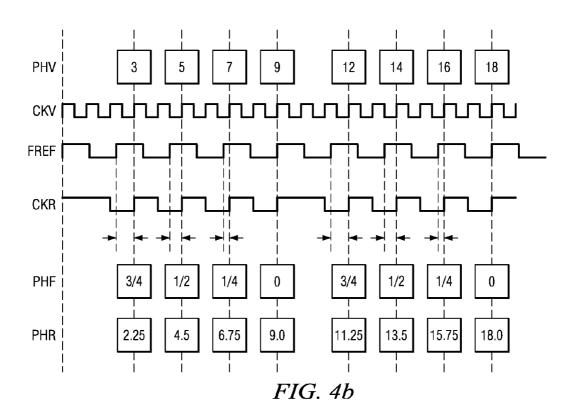

FIG. 4b illustrates a timing diagram showing the operation of the ADPLL of FIG. 4a;

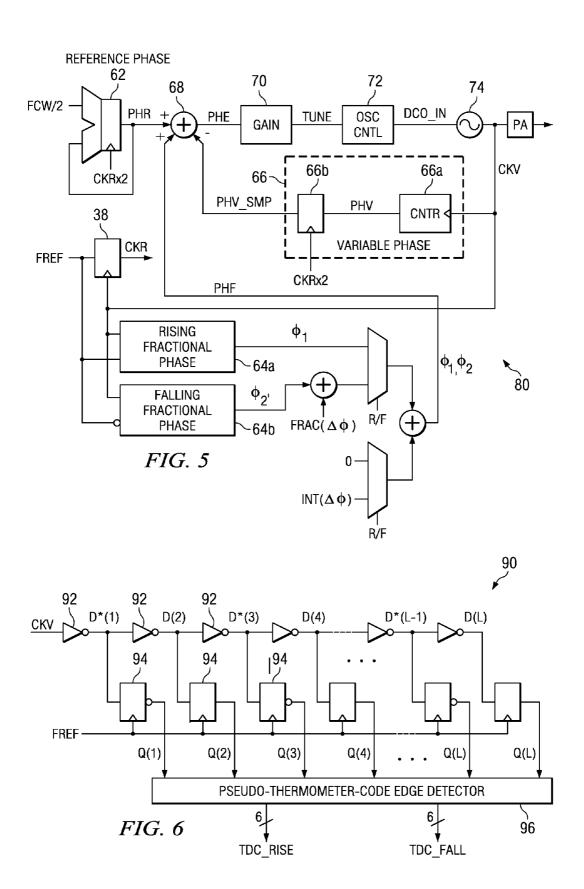

FIG. 5 illustrates an ADPLL using the both edges of the reference clock to double the sampling rate of the PLL operation:

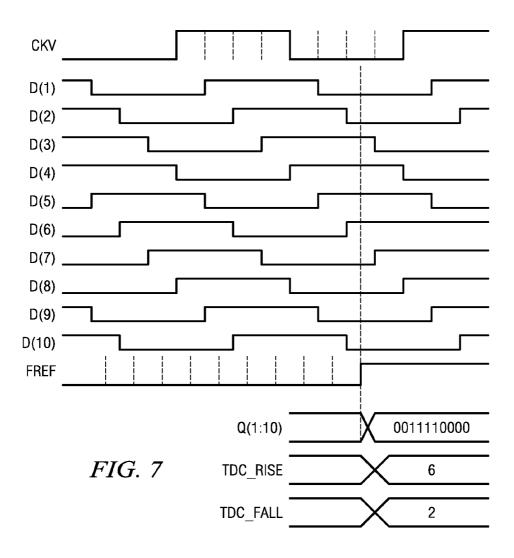

FIG.  ${\bf 6}$  illustrates a schematic diagram of a time-to-digital  $_{20}$  converter;

FIG. 7 illustrates a timing diagram showing the operation of the time-to-digital converter of FIG. 6;

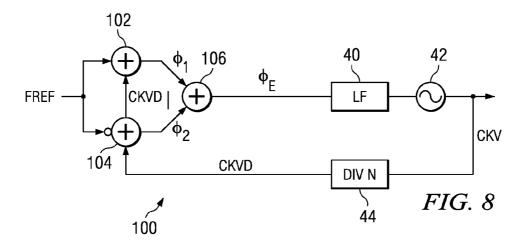

FIG. 8 illustrates a second embodiment of a PLL sampling on both edges of the reference clock;

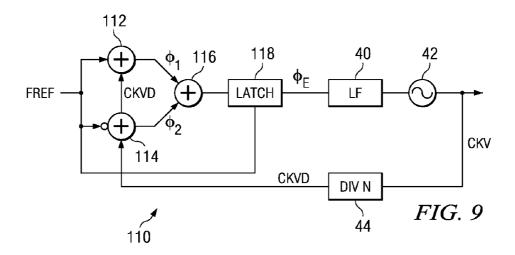

FIG. 9 illustrates a third embodiment of a PLL sampling on both edges of the reference clock;

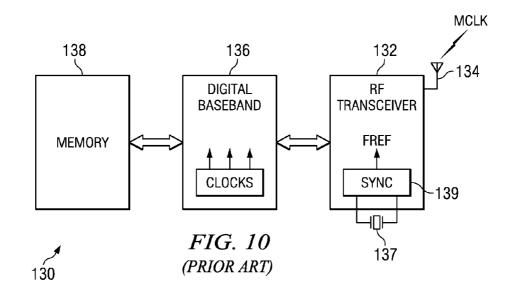

FIG. 10 illustrates a general block diagram of a prior art mobile communication device;

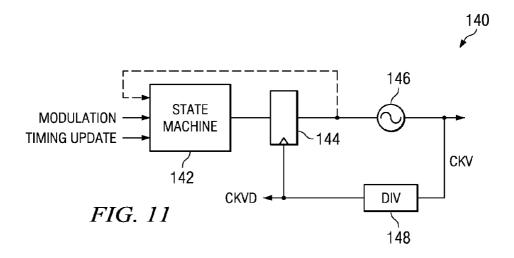

FIG. 11 illustrates a general block diagram of circuitry for providing a PLL function using a divided clock from the DCO as a synchronous clock for the RF transceiver and digital baseband circuit;

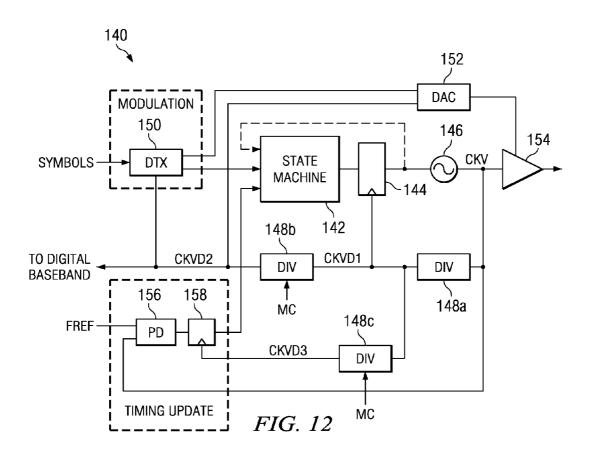

FIG. 12 illustrates a more detailed block diagram for a first embodiment of the circuit of FIG. 11; and

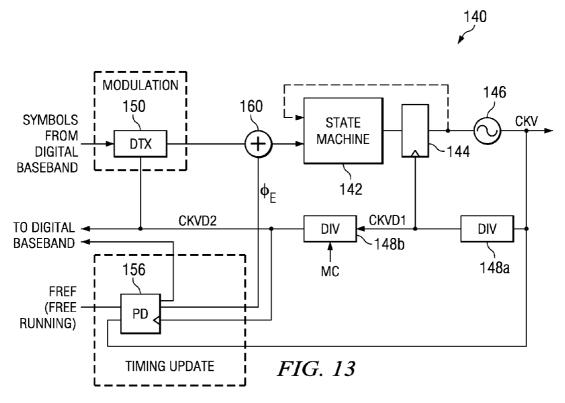

FIG. 13 illustrates a more detailed block diagram for a second embodiment of the circuit of FIG. 11.

## DETAILED DESCRIPTION OF THE INVENTION

The present invention is best understood in relation to FIGS. **1-13** of the drawings, like numerals being used for like elements of the various drawings.

FIG. 1a illustrates a block diagram of a generalized phase 45 locked loop device (PLL) 10. A reference frequency FREF, typically generated by a crystal oscillator, is input to a phase detector 12 along with CKVD, the divided-down clock output of the PLL 10. An error signal,  $\phi$ , is passed to a loop filter 14. The filtered signal adjusts the output of a controllable oscillator 16. The output of the controllable oscillator 16. CKV, is fed back to the phase detector 12 through a frequency divider 18.

In general, the phase detector (and, hence, the controllable oscillator) operates responsive to an active edge of the FREF 55 signal. For purposes of illustration throughout this specification, it will be assumed that the rising edge of FREF is the active edge; alternatively, the falling edge could be used as the active edge of FREF.

In many situations, it would be beneficial to compare the 60 phases and update the output signal more often. One possible solution would be to clock the phase detector and controllable oscillator at both the rising and falling edges of FREF.

As shown in FIG. 1*b*, however, clocking on both edges of the reference signal presents a problem. While the output of a 65 crystal oscillator produces a signal with a fairly accurate 50% duty cycle (i.e., the time between a rising edge and the sub-

4

sequent falling edge is exactly the same as the time between a falling edge and a subsequent rising edge), intervening circuitry can affect the duty cycle, such that the falling edge may occur within a range 20 in FIG. 1b. Consequently, the falling edge of FREF cannot be used as a mid-point between rising edges of FREF.

As shown in FIG. 2, the present invention uses a property of FREF to gain useful information from the falling edge of FREF. In FIG. 2, dashed line 22 shows the ideal 50% duty cycle mark for the falling edge. While the actual falling edge, shown at line 24 may be offset from the ideal, the time period  $T_{fall}$  between actual falling edges 24 equals the time period  $T_{rise}$  between rising edges. Thus, for each cycle, the actual falling edge 24 will be offset from the ideal 22 by a constant  $\Delta \phi$ .

FIG. 3a illustrates a first embodiment of the invention for using both edges of a reference clock in a PLL 30. FREF is input to a first phase detector 32 (which compares phase information on a first active edge, e.g. rising edge) of FREF and a second phase detector 34 (which compares phase information on a second active edge, e.g. falling edge) of FREF. Alternatively, the FREF signal is input to the first phase detector 32 and the inverted FREF signal is input to the second phase detector 34, and both phase detectors operate internally on the same active edge of the reference clock signals that are 180 degrees out of phase. The output of the first phase detector 32 is a first error signal  $\phi_1$  and the output of the second phase detector 34 is a second intermediate error signal  $\phi_2$ '. The intermediate error signal  $\phi_2$ ' is added to  $\Delta \phi$ through phase offset adder 36 to generate the second error signal  $\phi_2$ . The first and second error signals are input to multiplexer 38, which selects one of the first and second error signals responsive to an rising/falling (R/F) control signal, which indicates whether the current active edge of FREF is rising or falling. The output of multiplexer 38 is received by loop filter 40. The output of loop filter 40 drives oscillator 42. The output of oscillator 42 (CKV) is received by frequency divider 44. The divided output signal CKVD is transmitted to phase detectors 32 and 34.

FIG. 3*b* illustrates a timing diagram showing FREF, CKVD and two examples of CKV (for N=2 and N=3). As can be seen in FIG. 3*b*, when phase detectors compare FREF and CKVD as shown in FIG. 3*a*, phase detector 32 compares the rising edge of FREF with the rising edge of CKVD and phase detector 34 compares the falling edge of FREF (or the rising edge of the inverted FREF) with the falling edge of CKVD (or the rising edge of the inverted CKVD).  $\Delta \varphi$  is the phase difference between the actual falling edge of FREF and the ideal 50% duty cycle falling edge. For a rising edge,  $\varphi_E$ , the output of multiplexer 38, equals  $\varphi_1$  and, for a falling edge,  $\varphi_E$  equals  $\varphi_2$ , which equals  $\varphi_{2'+\Delta\varphi}$ .

It would also be possible to compare the edges of FREF with the output CKV. In this case, both the rising edge and falling edge of FREF would be compared to a rising edge of CKV, if N ( $f_{CKW}f_{FREF}$ ) was an even integer. If N is an odd integer, two approaches could be used. In the first approach, rising edges of FREF would be compared to rising edges of CKV and falling edges of FREF would be compared to falling edges of CKV (it would also be possible to compare rising edges of FREF to falling edges of CKV and vice-versa). In the second embodiment, a half-phase adjustment  $\phi_H$  could be added to  $\phi_2$ ' along with  $\Delta \phi$  by the phase offset adder  $\Delta \phi$ , such that  $\phi_2 = \phi_2$ '  $\Delta \phi + \phi_H$ .

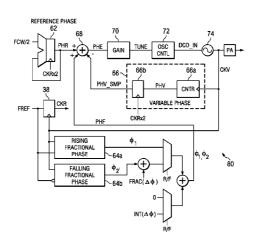

FIG. 4a illustrates a block diagram of an all digital PLL (ADPLL) 60 of the type disclosed in U.S. Ser. No. 10/008,462 to Staszewski et al, entitled "Frequency Synthesizer with

Phase Restart", filed Nov. 30, 2001, which is incorporated by reference herein. This ADPLL is designed to work off a single edge of FREF.

ADPLL 60 includes a reference phase accumulator 62 that calculates a reference phase signal (PHR), a fractional error correction circuit 64 that calculates a fractional error correction (PHF), and a variable phase accumulator 66 that calculates a variable phase correction (PHV\_SMP, which is integer only). The phase error (PHE) is calculated by phase detector 68 as PHE=PHR+PHF-PHV\_SMP (with proper bit alignment to line up integer and fractional portions). PHE is received by gain circuit 70 and oscillator control circuit 72. The oscillator control circuit 72 drives a digitally controlled oscillator 74

FCW (frequency control word) is the ratio of the desired frequency of CKV divided by the frequency of FREF. The reference phase signal is an accumulation of FCW at the active edge of CKR, which is the retimed FREF clock. The FCW input to the reference accumulator **62** is used to establish the operating reference phase of the desired channel plus the modulation data.

The variable phase accumulator **66** comprises a counter **66** a, which increments on each active edge of CKV and a latch **66** b that latches the output of the counter at CKR.

The fractional phase circuit **64** determines a difference between an active edge of FREF and the next active edge of CKV, normalized to a fraction of a CKV clock cycle.

Operation of the circuit is best understood in relation to the timing diagram of FIG. 4b, where an example of FCW=2.25 30 is used. In an actual circuit, however, FCW would typically be much higher. For purposes of illustration, FCW is a constant (i.e., no modulation) and there is no drift. As described above, the variable phase circuit 66 counts the CKV clocks and latches the count on the active (rising) edge of CKR. The PHV 35 from the variable phase circuit 66 counts are provided above the CKV signal. Also at each active edge of CKR, the reference phase circuit 62 accumulates another FCW.

At any active edge of CKR, the preceding active edge of FREF may have occurred at a point less than one CKV clock 40 cycle earlier (since CKR is retimed to CKV). This is shown by the dashed lines in FIG. 4b. PHF measures this fractional part of a CKV cycle. As can be seen in FIG. 4b, for the steady state situation, without drift or modulation, the addition of PHF and PHR will equal PHV and PHE will be zero.

FIG. 5 illustrates a block diagram of an ADPLL 80 designed to work off both falling and rising edges of FREF. In this embodiment, the control word FCW from FIG. 4a is halved, since it will be accumulated twice per FREF clock cycle (as shown by the retimed signal CKRx2, which is at 50 twice the CKR frequency). The variable phase circuit 66 is also sampled twice per FREF cycle. The fractional phase errors are computed using a rising fractional phase circuit 64a and a falling fractional phase circuit **64***b*. The rising fractional phase circuit determines a phase error on the rising edge of 55 FREF and the falling fractional phase circuit determines an intermediate phase error on the falling edge of FREF. On the rising edge of FREF, the output of the rising fractional phase error circuit **64***a* is passed to adder **68** for the determination of PHE, similar to that described in connection with FIGS. 4a-b. 60 On the falling edge of FREF, the intermediate phase error  $\phi_2$ is added to the fractional portion of the offset error  $\Delta \phi$  (which could be greater than one). The sum is then added to the integer portion of the offset error  $\Delta \phi$  to provide  $\phi_2$ . This sum is passed to adder 68 for the computation of PHE. Alternatively,  $\Delta \phi$  could be added to  $\phi_2$ , so long as the fractional part of  $\Delta \phi$  is not compromised by a large value of  $\Delta \phi$ .

6

FIG. 6 illustrates a time-to-digital converter (TDC) 90 for measuring a fractional delay between CKV and FREF. Such a circuit may be used as the rising or falling fractional phase circuits 64a and 64b. The CKV signal passes through a string of inverters 92. Each inverter (or other logic device) 92 features a known time delay, for example, approximately 20 psec using Texas Instruments' (C035) of 0.08  $\mu$ m L-effective CMOS process. On the active (rising) edge of FREF, a corresponding set of registers 94 capture the timing state output (D(1) . . . D(L)) of each inverter. The output of every other register 94 is inverted to compensate for the inversion by each inverter 92. The outputs (Q(1) . . . Q(L)) of the registers 94 are received by a pseudo-thermometer-code edge detector 96, which outputs the location of a rising edge and a falling edge relative to FREF.

The operation of the circuit is shown in FIG. 7, which shows the Q(1 ... L) values (L=10 in the illustrated embodiment) at the active edge of FREF. In the illustrated example, the falling edge of CKV that immediately precedes FREF is displaced by two inverter delays, while the rising edge of CKV that immediately precedes FREF is displaced by six inverter delays.

While FIG. 5 shows two fractional phase detectors **64***a* and <sup>25</sup> **64***b*, the functions of the two devices could be combined into a single circuit that shares hardware, such as the string of inverters **92** and the psuedo-thermometer code edge detector **96**.

Additional detail on the operation of time-to-digital converter **90** can be found in U.S. Ser. No. 09/608,317, filed Jun. 30, 2000, entitled "Digital Fractional Phase Detector" to Staszewski et al and in U.S. Ser. No. 09/967,275, filed Sep. 28, 2001, entitled "Power Saving Circuitry Using Predictive Logic" to Staszewski et al, both of which are incorporated by reference herein.

FIG. 8 illustrates a block diagram of a second embodiment of a PLL 100 that can use both edges of a reference clock. In this embodiment, FREF is coupled to phase detector 102 (which is responsive to a first active edge of FREF, e.g., the rising edge of FREF) and to phase detector 104 (which is responsive to a second active edge of FREF, e.g., the falling edge of FREF). The output of phase detector 102 is  $\phi_1$  and the output of phase detector 104 is  $\phi_2$ . It is assumed that the phase detectors 102 and 104 hold the output until the next compare event. The two most recent values of  $\phi_1$  and  $\phi_2$  are added by adder 106. The output of adder 106 is  $\phi_E$ ,  $\phi_E$  is passed to the loop filter 40 and to the controllable oscillator 42. The output of controllable oscillator 42 is fed back to the phase detectors 102 and 104.

In operation, the controllable oscillator 42 updates the signal twice per FREF clock cycle, driven by the average of the sum of the most recent outputs of the phase detectors as shown by Table 1. As in the case of FIG. 4a, it is assumed that phase detector 102 compares the rising edge of FREF with the rising edge of CKVD and phase detector 104 compares the falling edge of FREF with the falling edge of CKVD. It would also be possible to compare the edges of FREF with the output CKV. In this case, both the rising edge and falling edge of FREF could be compared to a rising edge of CKV, if N  $(f_{CKV}/f_{FREF})$  was an even integer. If N is an odd integer, rising edges of FREF could be compared to rising edges of CKV and falling edges of FREF would be compared to falling edges of CKV (it would also be possible to compare rising edges of FREF to falling edges of CKV and vice-versa). Another possibility would b to add an offset  $\phi_H$ , as described above.

**7** TABLE 1

| PHASE ERROR CALCULATION                                                              |                                                                                                                                                                                                                                                    |  |  |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Clock cycle                                                                          | $oldsymbol{\phi}_E$                                                                                                                                                                                                                                |  |  |

| n (rising) n (falling) n + 1 (rising) n + 1 (falling) n + 2 (rising) n + 2 (falling) | $\begin{aligned} & \varphi_1(n) + \varphi_2(n-1) \\ & \varphi_1(n) + \varphi_2(n) \\ & \varphi_1(n+1) + \varphi_2(n) \\ & \varphi_1(n+1) + \varphi_2(n+1) \\ & \varphi_1(n+2) + \varphi_2(n+1) \\ & \varphi_1(n+2) + \varphi_2(n+2) \end{aligned}$ |  |  |

FIG. 9 shows a block diagram of a single sampling PLL 110 that calculates a phase error based on detections on both edges of FREF. In this embodiment, FREF is coupled to phase detector 112 and an inverted FREF is coupled to phase detector 114. The output of phase detector 112 is  $\phi_1$  and the output of phase detector 114 is  $\phi_2$ . The two most recent values of  $\phi_1$  and  $\phi_2$  are added by adder 116, but the total is latched by latch 118 only on a single edge of FREF (the rising edge in the illustrated embodiment). The output of latch 118 is  $\phi_E$ .  $\phi_E$  is passed to the loop filter 40 and to the controllable oscillator 42. The output of controllable oscillator 42 is fed back to the phase detectors 112 and 114.

TABLE 2

| PHASE ERROR CALCULATION                        |                                                                                                                       |  |  |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| Clock cycle                                    | $\Phi_E$                                                                                                              |  |  |

| n (rising)<br>n + 1 (rising)<br>n + 2 (rising) | $\begin{aligned} & \phi_1(n) + \phi_2(n-1) \\ & \phi_1(n+1) + \phi_2(n) \\ & \phi_1(n+2) + \phi_2(n+1) \end{aligned}$ |  |  |

This embodiment differs from the embodiment of FIG. 8 in 35 that the phase error driving the controllable oscillator 42 is updated only once per FREF cycle, although phase error contains components of updates performed twice during the FREF signal.

FIG. 10 illustrates a block diagram of a general mobile 40 phone architecture 130. An RF transceiver 132 is coupled to an antenna 134 and a digital baseband circuit 136. The digital baseband circuit 136 is coupled to a memory subsystem 138. In operation, the digital baseband circuitry 136, which can include one or more digital signal processors (DSPs) and 45 general purpose processors, generates the data for transmission over the RF transceiver. As described above, the RF transceiver uses a highly stable FREF signal, typically from a crystal oscillator. An external crystal 137 is coupled to a sync circuit 139 (controlled in software by the digital baseband 50 136) that matches the frequency and phase of the crystal (possibly through a PLL) with a master clock (MCLK), which is embedded in communication data and broadcast to the mobile device 130 by the base stations. In turn, the base stations synchronize their master clock with an even more 55 precise clock signal, such as from a cesium clock, which may be received by the base stations via fiber or satellite communications. The synchronization circuitry 139 can be very complex.

Additionally, there may be several clocks in the digital 60 baseband circuit **136** that run independently of the clocks in the RF transceiver **132**. This can cause significant noise, especially if the RF transceiver circuit were to be fabricated on the same circuit as the digital baseband circuit.

FIG. 11 illustrates a general block diagram of an architecture for the RF portion of a mobile communications device 140 which has significant advantages over the prior art. A

state machine 142 receives modulation and controllable oscillator timing update information (along with optional feedback). State machine information is stored in latch 144, which is clocked at CKVD (a divided clock signal derived from the output CKV). The output of latch 144 is coupled to the digitally controlled oscillator (DCO) 146. The output of DCO 146 is coupled to frequency divider 148. The output of frequency divider 148 is CKVD.

In operation, the CKV signal is may be divided down by several frequency dividers 148 to provide suitable clock signals for devices in both the RF transceiver 132 and the digital baseband circuitry 136. For example, by generating a CKV having a frequency of 2.4 GHz, the signal could be divided to a clock of about 8 MHz for generating data samples for a Bluetooth application and could be divided to a clock of about 100 MHz for generating samples in an 802.11b application. Other divided clock frequencies could be used for purposes other the data symbol generation. Preferably, the frequency dividers divide by a power of two.

FIG. 12 illustrates a more detailed block diagram of a first embodiment of the RF portion of the mobile communication device 140. In this embodiment, symbols from the digital baseband circuitry 136 (see FIG. 10) are received by data transmit modulation circuit 150. Data from the data transmit modulation circuit 150 is output to state machine 142 and to digital-to-analog converter (DAC) 152, if amplitude modulation is being used. The output of DAC 152 drives power amplifier 154, which is coupled to the output (CKV) of DCO **146**. CKV is also output to frequency divider **148***a*, as well as - 30 to phase detector **156**. The output of frequency divider **148***a* (CKVD1) is coupled to frequency dividers 148b and 148c, which output signals CKVD2 and CKVD3, respectively. CKVD2 clocks DAC 152 and is also output to the data transmit modulation circuit 150 and to digital baseband circuitry 136. CKVD3 clocks latch 158 at the output of phase detector 156. The output of latch 158 is coupled to state machine 142.

In operation, the data modulation circuit creates sample points based on the symbols received from the digital baseband circuit 136. In the prior art, a "chip clock" is used to generate these samples at a desired frequency. In general, the chip clock is a multiple of the reference clock and requires a clock generation circuitry, such as a PLL to generate a higher frequency clock from the reference clock. In the illustrated embodiment, however, a clock derived from the output of the DCO 146 (i.e., CKVD2) is used for the chip clock, by dividing the output of the DCO. A data modulation circuit of this type is disclosed in U.S. Ser. No. 10/001,448 to Staszewski et al, entitled "Transmit Filter", filed Oct. 31, 2001, which is incorporated by reference herein. An apparent data rate can be adjusted by dynamically changing the oversampling ratio of the transmit filter.

Any number of clock frequencies could be generated from CKV. These clocks could be used in the various parts of a device, in particular in the digital baseband circuit 136 and throughout the RF transceiver 132, eliminating multiple clock generation circuits. Additionally, using clocks generated from CKV in both the baseband circuit 136 and in the RF transceiver 132 provides many significant advantages. For example, since the clocks in the two subsystems are interrelated, operations occurring in the digital baseband circuit 136 could be timed to cause the least possible spurious noise in the RF transceiver 132.

FIG. 13 illustrates a second embodiment, similar to that of FIG. 12, where a single clock CKVD2 is used for both timing updates through the phase detector 156 and for data modulation through data transmit modulation circuit 150. In this embodiment,  $\phi_E$  is generated by the phase detector 156 and

passed to adder 160 such that a single number for data modulation and timing updates is passed to state machine 142.

A value  $\Delta$ , an integer indicating a relative position of the CKVD2 clock to the free-running FREF frequency reference, is passed back to the digital baseband circuit **136** where it may 5 be used for synchronization, framing, timing adjustment of the fractional rate of the modulating data, and phase/frequency adjustment of the synthesized RF frequency with MCLK. FREF can now operate in a free-running mode (i.e., not adjusted by MCLK). The master clock MCLK synchronization circuit would now perform adjustment of the center frequency of the RF oscillator, rather than adjust FREF. Adjustments to the center frequency can be made by adjustments to  $\phi_E$ . Since FREF is a very stable clock and since MCLK updates are infrequent, adjustments are very small 15 and occur over long periods of time.

In FIGS. 12 and 13, the phase detection circuits are clocked by a signal that is a division of CKV. Instead of using CKR, which is the FREF clock retimed to CKV clock (see FIG. 5), as the system clock, a power-of-two division (or any other 20 division) of CKV could be used as the system clock. Comparison events in the phase detector would be triggered by the FREF clock in which the clock timing delay is obtained by time-to-digital converters (see FIG. 6) and the result used to perform phase value adjustment.

As can be seen in FIGS. 12 and 13, some or all of the frequency dividers 148 are controlled by a modulus control (MC) signal. This signal is used to indicate a divisor. For example, for a divide-by-8/9 frequency divider, MC=8/9. MC could vary dynamically during operation of the device in 30 order to obtain a fractional division ratio.

Although the Detailed Description of the invention has been directed to certain exemplary embodiments, various modifications of these embodiments, as well as alternative embodiments, will be suggested to those skilled in the art. The 35 invention encompasses any modifications or alternative embodiments that fall within the scope of the claims.

The invention claimed is:

- 1. A phase locked loop circuit, comprising:

- a controllable oscillator for generating an output signal of 40 desired frequency;

- a first phase detection circuit for generating an output indicative of phase differential responsive to said output signal and a first edge of a reference signal;

- a second phase detection circuit for generating an output 45 indicative of phase differential responsive to said output signal and a second edge of the reference signal;

- circuitry for adjusting the output of said second phase detection circuit to account for a variation of said reference signal from a 50% duty cycle; and

- circuitry for controlling said controllable oscillator responsive to said outputs of said first and second phase detections circuits.

- 2. A phase locked loop circuit, comprising:

- a controllable oscillator for generating an output signal of 55 desired frequency;

- a first phase detection circuit for generating an output indicative of phase differential responsive to said output signal and a first edge of a reference signal;

- a second phase detection circuit for generating an output 60 indicative of phase differential responsive to said output signal and a second edge of the reference signal; and

- circuitry for controlling said controllable oscillator responsive to said outputs of said first and second phase detections circuits, wherein said outputs of said first and second phase detection circuits are added on each edge of said reference signal.

10

- 3. A phase locked loop circuit, comprising:

- a controllable oscillator for generating an output signal of desired frequency;

- a first phase detection circuit for generating an output indicative of phase differential responsive to said output signal and a first edge of a reference signal;

- a second phase detection circuit for generating an output indicative of phase differential responsive to said output signal and a second edge of the reference signal; and

- circuitry for controlling said controllable oscillator responsive to said outputs of said first and second phase detections circuits, wherein said outputs of said first and second phase detection circuits are added on a predetermined edge of said reference signal.

- 4. A phase locked loop circuit, comprising:

- a controllable oscillator for generating an output signal of desired frequency;

- a first phase detection circuit for generating an output indicative of phase differential responsive to said output signal and a first edge of a reference signal;

- a second phase detection circuit for generating an output indicative of phase differential responsive to said output signal and a second edge of the reference signal; and

- circuitry for controlling said controllable oscillator responsive to said outputs of said first and second phase detections circuits, wherein said first detection circuit generates an output responsive to the output signal and a rising edge of said reference signal and said second detection circuit generates an output responsive to the output signal and a falling edge of said reference signal.

- 5. A phase locked loop circuit, comprising:

- a controllable oscillator for generating an output signal of desired frequency;

- a first phase detection circuit for generating an output indicative of phase differential responsive to said output signal and a first edge of a reference signal;

- a second phase detection circuit for generating an output indicative of phase differential responsive to said output signal and a second edge of the reference signal; and

- circuitry for controlling said controllable oscillator responsive to said outputs of said first and second phase detections circuits wherein said first detection circuit generates an output responsive to the output signal and a falling edge of said reference signal and said second detection circuit generates an output responsive to the output signal and a rising edge of said reference signal.

- 6. A phase locked loop circuit, comprising:

- a controllable oscillator for generating an output signal of desired frequency;

- a first phase detection circuit for generating an output indicative of phase differential responsive to said output signal and a first edge of a reference signal;

- a second phase detection circuit for generating an output indicative of phase differential responsive to said output signal and a second edge of the reference signal; and

- circuitry for controlling said controllable oscillator responsive to said outputs of said first and second phase detections circuits, wherein said first and second phase detection circuits comprise a time-to-digital converter for generating a digital value indicative of said phase differential

- 7. The phase locked loop circuit of claim 6 wherein said digital value has a fractional part and an integer part.

- 8. The phase locked loop circuit of claim 6 and further comprising circuitry for adjusting the output of said second phase detection circuit to account for a variation of said reference signal from a 50% duty cycle.

- 9. The phase locked loop circuit of claim 6 wherein said outputs of said first and second phase detection circuits are added on each edge of said reference signal.

- 10. The phase locked loop circuit of claim 6 wherein said outputs of said first and second phase detection circuits are 5 added on a predetermined edge of said reference signal.

- 11. The phase locked loop circuit of claim 6 wherein said first detection circuit generates an output responsive to the output signal and a rising edge of said reference signal and said second detection circuit generates an output responsive 10 to the output signal and a falling edge of said reference signal.

- 12. The phase locked loop circuit of claim 6 wherein said first detection circuit generates an output responsive to the output signal and a falling edge of said reference signal and said second detection circuit generates an output responsive 15 to the output signal and a rising edge of said reference signal.

- 13. The phase locked loop circuit of claim 6 wherein said first and second phase detection circuits comprise a time-to-digital converter for generating a digital value indicative of said phase differential.

- 14. The phase locked loop circuit of claim 13 wherein said digital value has a fractional part and an integer part.

- **15**. A method of synthesizing a frequency in a phase locked loop circuit, comprising:

generating a first phase differential output responsive to 25 said output signal and a first edge of a reference signal; generating a second phase differential output responsive to said output signal and a second edge of a reference signal; and

12

controlling a controllable oscillator responsive to said outputs of said first and second phase detections circuits.

- 16. The method of claim 15 further comprising adjusting the output of said second phase detection circuit to account for a variation of said reference signal from a 50% duty cycle.

- 17. The method of claim 15 wherein said outputs of said first and second phase detection circuits are added on each edge of said reference signal.

- **18**. The method of claim **15** wherein said outputs of said first and second phase detection circuits are added on a predetermined edge of said reference signal.

- 19. The method of claim 15 wherein said first detection circuit generates an output responsive to the output signal and a rising edge of said reference signal and said second detection circuit generates an output responsive to the output signal and a falling edge of said reference signal.

- 20. The method of claim 15 wherein said first detection circuit generates an output responsive to the output signal and a falling edge of said reference signal and said second detection circuit generates an output responsive to the output signal and a rising edge of said reference signal.

- 21. The method of claim 15 wherein said first and second phase detection circuits comprise a time-to-digital converter for generating a digital value indicative of said phase differential

- 22. The method of claim 21 wherein said digital value has a fractional part and an integer part.

\* \* \* \* \*