US007714665B2

## (12) United States Patent

## Waheed et al.

## (54) HARMONIC CHARACTERIZATION AND CORRECTION OF DEVICE MISMATCH

- (75) Inventors: Khurram Waheed, Acton, MA (US); Robert B. Staszewski, CD Delft (NL)

- (73) Assignee: Texas Instruments Incorporated, Dallas, TX (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 224 days.

This patent is subject to a terminal disclaimer.

- (21) Appl. No.: 11/618,605

- (22) Filed: Dec. 29, 2006

## (65) **Prior Publication Data**

US 2007/0188244 A1 Aug. 16, 2007

## **Related U.S. Application Data**

- (60) Provisional application No. 60/774,107, filed on Feb. 16, 2006.

- (51) Int. Cl. *H03L 7/099*

(2006.01)

See application file for complete search history.

#### (56) **References Cited**

#### U.S. PATENT DOCUMENTS

6,753,738 B1\* 6/2004 Baird ..... 331/25

# (10) Patent No.: US 7,714,665 B2 (45) Date of Patent: \*May 11, 2010

| 7,046,098 | B2 * | 5/2006  | Staszewski 331/ | 158 |

|-----------|------|---------|-----------------|-----|

| 7,148,760 | B2 * | 12/2006 | Vaananen 331    | /25 |

## (Continued)

## OTHER PUBLICATIONS

T.Pittorino et al., "A UMTS-Compliant Fully Digitally Controlled Oscillator with 100MHz Fine-Tuning Range in 0.13um CMOS," ISSCC 2006, pp. 210-211, 649, Feb. 6-9, 2006.

Staszewski et al., "A First Multigigahertz Digitally Controlled Oscillator for Wireless Applications," IEEE Trans. Microwave Theory and Techniques, vol. 51, No. 11, Nov. 2003, pp. 2154-2164.

Primary Examiner-Robert Pascal

Assistant Examiner—Ryan J Johnson (74) Attorney, Agent, or Firm—Ronald O. Neerings; Wade James Brady, III; Frederick J. Telecky, Jr.

## (57) ABSTRACT

An apparatus and method fore harmonic characterization and ratio correction of device mismatch between coarse and fine varactor tuning devices within a segmented unified varactor bank of an (RF) digitally controlled oscillator (DCO). The DCO is divided into an MSB bank, LSB bank and sigma-delta (SD-LSB) bank. Any ratio mismatches between MSBs and LSBs are digitally calibrated out using a DCO step-size predistortion scheme wherein LSB steps are adjusted to account for ratio mismatch between the MSB/LSB step sizes. A harmonic characterization technique is used to estimate the mismatches in the minimal size CMOS tuning varactors of a digitally controlled RF oscillator (DCO), wherein nominal ratio mismatch between the MSB and LSB devices is estimated using hybrid stochastic gradient DCO gain estimation algorithms. The nominal ratio mismatch and the mismatches in MSB and LSB banks are used to determine average MSB/ LSB mismatch which is then used to correct the LSB steps.

## 26 Claims, 11 Drawing Sheets

331/177 V

## U.S. PATENT DOCUMENTS

| 7,439,817 B2*   | 10/2008 | Waheed et al 331/16      |

|-----------------|---------|--------------------------|

| 2003/0133522 A1 | 7/2003  | Staszewski et al 375/345 |

| 2004/0146132 A1 | 7/2004  | Staszewski et al 375/376 |

| 2006/0033582 A1  | 2/2006 | Staszewski et al 331/16 |

|------------------|--------|-------------------------|

| 2007/0188243 A1* | 8/2007 | Waheed et al 331/16     |

| 2008/0042756 A1* | 2/2008 | Waheed et al 331/16     |

\* cited by examiner

(PRIOR ART)

Sheet 2 of 11

US 7,714,665 B2

**U.S.** Patent

May 11, 2010 Sheet 6 of 11

EFFECT OF TRACKING BANK VARACTOR MISMATCH ON TRANSMITTER RSM PHASE ERROR

**U.S.** Patent

May 11, 2010 Sheet 11 of 11

## HARMONIC CHARACTERIZATION AND CORRECTION OF DEVICE MISMATCH

## REFERENCE TO PRIORITY APPLICATION

This application claims priority to U.S. Provisional Application Ser. No. 60/774,107, filed Feb. 16, 2006, entitled "Frequency Tuning Range Extension and Modulation Resolution Improvement of a Digitally Controlled Oscillator", incorporated herein by reference in its entirety.

## FIELD OF THE INVENTION

The present invention relates to the field of data communications and more particularly relates to an apparatus for and 15 method of harmonic characterization and correction of device mismatch within a segmented unified varactor bank of a radio frequency (RF) digitally controlled oscillator (DCO).

## BACKGROUND OF THE INVENTION

Modern radio frequency (RF) CMOS designers are facing new integration and characterization paradigms due to the coexistence of traditional analog RF wireless designs with digital base-band signal processors and power management 25 on the same physical die. While deep-submicron CMOS processes present new integration opportunities on one hand, they make it extremely difficult to implement high fidelity traditional analog circuits, on the other. The latest CMOS technology parameters are optimized for low cost digital 30 designs only. This forces the analog and mixed-signal designers, using these technologies, to make multi-dimensional trade-offs. The conflicting requirements of area, power and performance in the modern wireless cellular handsets force the designer to intelligently budget parameters such as noise, 35 linearity, gain, supply voltage, signal headroom, impedance, power leakage and dissipation. The inability of SPICE models and other simulators to model the complete RF operational environment mandates several expensive design and fabrication iterations before arriving at a production worthy 40 solution. Although device modeling has recently benefited greatly from the advances in the computational modeling techniques, rapid scaling of technology as well as architectural requirements and device-level innovations appear to hamper the modeling accuracy faster.

Historically, analog circuits have lagged in production ramping behind digital circuitry by more than one CMOS generation, failing to utilize the full potential of new processes or to comply with the new supply-voltage scaling. The quandary of poor characterization leads to substantial conser- 50 vatism in initial analog designs. This leads to expensive cost of design iterations, thus resulting in circuits that do not exploit the raw speed of the latest technology. For example, precise frequency tuning of a low-voltage deep-submicron CMOS digitally-controlled oscillator is an extremely chal- 55 lenging task due to its highly nonlinear frequency versus voltage characteristics. Low-voltage headroom also makes it susceptible to the substrate and the power/ground supply noise. Furthermore, it is extremely difficult to guarantee correct output DCO frequency and tuning step without accurate 60 data on the constituent tuning devices, parasitics and device variation across process, voltage and temperature.

Sometimes, the task is further complicated by the difficulty in even making reliable laboratory measurements due to the accuracy issues caused by probing noise, minuscule device 65 sizing, dynamic effects and loading. Some key device characteristics of the DCO, for example, capacitor mismatch,

thermal and flicker (1/f) noise contributions are quite difficult to measure accurately. For small capacitors used in most analog circuits, generally in the range of 0.1-1 picofarads, direct measurement would possess many uncertainties resulting from parasitics in the physical test setup. Varactors built in CMOS technology are even smaller, typically in the attofarad to femtofarad range. These varactors also suffer from a relatively low quality factor and exhibit substantial series resistance due to the n-well material. All these attributes render the

characterization of varactors extremely difficult.

Further, good quality control of CMOS fabrication is a prerequisite to the mass production of wireless standard specification-compliant transmitters. The amount of mismatch, in the smallest sized DCO bank varactors used for frequency command tracking, is critical to the performance of ADPLL based transceivers due to its direct impact on the spectral purity of the DCO and hence the transceiver built using it.

While digital polar modulated transmitters have been dem-20 onstrated for GGE (GSM.GPRS and EDGE), their usage for 3G remains a daunting task. Polar modulation relies on splitting the digital I/Q baseband input signal into a phase (or its time derivative, frequency) and an amplitude data streams. The differentiated phase signal ( $f=\Delta\theta/\Delta t$ ) is used to directly modulate a digitally controlled oscillator (DCO), the output of which is combined with the amplitude signal (p) in a digital pre-power amplifier (PPA) or digitally-controlled power amplifier (DPA). The  $f=\Delta\theta/\Delta t$  component generated when passing, e.g., the 3.84 MHz WCDMA I/Q signal through a CORDIC transformation algorithm spreads significantly due to the non linear (arctan) operation. It is no longer bandlimited and theoretically infinite modulation of the oscillator is needed to represent this phase signal. Although in a discrete time system, the maximum frequency deviation will be limited to the sampling rate, it is still in the order of tens of megahertz as shown in FIG. 1 for the CORDIC operating at 60 MHz. Given that the DCO can operate at four times the channel frequency, the required modulation is four times that shown in FIG. 1. Any truncation in phase data will degrade Error Vector Magnitude (EVM) and produces spectral regrowth.

Tight modulation resolution has to be maintained in order to keep the frequency quantization noise much lower than electronic or thermal DCO phase noise. In order to satisfy the close-in spectral mask as well as the requisite phase error (or EVM) performance for the GSM/EDGE/WCDMA polar transmitters, any degradation due to the INL and DNL in the DCO has to be avoided.

It is further desirable to have characterization methodologies, which do not penalize the device area budget, do not consume extensive testing time and can be easily ported into the next generations of the CMOS processes with minimal adjustments. Specifically, there is a need for a varactor characterization technique to estimate the mismatches in the tracking bank (i.e., unified bank) tuning varactors of an RF DCO. The DCO being a vital component of the digital radio frequency processor (DRP) technology at the heart of modern GSM/EDGE/UMTS RF transceiver designs.

Once the characterization and calibration of such device mismatches is understood, development of digital circuits that allow for the compensation of such inter-device ratio, random and possibly systematic mismatches is a must.

## SUMMARY OF THE INVENTION

The present invention is a novel apparatus and method of extending the frequency tuning range and improving the modulation resolution of an RF digitally controlled oscillator (DCO). The invention provides a new mechanism of arranging the DCO varactor banks so as to achieve wider modulation tuning range from the DCO in a two-point modulation scheme as done in the polar domain using the DRP based 5 transmitter architecture.

Further, the invention provides a simple, fast and efficient harmonic mismatch characterization technique for the mismatch characterization of the minimal sized varactors in a multi-gigahertz DCO. This technique can be used in conjunction with the techniques discussed in U.S. patent application Ser. No. 11/460,221 to Waheed et al., entitled "Hybrid Stochastic Gradient Based Digital Controlled Oscillator Gain KDCO Estimation," US Patent Publication No. 2003/ 0133522 to Staszewski et al., entitled "All-Digital Frequency 15 Synthesis With DCO Gain Calibration," or US Patent Publication No. 2006/0033582 to Staszewski et al., entitled "Gain Calibration of a Digital Controlled Oscillator," all of which are incorporated herein by reference in their entirety. The proposed technique is amenable to laboratory automation and 20 is suitable for fast characterization of fabrication quality in mass-scale produced RF integrated radios. Further, an example digital circuit is presented to compensate for the possible ratio mismatch in the banks of the transmitter.

For the wide bandwidth DCO comprising a PVT bank (for 25 initial locking) and a single unified bank of varactors (to be used both before and after locking), the unified bank is further divided into an MSB bank, LSB bank and a fractional sigmadelta (SD-LSB) bank. Any mismatches between MSBs and LSBs are digitally calibrated out using a pre-distortion 30 scheme wherein the LSB steps are adjusted to account for the mismatch between the MSB/LSB step sizes. A harmonic calibration technique is used to determine the average MSB/ LSB mismatch. In the simplest scheme, the average mismatch value is used to correct the LSB steps. Note that the ratio 35 between the MSB and LSB devices in the instant embodiment is a function of the fabricated device geometry only and does not depend on temperature, frequency, process and voltage. In this case, the calibration scheme is simplified.

The invention is applicable to any system in which it is 40 desirable to extend the frequency tuning range and improve the modulation accuracy/resolution of a digitally controlled RF oscillator such as employed in mobile phones and other wireless applications. The invention is intended for use in a digital radio transmitter or transceiver but can be used in other 45 applications as well, such as a general communication channel and data converters.

One advantage of the range extension and modulation resolution improvement scheme of the present invention for the enhanced tuning range DCO is that the unified varactor bank 50 permits the use of a fewer number of control lines (e.g., 128+16=144). This results in a more compact circuit layout, minimizing parasitic capacitance. Extremely tight matching can be achieved by design between the MSB and LSB devices ensuring monotonic frequency transition and acceptable INL 55 and DNL. Any mismatch between the LSBs and a particular MSB can be further digitally calibrated using the predistortion scheme of the invention.

Another advantage is that the relatively quick harmonic calibration scheme of the invention can be used to determine 60 the average MSB or LSB device mismatches using a harmonic characterization technique whereas the average MSB/ LSB mismatches can be quickly estimated without extensive laboratory measurements. For the nominal ratio estimation between MSB and LSB devices of the unified bank the 65 KDCO gain estimation techniques described in the cited patent applications can be used. 4

Note that many aspects of the invention described herein may be constructed as software objects that are executed in embedded devices as firmware, software objects that are executed as part of a software application on either an embedded or non-embedded computer system running a real-time operating system such as WinCE, Symbian, OSE, Embedded LINUX, etc. or non-real time operating system such as Windows, UNIX, LINUX, etc., or as soft core realized HDL circuits embodied in an Application Specific Integrated Circuit (ASIC) or Field Programmable Gate Array (FPGA), or as functionally equivalent discrete hardware components.

There is thus provided in accordance with the present invention, an apparatus for correction of varactor mismatch of a single segmented unified tuning bank in a digitally controlled oscillator (DCO), the unified tuning bank having a coarse tuning bank comprising a plurality of coarse tuning devices and a fine tuning bank comprising a plurality of fine tuning devices, the apparatus comprising DCO gain estimation means and harmonic calibration means in combination with the DCO gain estimation means operative to determine a mismatch error value between the coarse tuning devices and the fine tuning devices.

There is also provided in accordance with the present invention, a method of correction of device mismatch of a single segmented unified bank of conversion devices for use in a digital to analog quantity converter (DAC), the unified conversion bank having a coarse bank comprising a plurality of coarse conversion devices and a fine bank comprising a plurality of fine conversion devices, the method comprising the step of performing harmonic characterization of random conversion device mismatches in most significant bit (MSB) and least significant bit (LSB) devices; the step of performing comprising the steps of applying a sinusoidal modulation to the DAC using one or more conversion device banks and estimating random mismatches in the DAC conversion device banks using the level of one or more harmonics in an observable frequency modulated RF spectrum output from the DAC.

There is further provided in accordance with the present invention, a transmitter comprising a frequency synthesizer for performing a frequency modulation; the frequency synthesizer comprising a digitally controlled oscillator (DCO), the DCO comprising a single segmented unified tuning bank comprising a coarse tuning bank comprising a plurality of coarse tuning devices adapted to provide coarse frequency tuning control of the DCO, a fine tuning bank comprising a plurality of fine tuning devices adapted to provide fine frequency tuning control of the DCO and harmonic calibration means for determining an average ratio mismatch error value between the coarse tuning devices and the fine tuning devices.

There is also provided in accordance with the present invention, a method of ratio estimation between coarse and fine varactor tuning devices in a digitally controlled oscillator (DCO), the method comprising the steps of measuring DCO gain (KDCO) for each varactor bank in the DCO to estimate a nominal ratio mismatch between most significant bit (MSB) and least significant bit (LSB) devices, performing harmonic characterization of random varactor mismatches in most significant bit (MSB) and least significant bit (LSB) devices; the step of performing comprising the steps of applying a sinusoidal modulation to the DCO using one or more varactor banks, estimating random mismatches in the DCO varactor banks using the level of one or more harmonics in an observable frequency modulated RF spectrum output from the DCO and computing an average ratio mismatch between most significant bit (MSB) and least significant bit (LSB) devices using the nominal ratio estimate and individual random mismatch estimates measured in each varactor bank.

There is further provided in accordance with the present invention, a transmitter comprising a frequency synthesizer for performing a frequency modulation; the frequency synthesizer comprising a digitally controlled oscillator (DCO), the DCO comprising a single segmented unified tuning bank 5 comprising a coarse tuning bank comprising a plurality of coarse tuning devices adapted to provide coarse frequency tuning control of the DCO, a fine tuning bank comprising a plurality of fine tuning devices adapted to provide fine frequency tuning control of the DCO and means for interfacing 10 the transmitter to a scripts processor, the scripts processor suitably programmed to perform harmonic calibration by determining an average ratio mismatch error value between the coarse tuning devices and the fine tuning devices.

There is also provided in accordance with the present 15 invention, a method of harmonic calibration of random varactor mismatches between most significant bit (MSB) device of an MSB varactor bank and least significant bit (LSB) devices of an LSB varactor bank in a digitally controlled oscillator (DCO), the method comprising the steps of apply- 20 ing a single frequency modulation tone to the DCO and estimating random mismatches in the DCO varactor banks using the level of one or more harmonics in an observable frequency modulated RF spectrum output from the DCO.

## BRIEF DESCRIPTION OF THE DRAWINGS

The invention is herein described, by way of example only, with reference to the accompanying drawings, wherein:

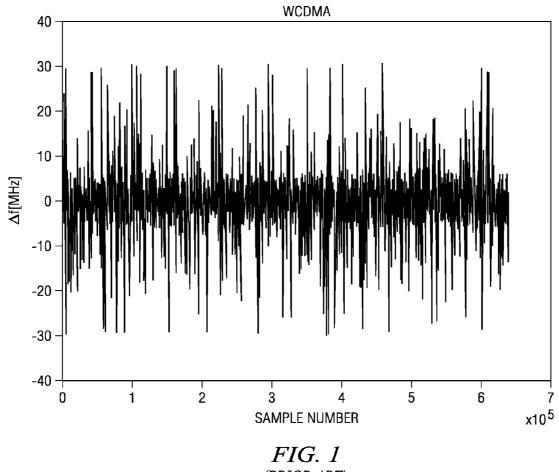

FIG. 1 is a graph illustrating the frequency deviation com-<sup>30</sup> ponent of typical WCDMA modulation with the cordic running at 60 MHz;

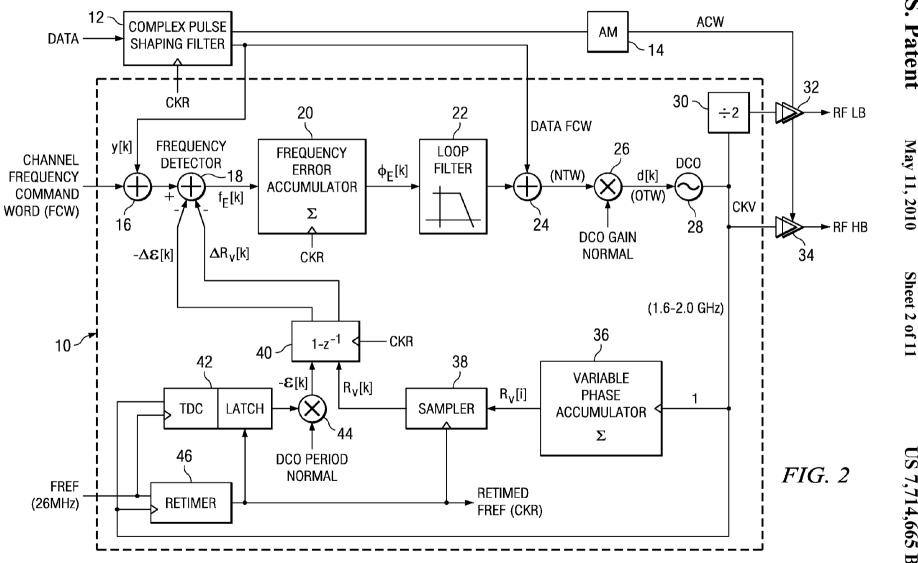

FIG. **2** is a block diagram illustrating an all digital phase locked loop (ADPLL) based polar transmitter constructed in accordance with the present invention; <sup>35</sup>

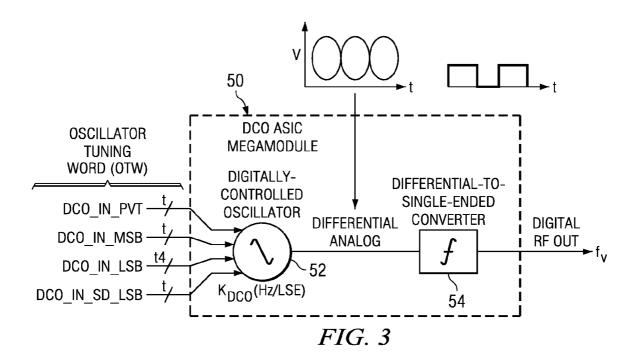

FIG. **3** is a block diagram illustrating a DCO module incorporating digital inputs and outputs;

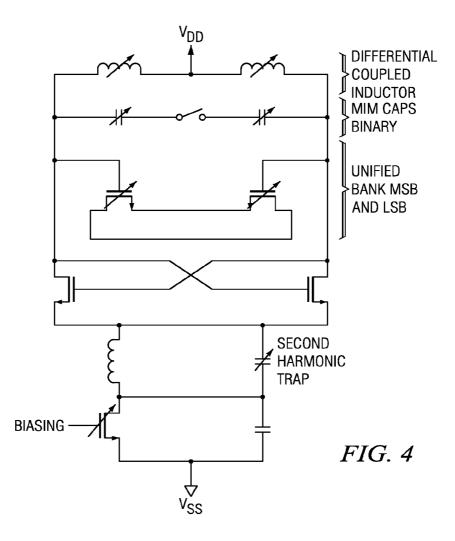

FIG. **4** is a schematic diagram illustrating the DCO core including the tunable capacitance and biasing network;

FIG. **5** is a graph illustrating DCO output frequency and <sup>40</sup> step size as a function of PVT bank bits for a mid MSB and LSB setting;

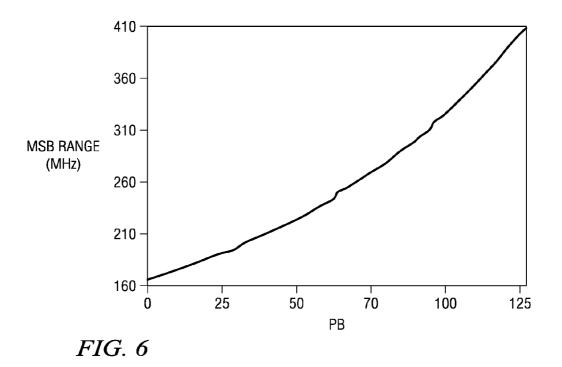

FIG. **6** is a graph illustrating MSB range as a function of PVT bank bits for a mid MSB setting;

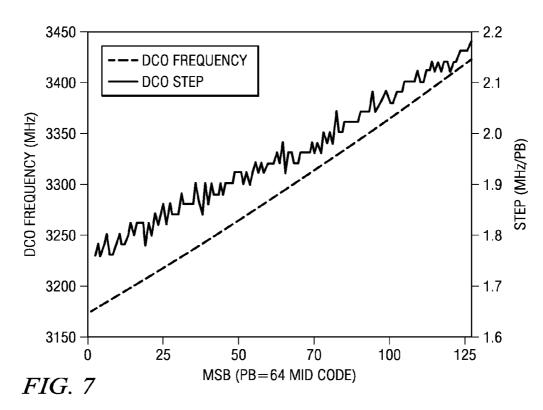

FIG. 7 is a graph illustrating DCO output frequency and <sup>45</sup> LSB step size for LSB (0-15) and MSB (60-68) sweep for a fixed PVT setting;

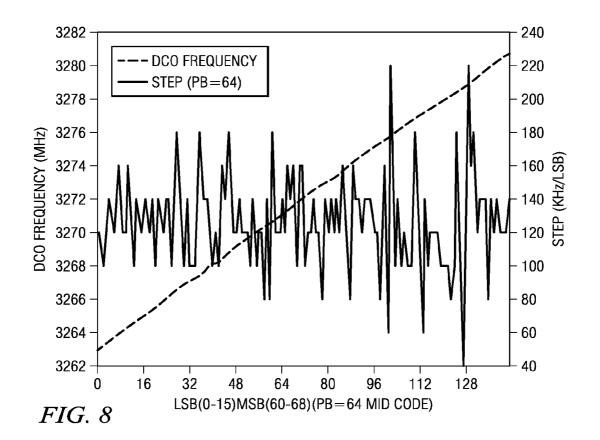

FIG. **8** is a graph of the DCO output frequency and step size versus DCO frequency command code;

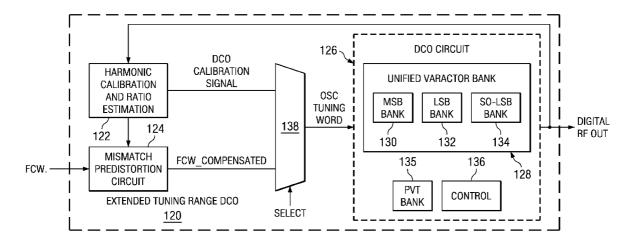

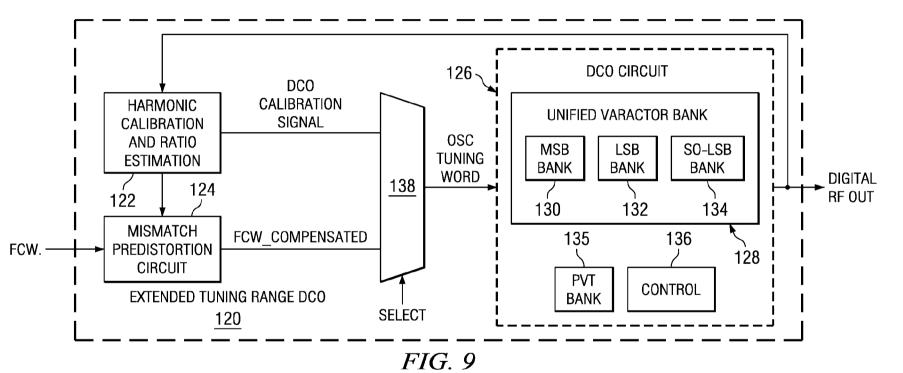

FIG. 9 is a block diagram illustrating the extended tuning range and enhanced resolution DCO circuit designed in accordance with the present invention;

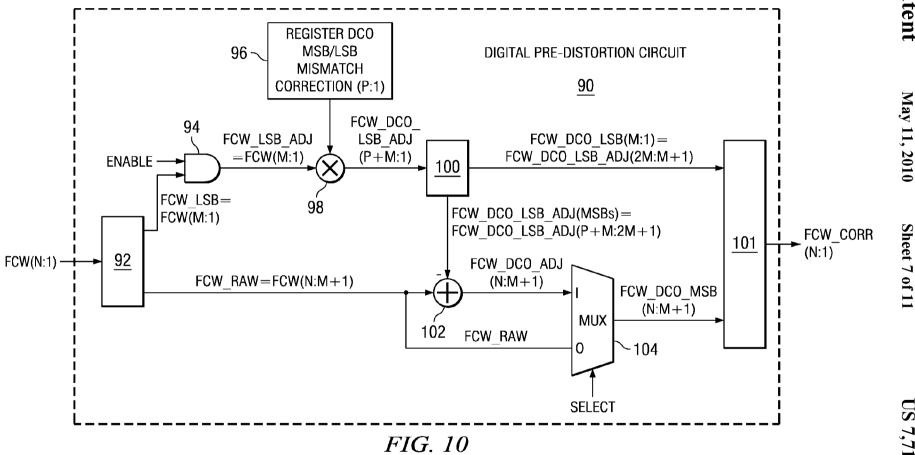

FIG. **10** is a block diagram illustrating the digital predistortion circuit for countering DCO MSB/LSB mismatch constructed in accordance with the present invention; <sup>55</sup>

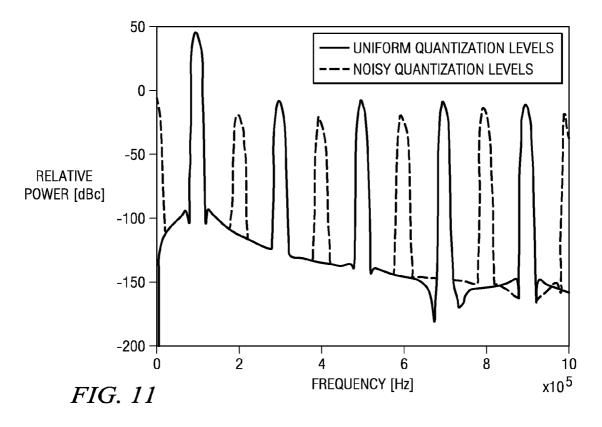

FIG. **11** is a graph illustrating the spectrum for uniform and noisy quantization levels in harmonic characterization of varactor mismatches in the DCO;

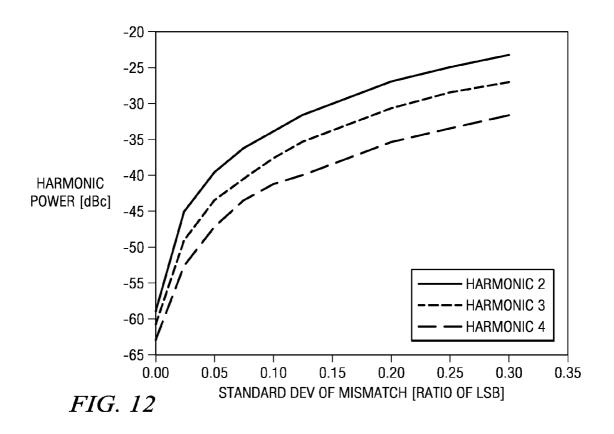

FIG. **12** is a block diagram illustrating the effects of the <sub>60</sub> unified LSB (or tracking) bank varactor mismatch on frequency modulation harmonics using a 203 kHz sine wave modulating tone;

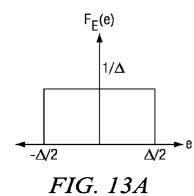

FIG. **13**A is a diagram illustrating the quantization density function for an ideal uniform quantization;

65

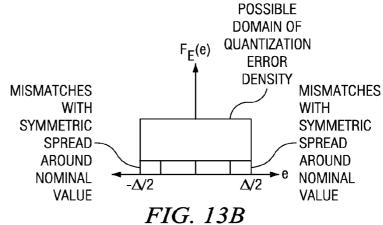

FIG. **13**B is a diagram illustrating the quantization density functions for a quantizer with noisy quantization levels;

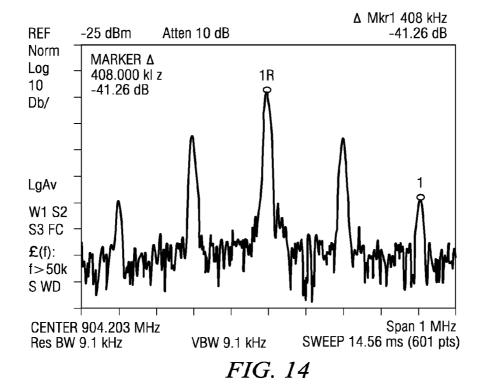

FIG. **14** is a graph illustrating laboratory measurements taken on a physical GSM transceiver chip demonstrating the benefits of the present invention;

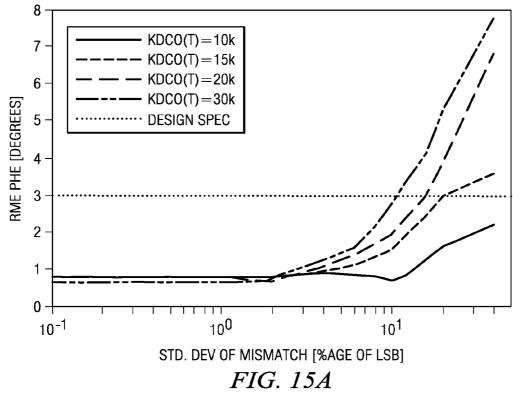

FIG. **15**A is a graph illustrating the RMS Phase Error as a function of DCO varactor mismatches;

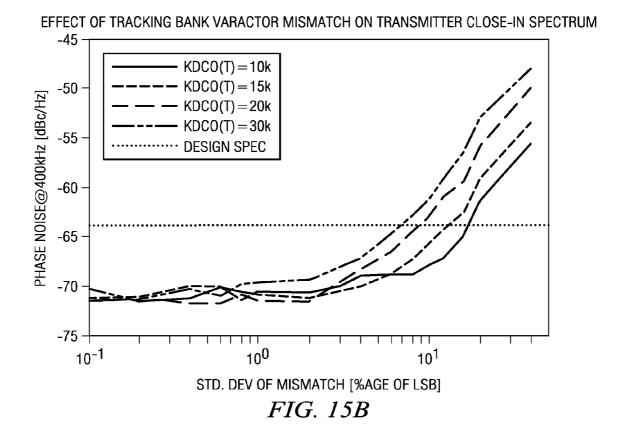

FIG. **15**B is a graph illustrating the Modulated Phase Spectrum at 400 kHz as a function of DCO varactor mismatches; and

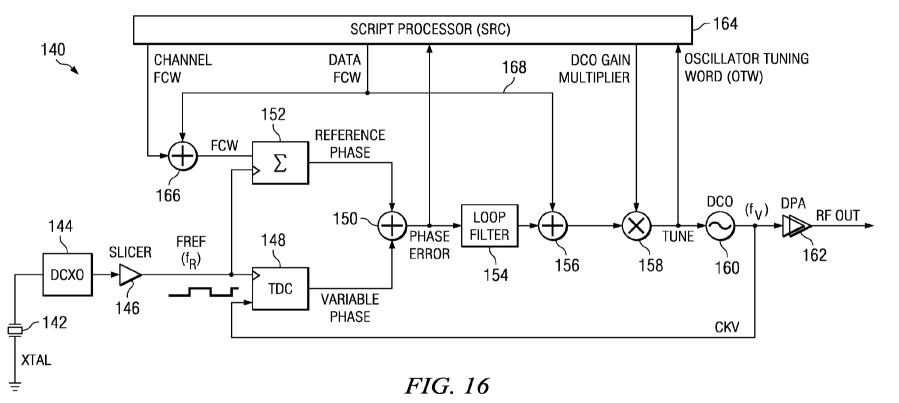

FIG. **16** is a block diagram illustrating the ADPLL setup for BIST using the script processor based on monitoring of the DCO tuning word and digital phase error signals.

## DETAILED DESCRIPTION OF THE INVENTION

## Notation Used Throughout

The following notation is used throughout this document.

| ABAcquisition BankACLRAdjacent Channel Leakage RatioADPLLAll Digital Phase Locked LoopASICApplication Specific Integrated CircuitBISTBuilt-In Self TestCKRRetimed Reference ClockCKVVariable Oscillator ClockCMOSComplementary Metal Oxide SemiconductorDCODigitally Controlled OscillatorDCSDigital Cellular SystemDNLDifferential Non-LinearityDPADigitally-Controlled Power AmplifierDRPDigital RF Processor or Digital Radio ProcessorEDGEEnhanced Data rates for GSM EvolutionEVMError Vector MagnitudeFCWFrequency Command WordFPGAField Programmable Gate ArrayFREFFrequency ReferenceGGEGSM, GPRS and EDGEGPRSGeneral Packet Radio ServiceGSMGlobal System for Mobile CommunicationsHBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersINLIntegral Non-LinearityLBLow BandLSBMost Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase NoisePVTPro | Term     | Definition                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------|

| ADPLLAll Digital Phase Locked LoopASICApplication Specific Integrated CircuitBISTBuilt-In Self TestCKRRetimed Reference ClockCKVVariable Oscillator ClockCMOSComplementary Metal Oxide SemiconductorDCODigitally Controlled OscillatorDCSDigital Cellular SystemDNLDifferential Non-LinearityDPADigitally-Controlled Power AmplifierDRPDigital R Processor or Digital Radio ProcessorEDGEEnhanced Data rates for GSM EvolutionEVMError Vector MagnitudeFCWFrequency Command WordFPGAField Programmable Gate ArrayFREFFrequency ReferenceGGEGSM, GPRS and EDGEGPRSGeneral Packet Radio ServiceGSMGlobal System for Mobile CommunicationsHBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegrat Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSEMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase Locked LoopPNPha | AB       | Acquisition Bank                        |

| ADPLLAll Digital Phase Locked LoopASICApplication Specific Integrated CircuitBISTBuilt-In Self TestCKRRetimed Reference ClockCKVVariable Oscillator ClockCMOSComplementary Metal Oxide SemiconductorDCODigitally Controlled OscillatorDCSDigital Cellular SystemDNLDifferential Non-LinearityDPADigitally-Controlled Power AmplifierDRPDigital R Processor or Digital Radio ProcessorEDGEEnhanced Data rates for GSM EvolutionEVMError Vector MagnitudeFCWFrequency Command WordFPGAField Programmable Gate ArrayFREFFrequency ReferenceGGEGSM, GPRS and EDGEGPRSGeneral Packet Radio ServiceGSMGlobal System for Mobile CommunicationsHBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegrat Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSEMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase Locked LoopPNPha | ACLR     | Adjacent Channel Leakage Ratio          |

| BISTBuilt-In Self TestCKRRetimed Reference ClockCKVVariable Oscillator ClockCMOSComplementary Metal Oxide SemiconductorDCODigitally Controlled OscillatorDCSDigitall Cellular SystemDNLDifferential Non-LinearityDPADigitally-Controlled Power AmplifierDRPDigitally-Controlled Power AmplifierDRPDigitally-Controlled Power AmplifierDRPDigitall RF Processor or Digital Radio ProcessorEDGEEnhanced Data rates for GSM EvolutionEVMError Vector MagnitudeFCWFrequency Command WordFPGAField Programmable Gate ArrayFREFFrequency ReferenceGGEGSM, GPRS and EDGEGPRSGeneral Packet Radio ServiceGSMGlobal System for Mobile CommunicationsHBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProc | ADPLL    | All Digital Phase Locked Loop           |

| CKRRetimed Reference ClockCKVVariable Oscillator ClockCMOSComplementary Metal Oxide SemiconductorDCODigitally Controlled OscillatorDCSDigital Cellular SystemDNLDifferential Non-LinearityDPADigitally-Controlled Power AmplifierDRPDigitall RF Processor or Digital Radio ProcessorEDGEEnhanced Data rates for GSM EvolutionEVMError Vector MagnitudeFCWFrequency Command WordFPGAField Programmable Gate ArrayFREFFrequency ReferenceGGEGSM, GPRS and EDGEGPRSGeneral Packet Radio ServiceGSMGlobal System for Mobile CommunicationsHBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorS                   | ASIC     | Application Specific Integrated Circuit |

| CKVVariable Oscillator ClockCMOSComplementary Metal Oxide SemiconductorDCODigitally Controlled OscillatorDCSDigital Cellular SystemDNLDifferential Non-LinearityDPADigitally-Controlled Power AmplifierDRPDigital RF Processor or Digital Radio ProcessorEDGEEnhanced Data rates for GSM EvolutionEVMError Vector MagnitudeFCWFrequency Command WordFPGAField Programmable Gate ArrayFREFFrequency ReferenceGGEGSM, GPRS and EDGEGPRSGeneral Packet Radio ServiceGSMGlobal System for Mobile CommunicationsHBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegrat Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTBTrac                            | BIST     | Built-In Self Test                      |

| CMOSComplementary Metal Oxide SemiconductorDCODigitally Controlled OscillatorDCSDigital Cellular SystemDNLDifferential Non-LinearityDPADigitally-Controlled Power AmplifierDRPDigital RF Processor or Digital Radio ProcessorEDGEEnhanced Data rates for GSM EvolutionEVMError Vector MagnitudeFCWFrequency Command WordFREAFrequency Command WordFREFFrequency ReferenceGGEGSM, GPRs and EDGEGPRSGeneral Packet Radio ServiceGSMGlobal System for Mobile CommunicationsHBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTracking BankTDCTDCTime to Digital Conver                            | CKR      | Retimed Reference Clock                 |

| DCODigitally Controlled OscillatorDCSDigital Cellular SystemDNLDifferential Non-LinearityDPADigitally-Controlled Power AmplifierDRPDigital RF Processor or Digital Radio ProcessorEDGEEnhanced Data rates for GSM EvolutionEVMError Vector MagnitudeFCWFrequency Command WordFPGAField Programmable Gate ArrayFREFFrequency ReferenceGGEGSM, GPRS and EDGEGPRSGeneral Packet Radio ServiceGSMGlobal System for Mobile CommunicationsHBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTacking BankTDCTDCTime to Digital Converter                                                              | CKV      | Variable Oscillator Clock               |

| DCSDigital Cellular SystemDNLDifferential Non-LinearityDPADigitally-Controlled Power AmplifierDRPDigital RF Processor or Digital Radio ProcessorEDGEEnhanced Data rates for GSM EvolutionEVMError Vector MagnitudeFCWFrequency Command WordFPGAField Programmable Gate ArrayFREFFrequency ReferenceGGEGSM, GPRS and EDGEGPRSGeneral Packet Radio ServiceGSMGlobal System for Mobile CommunicationsHBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTacking BankTDCTDCTime to Digital Converter                                                                                                | CMOS     | Complementary Metal Oxide Semiconductor |

| DNLDifferential Non-LinearityDPADigitally-Controlled Power AmplifierDRPDigital RF Processor or Digital Radio ProcessorEDGEEnhanced Data rates for GSM EvolutionEVMError Vector MagnitudeFCWFrequency Command WordFPGAField Programmable Gate ArrayFREFFrequency ReferenceGGEGSM, GPRS and EDGEGPRSGeneral Packet Radio ServiceGSMGlobal System for Mobile CommunicationsHBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTacking BankTDCTDCTime to Digital Converter                                                                                                                          | DCO      |                                         |

| DPADigitally-Controlled Power AmplifierDRPDigital RF Processor or Digital Radio ProcessorEDGEEnhanced Data rates for GSM EvolutionEVMError Vector MagnitudeFCWFrequency Command WordFPGAField Programmable Gate ArrayFREFFrequency ReferenceGGEGSM, GPRS and EDGEGPRSGeneral Packet Radio ServiceGSMGlobal System for Mobile CommunicationsHBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegrated CircuitLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                           | DCS      | Digital Cellular System                 |

| DRPDigital RF Processor or Digital Radio ProcessorEDGEEnhanced Data rates for GSM EvolutionEVMError Vector MagnitudeFCWFrequency Command WordFPGAField Programmable Gate ArrayFREFFrequency ReferenceGGEGSM, GPRs and EDGEGPRSGeneral Packet Radio ServiceGSMGlobal System for Mobile CommunicationsHBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScirpts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                               | DNL      |                                         |

| EDGEEnhanced Data rates for GSM EvolutionEVMError Vector MagnitudeFCWFrequency Command WordFPGAField Programmable Gate ArrayFREFFrequency ReferenceGGEGSM, GPRS and EDGEGPRSGeneral Packet Radio ServiceGSMGlobal System for Mobile CommunicationsHBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                | DPA      |                                         |

| EVMError Vector MagnitudeFCWFrequency Command WordFPGAField Programmable Gate ArrayFREFFrequency ReferenceGGEGSM, GPRS and EDGEGPRSGeneral Packet Radio ServiceGSMGlobal System for Mobile CommunicationsHBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                         | DRP      |                                         |

| FCWFrequency Command WordFPGAField Programmable Gate ArrayFREFFrequency ReferenceGGEGSM, GPRS and EDGEGPRSGeneral Packet Radio ServiceGSMGlobal System for Mobile CommunicationsHBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                  | EDGE     | Enhanced Data rates for GSM Evolution   |

| FPGAField Programmable Gate ArrayFREFFrequency ReferenceGGEGSM, GPRS and EDGEGPRSGeneral Packet Radio ServiceGSMGlobal System for Mobile CommunicationsHBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                           |          | Error Vector Magnitude                  |

| FREFFrequency ReferenceGGEGSM, GPRS and EDGEGPRSGeneral Packet Radio ServiceGSMGlobal System for Mobile CommunicationsHBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                            | FCW      | Frequency Command Word                  |

| GGEGSM, GPRS and EDGEGPRSGeneral Packet Radio ServiceGSMGlobal System for Mobile CommunicationsHBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScirpts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                | FPGA     |                                         |

| GPRSGeneral Packet Radio ServiceGSMGlobal System for Mobile CommunicationsHBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIRInfinite Impulse ResponseINLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                         | FREF     |                                         |

| GSMGlobal System for Mobile CommunicationsHBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |                                         |

| HBHigh BandHDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScipts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |                                         |

| HDLHardware Description LanguageICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |                                         |

| ICIntegrated CircuitIEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |                                         |

| IEEEInstitute of Electrical and Electronic EngineersIIRInfinite Impulse ResponseINLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScipts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |                                         |

| IIRInfinite Impulse ResponseINLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScirpts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |                                         |

| INLIntegral Non-LinearityLBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScipts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |                                         |

| LBLow BandLSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScipts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                         |

| LSBLeast Significant BitMIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScipts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | e ,                                     |

| MIMMetal Insulator MetalMOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScipts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |                                         |

| MOSCAPMetal Oxide Semiconductor CapacitorMSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScipts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |                                         |

| MSBMost Significant BitOTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRSciripts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |                                         |

| OTWOscillator Tuning WordPBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |                                         |

| PBPVT BankPCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |                                         |

| PCSPersonal Communications ServicePDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |                                         |

| PDFProbability Density FunctionPLLPhase Locked LoopPNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScirpts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |                                         |

| PLL     Phase Locked Loop       PN     Phase Noise       PVT     Process, Voltage, Temperature       RF     Radio Frequency       RMS     Root Mean Squared       SCR     Scripts Processor       SD     Sigma-Delta       TB     Tracking Bank       TDC     Time to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |                                         |

| PNPhase NoisePVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |                                         |

| PVTProcess, Voltage, TemperatureRFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |                                         |

| RFRadio FrequencyRMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |                                         |

| RMSRoot Mean SquaredSCRScripts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |                                         |

| SCRScripts ProcessorSDSigma-DeltaTBTracking BankTDCTime to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |                                         |

| SD Sigma-Delta<br>TB Tracking Bank<br>TDC Time to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |                                         |

| TB Tracking Bank<br>TDC Time to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |                                         |

| TDC Time to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | 0                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | UB       | Unified Bank                            |

| UMTS Universal Mobile Telecommunications System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                         |

| OM IS         Oniversal Mobile Telecommunications system           VHDL         VHSIC Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |                                         |

| WCDMA Wideband Code Division Multiple Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |                                         |

| WLAN Wireless Local Area Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |                                         |