US007920081B2

# (12) United States Patent

### Waheed et al.

#### (54) DIGITAL PHASE LOCKED LOOP WITH DITHERING

- (75) Inventors: Khurram Waheed, Plano, TX (US);

Mahbuba Sheba, Richardson, TX (US);

Robert Bogdan Staszewski, Garland, TX (US); Socrates Vamvakos, Richardson, TX (US)

- (73) Assignee: **Texas Instruments Incorporated**, Dallas, TX (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 12/841,354

- (22) Filed: Jul. 22, 2010

#### (65) **Prior Publication Data**

US 2010/0283654 A1 Nov. 11, 2010

#### **Related U.S. Application Data**

- (62) Division of application No. 12/114,726, filed on May 2, 2008, now Pat. No. 7,786,913.

- (60) Provisional application No. 60/945,818, filed on Jun. 22, 2007.

- (51) Int. Cl.

- *H03M 1/06* (2006.01)

## (10) Patent No.: US 7,920,081 B2

### (45) **Date of Patent:** Apr. 5, 2011

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 7,046,098 | B2 * | 5/2006 | Staszewski       | 331/158  |

|-----------|------|--------|------------------|----------|

| 7,483,508 | B2 * | 1/2009 | Staszewski et al | 375/376  |

| 7,570,182 | B2 * | 8/2009 | Sheba et al.     | 341/118  |

| 7,777,576 | B2 * | 8/2010 | Waheed et al.    | . 331/17 |

| 7,786,913 | B2 * | 8/2010 | Waheed et al.    | 341/143  |

|           |      |        |                  |          |

\* cited by examiner

Primary Examiner — Lam T Mai

(74) Attorney, Agent, or Firm—Wade J. Brady, III; Frederick J. Telecky, Jr.

#### (57) **ABSTRACT**

An embodiment of the present invention provides a phase locked loop that operates on clock signals derived from an RF clock signal generated by the phase locked loop. A frequency reference input provides a reference clock. A controllable oscillator generates the RF clock signal. A phase detection circuit operates on the reference clock to provide digital phase error samples indicative of a phase difference between the reference clock and the RF clock. A dithering circuit is coupled to the reference signal and injects a short sequence dither signal into the reference signal in order to overcome quantization noise and thereby improve RMS phase-error detection for integer channels.

#### 11 Claims, 30 Drawing Sheets

Sheet 3 of 30

*FIG.* 7*B*

Sheet 17 of 30

FIG. 20

Sheet 27 of 30

FIG. 24

#### DIGITAL PHASE LOCKED LOOP WITH DITHERING

#### CLAIM OF PRIORITY

This application is a divisional of and incorporates by reference application Ser. No. 12/114,726 filed May 2, 2008, entitled "Digital Phase Locked Loop With Dithering", which claims the benefit of and incorporates by reference U.S. Provisional Application No. 60/945,818 filed Jun. 22, 2007, 10 entitled "Interpolative All-Digital Phase Locked Loop".

#### FIELD OF THE INVENTION

This invention generally relates to the field of control sys- 15 tems and data communications. In particular, it relates to cellular telephony and communication devices such as Bluetooth, WLAN, etc. using all-digital radio frequency (RF) circuitry.

#### BACKGROUND OF THE INVENTION

With each successive cellular phone handset generation, users demand more features in a smaller form factor. Some recent examples include cell phones with integrated Blue- 25 interpolative all-digital phase locked loop (iADPLL) based tooth, GPS, digital camera, and MP3 functionality. Process shrinks help deliver a cost and size advantage for digital designs with relative ease. However, for analog/RF designs, the immaturity of advanced processes comes with design challenges that may outweigh the intended advantage. In a 30 typical handset, 30 to 40% of handset board space is occupied by analog/RF functionality which cannot be re-designed or migrated to the newer process/technology nodes easily, inhibiting vendor ability to cost effectively add features and reduce footprint.

Digital radio has recently allowed the replacement of space consuming analog RF circuitry with much more compact digital circuitry, thereby facilitating the ability to port designs rapidly to more advanced lithographies. Texas Instruments (TI) has proven this concept with its Digital RF Processor 40 (DRPTM) architecture, which it has successfully implemented in production versions of its Bluetooth BRF6xxx transceivers, GSM/GPRS LoCosto TCS23xx transceivers among other chips. DRP implementation is consistent with the ongoing trend toward RF-CMOS in the cellular area, making it 45 attractive in terms of power consumption, cost, and the integration of multiple radios.

Oscillators are a key component in the design of radio frequency (RF) communication systems. The estimation and calibration of the modulation gain of an RF oscillator is 50 of FIG. 2; currently an area of active research. Accurate knowledge of this gain significantly reduces the complexity and increases the performance of the phase-locked loop (PLL) as well as the transmit frequency modulation path. It is particularly beneficial in systems implemented in deep submicron CMOS and 55 based on orthogonal frequency/phase and amplitude (i.e. polar) topology. Estimation of RF oscillator frequencymodulation gain is especially important in low-cost dominantly digital high-volume transceivers. In such systems, the phase locked loop sets the loop bandwidth while the trans- 60 mitter sets the transfer function of the direct frequency modulation path wherein the acceptable gain estimation error ranges from less than 1% for LTE/WCDMA to several percents for EDGE, GSM and Bluetooth, for example.

An all-digital frequency synthesizer architecture built 65 around a digitally controlled oscillator (DCO) that is tuned in response to a digital tuning word (OTW) is described in U.S.

2

Pat. No. 7,046,098 entitled "All-digital frequency synthesis with capacitive re-introduction of dithered tuning information" and is incorporated by reference in its entirety herein. A gain characteristic (K<sub>DCO</sub>) of the digitally controlled oscillator can be determined by observing a digital control word before and after a known change  $\Delta f_{max}$  in the oscillating frequency. This has been described in U.S. patent application Ser. No. 11/460,221 entitled "Hybrid Stochastic Gradient Based Digital Controlled Oscillator Gain K<sub>DCO</sub> Estimation". A portion (TUNE\_TF) of the tuning word can be dithered and the resultant dithered portion can then be applied to a control input of switchable devices within the digitally controlled oscillator.

#### BRIEF DESCRIPTION OF THE DRAWINGS

Particular embodiments in accordance with the invention will now be described, by way of example only, and with  $_{20}$  reference to the accompanying drawings:

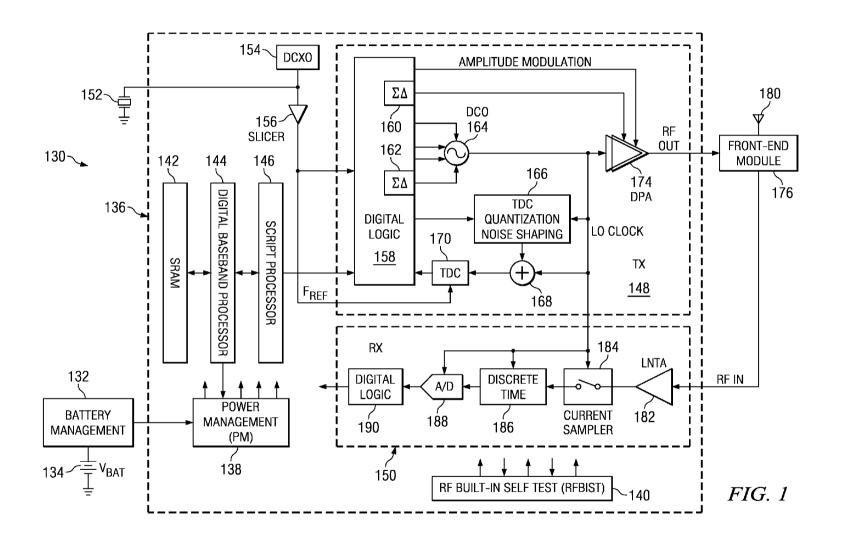

FIG. 1 is a block diagram of a single-chip radio with an all-digital local oscillator and transmitter and a discrete-time receiver;

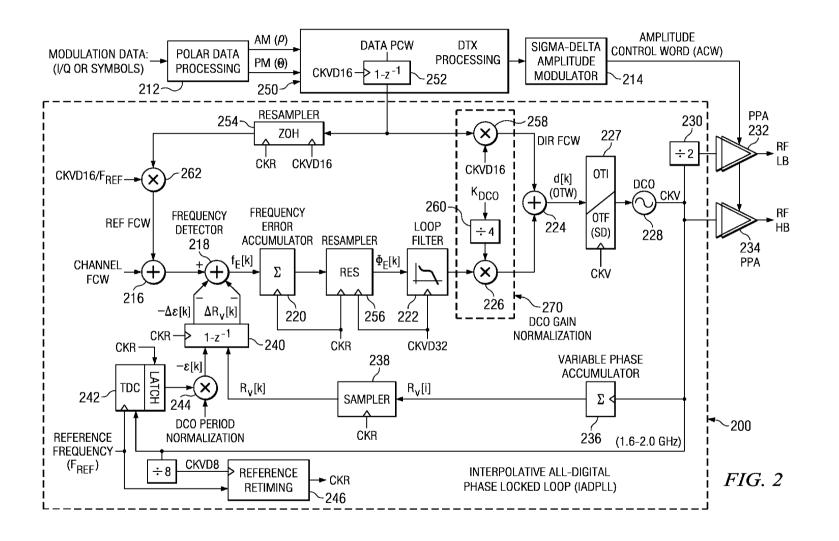

FIG. 2 is a more detailed block diagram illustrating the polar transmitter of FIG. 1 constructed in accordance with the present invention;

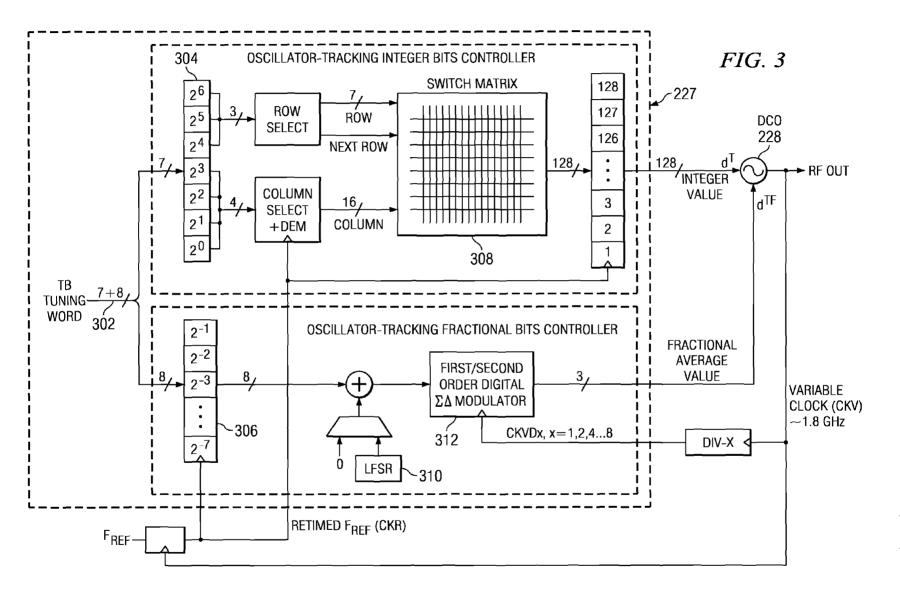

FIG. 3 is a block diagram of the digitally controlled oscillator (DCO) of FIG. 2 illustrating in more detail tracking bits with dynamic element matching (DEM) of the integer part and sigma-delta (SD) dithering of the fractional part;

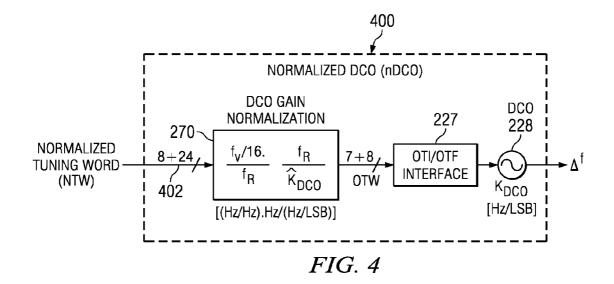

FIG. 4 is a normalized abstraction layer of the DCO of FIG. 3;

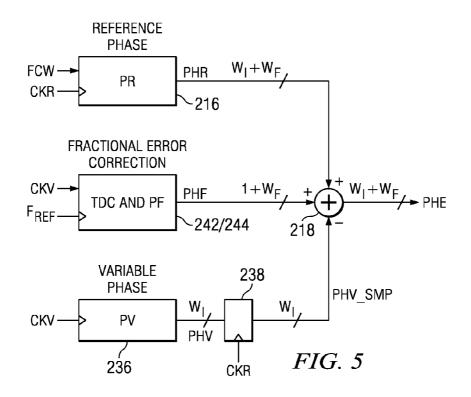

FIG. 5 illustrates a general block diagram of a phase detec-35 tion mechanism used in the iADPLL of FIG. 2;

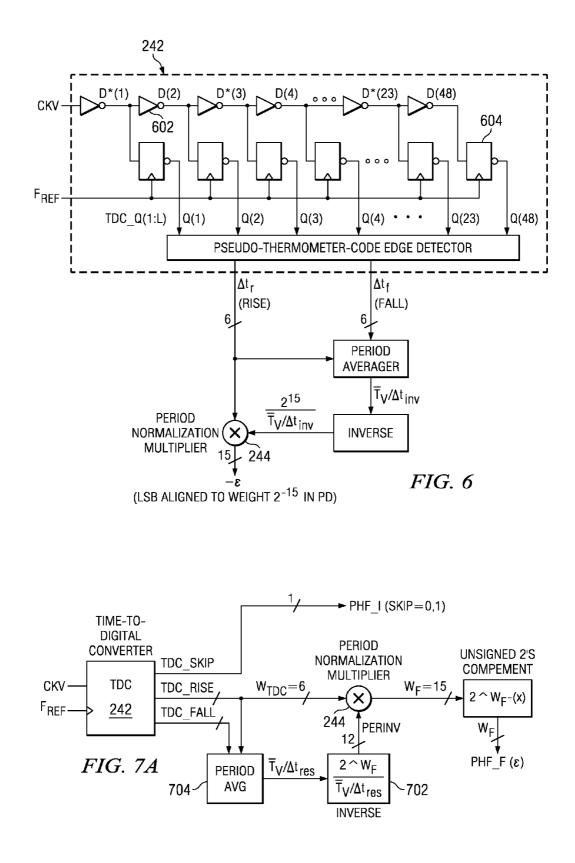

FIG. 6 is a block diagram of the time-to-digital converter (TDC) of FIG. 2;

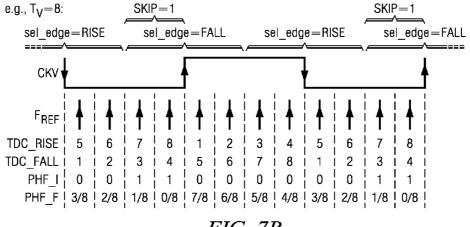

FIGS. 7A and 7B illustrate normalization and edge skipping operation of the TDC;

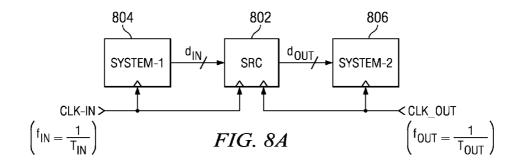

FIGS. 8A and 8B illustrate a conceptual view of data resampling using a sample rate converter;

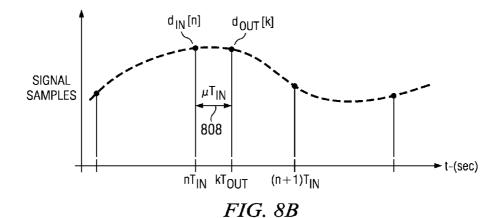

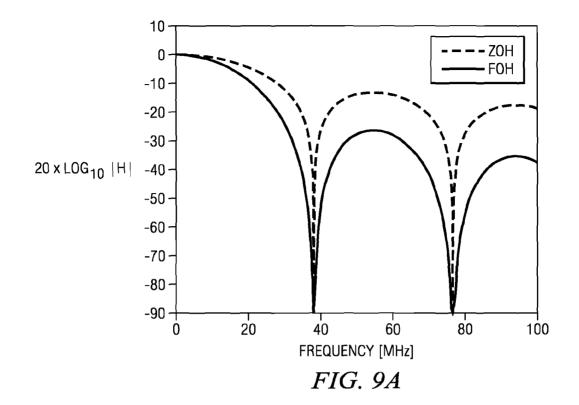

FIG. 9A is a magnitude response plot and FIG. 9B is a phase response plot for the zero-order hold (ZOH) and firstorder hold (FOH) resamplers of the iADPLL of FIG. 2;

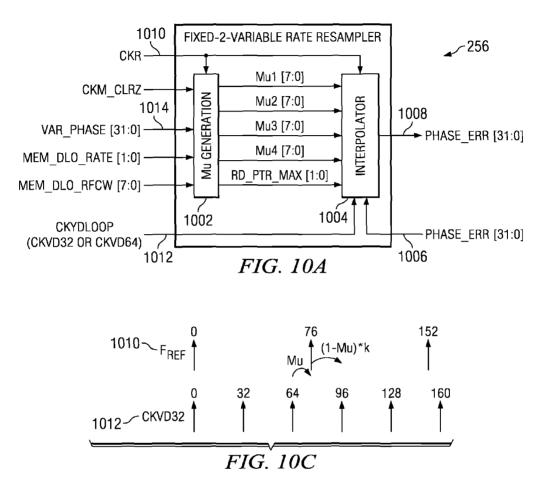

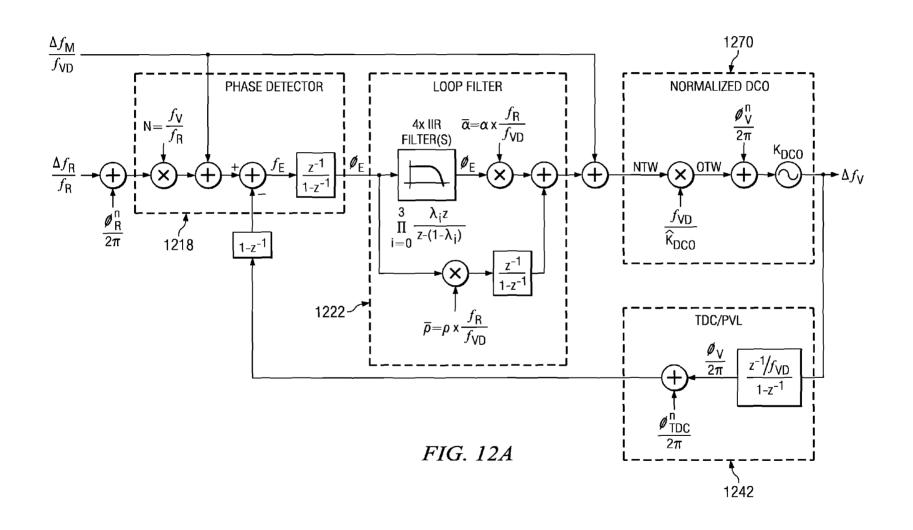

FIG. 10A is a simple block diagram and FIG. 10B is a more detailed schematic of the phase error resampler of FIG. 2;

FIG. 10C illustrates Mu generation between CKVD32 and FREF in the resampler of FIG. 10A;

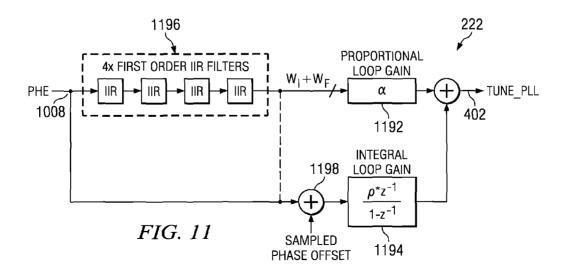

FIG. 11 is a block diagram of the loop filter for the iADPLL

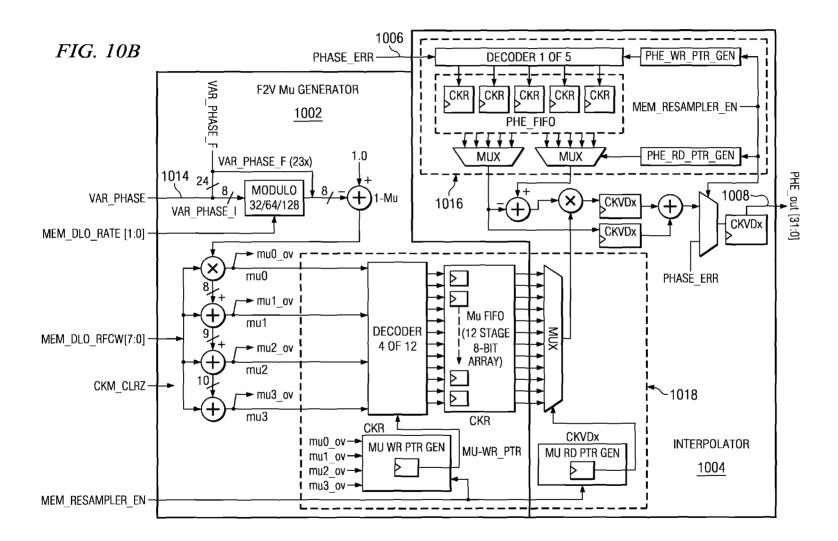

FIG. 12A is a z-domain block diagram for the iADPLL with all iADPLL operations shown at  $f_{VD}$ ;

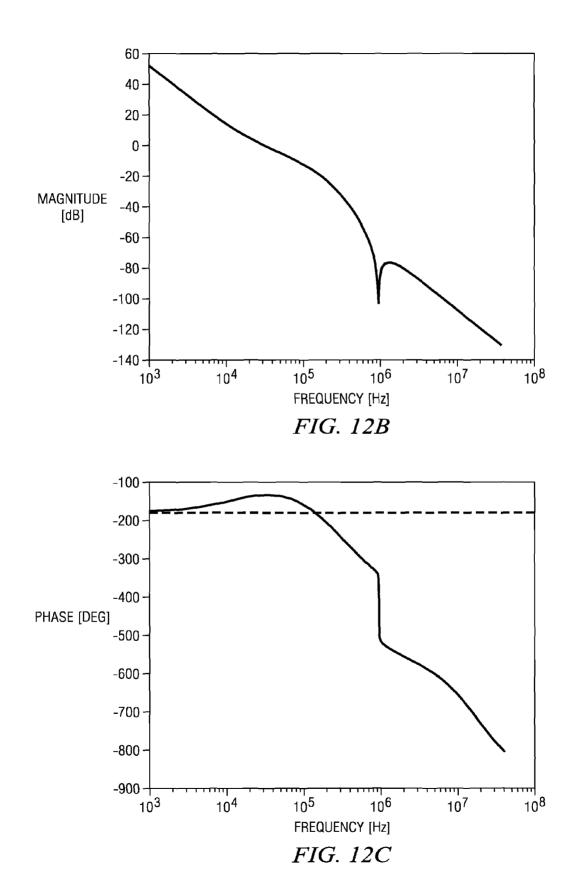

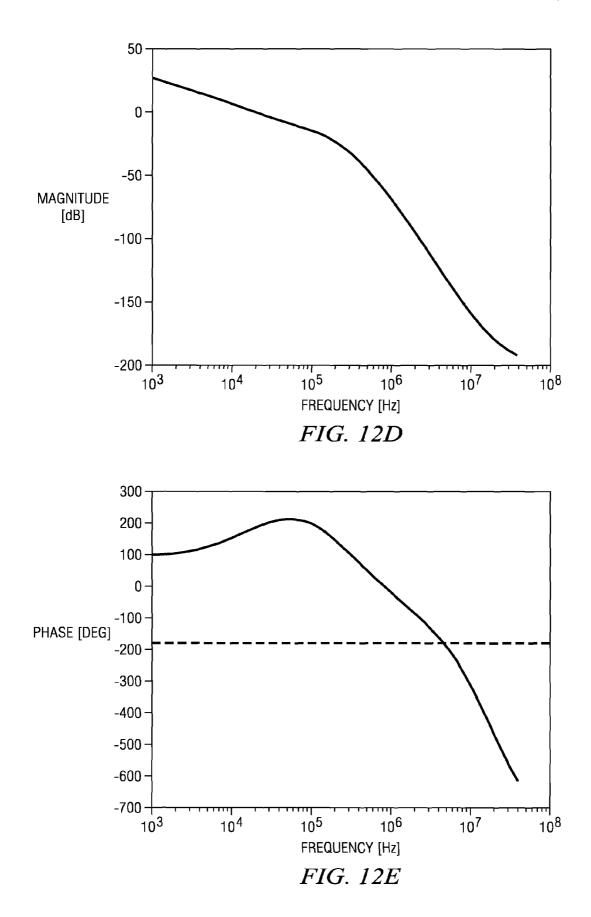

FIGS. 12B and 12C are plots of z-domain phase response with open-loop amplitude and phase transfer functions of the iADPLL of FIG. 12A with default loop settings,  $\alpha = 2^{-7}$ ,  $\rho =$  $2^{-16}$ ,  $\lambda = [2^{-3} 2^{-5} 2^{-5} 2^{-5}]$  and integral gain operating on resampled PHE signal;

FIGS. 12D and 12E are plots of z-domain phase response with open-loop amplitude and phase transfer functions of the iADPLL of FIG. 12A with default loop settings,  $\alpha = 2^{-7}$ ,  $\rho =$  $2^{-16}$ ,  $\lambda = [2^{-3} 2^{-5} 2^{-5}]$  and integral gain operating on filtered PHE signal;

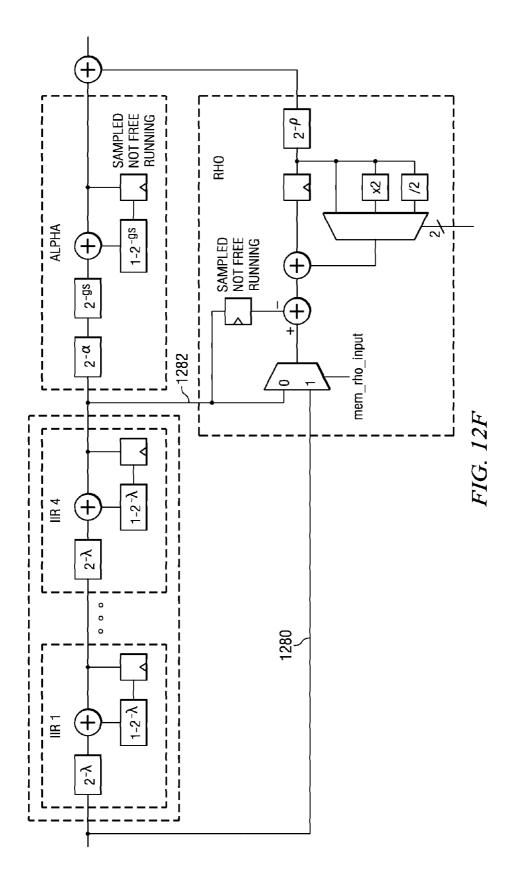

FIG. 12F is a block diagram of the iADPLL loop filter with alpha gear-shifting;

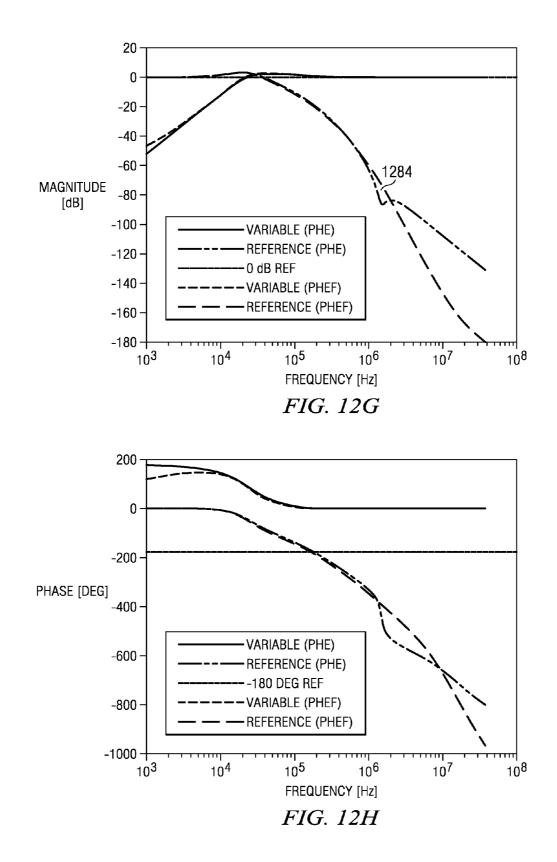

FIG. 12G is a plot showing the closed loop iADPLL transfer function magnitude response using both a raw PHE signal and a filtered PHEF signal for integral control;

20

45

FIG. 12H is a plot showing the closed loop iADPLL transfer function phase response using both a raw PHE signal and a filtered PHEF signal for integral control;

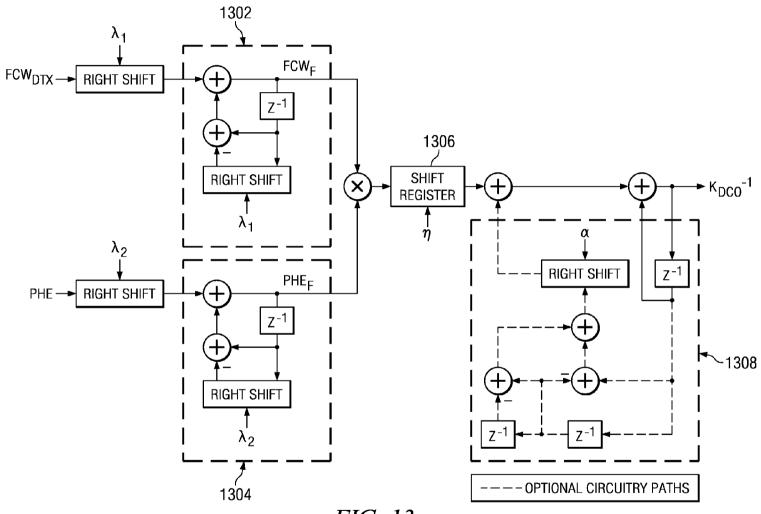

FIG. 13 is a block diagram of a hybrid stochastic gradient (HSG) K<sub>DCO</sub> normalizing factor calibration/compensation 5 algorithm;

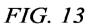

FIG. 14 is an illustration of coarse dithering applied to the slicer of the reference frequency generator;

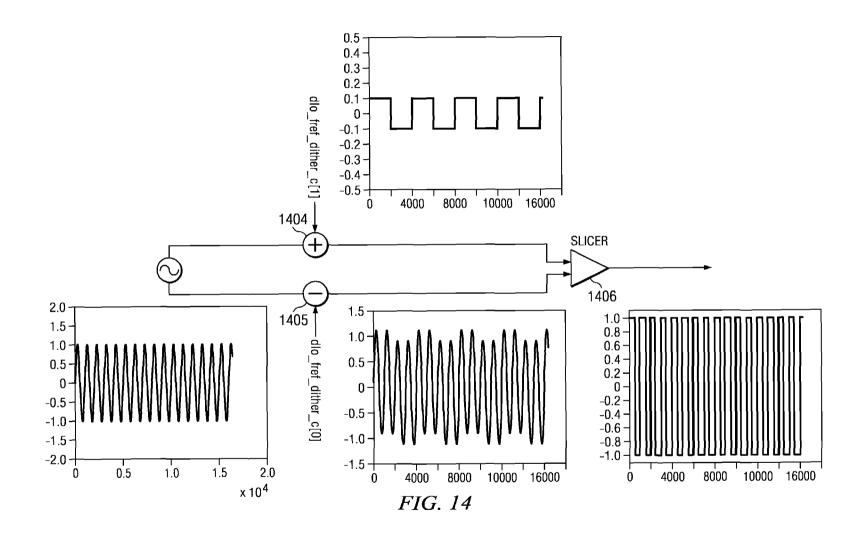

FIG. 15 is a block diagram of circuit for providing both coarse and fine dithering to the slicer input; 10

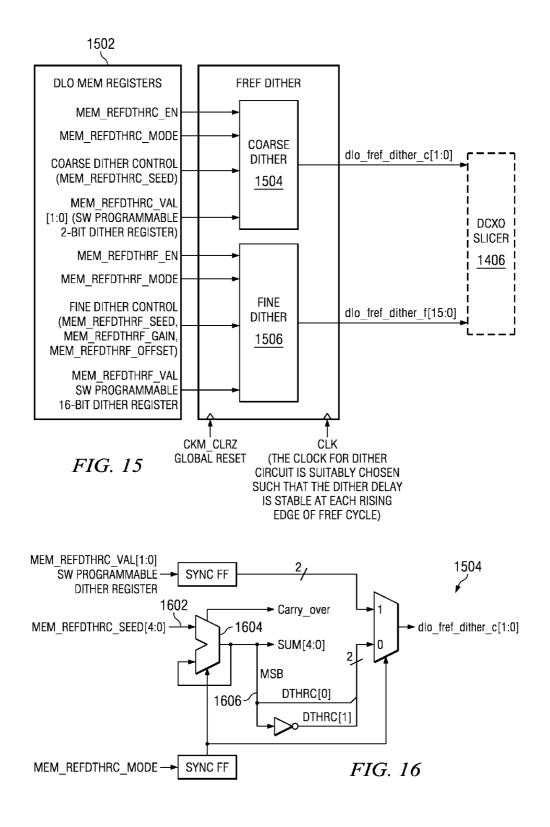

FIG. 16 is a more detailed block diagram of the coarse dither circuit of FIG. 15;

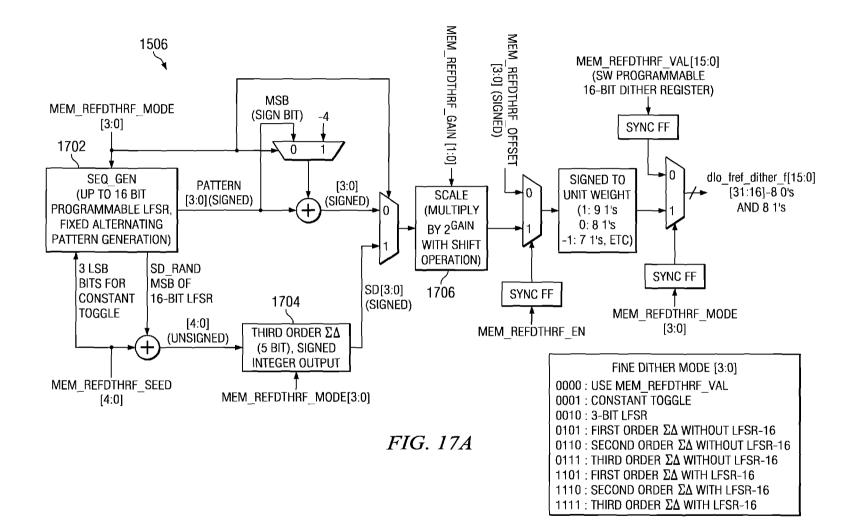

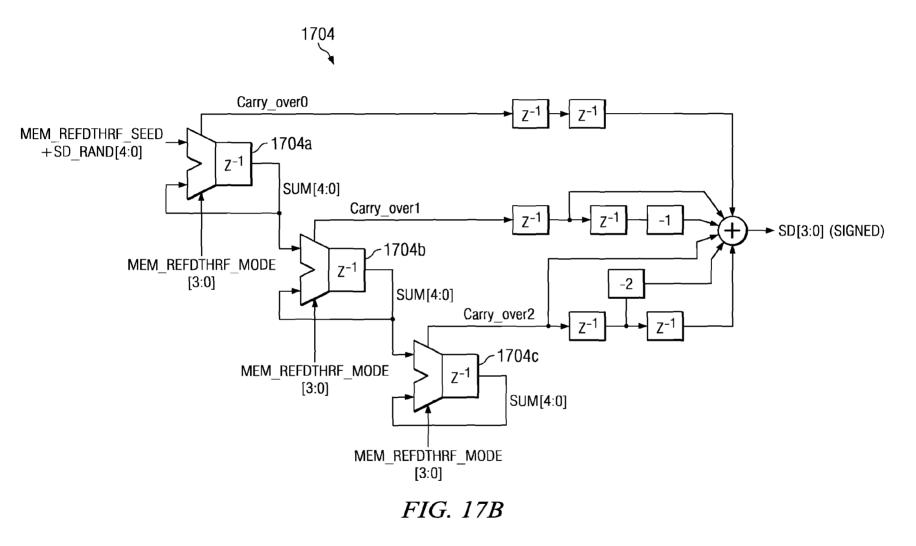

FIG. 17A is a more detailed block diagram of the fine dither circuit of FIG. 15;

FIG. 17B is a more detailed block diagram of the sigma- 15 delta generator of the fine dither circuit of FIG. 17A

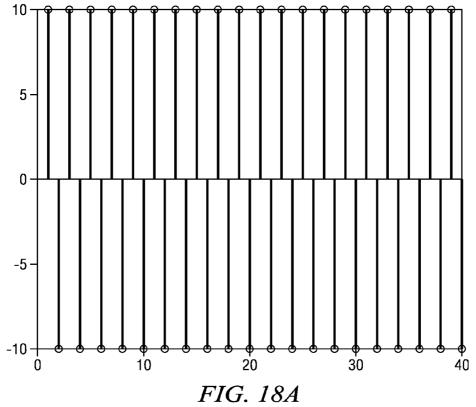

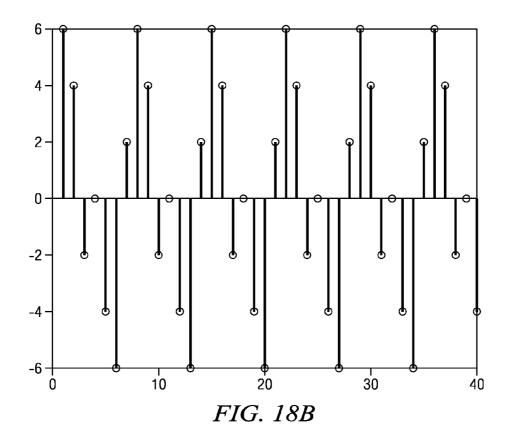

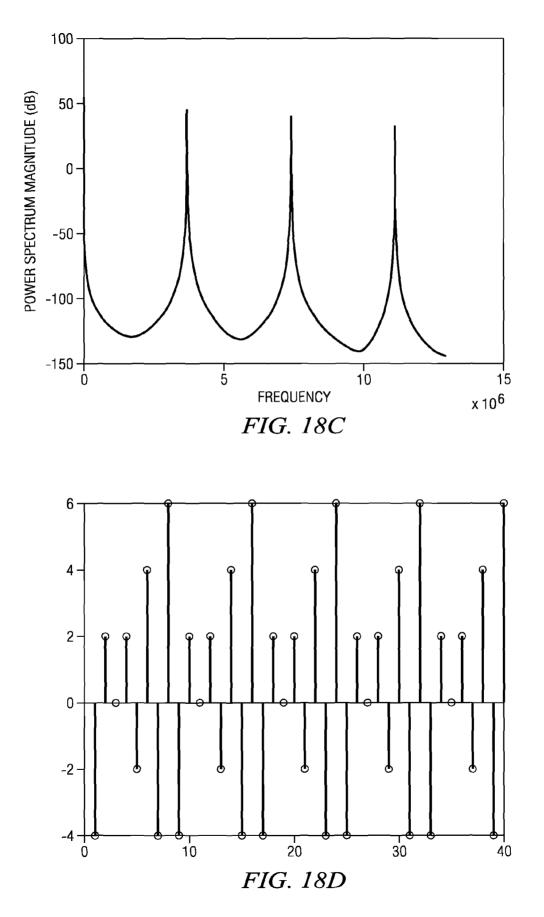

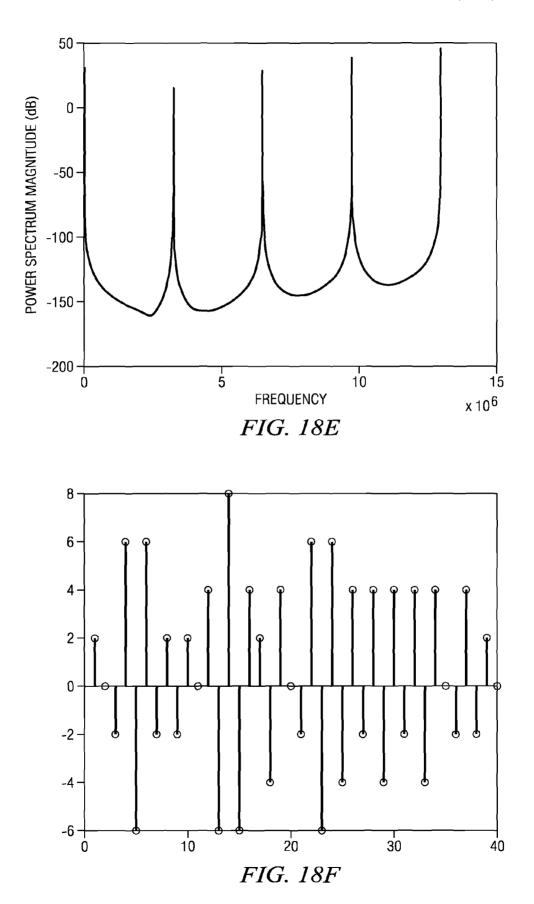

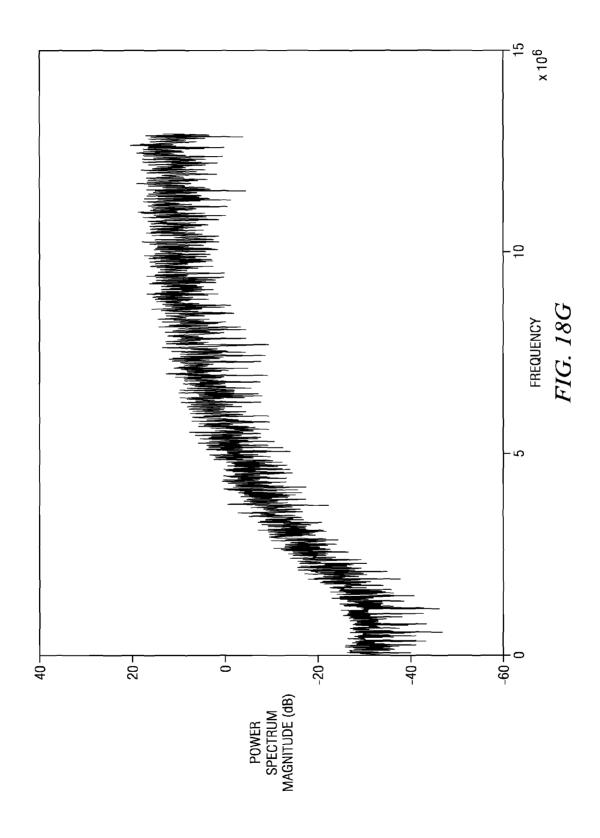

FIGS. 18A-G are plots illustrating example short sequence dither signals and resulting spectral magnitudes;

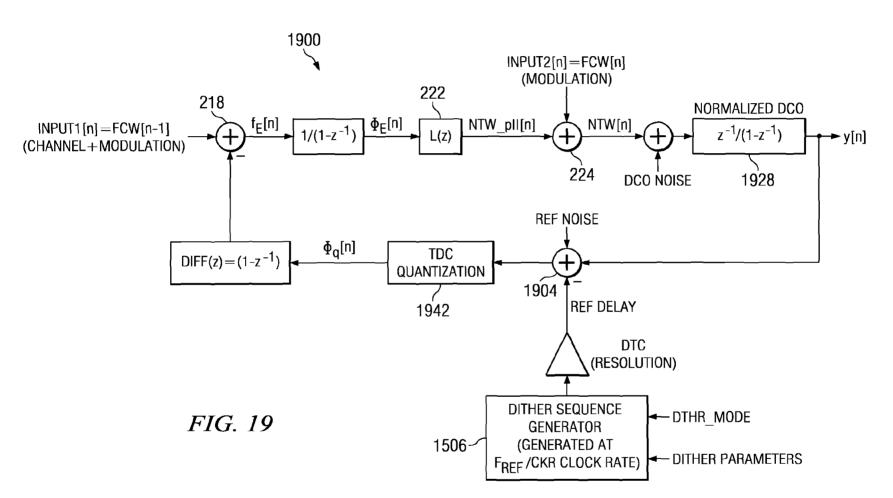

FIG. 19 is a model of open loop FREF dithering of the iADPLL of FIG. 2:

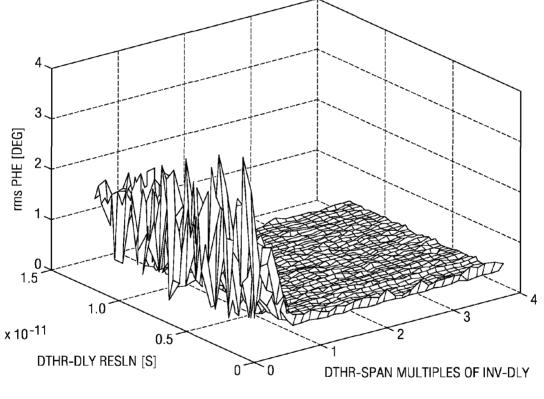

FIG. 20 is a plot of phase error vs. dither resolution (fraction of inverter delay) for different inverter delay values;

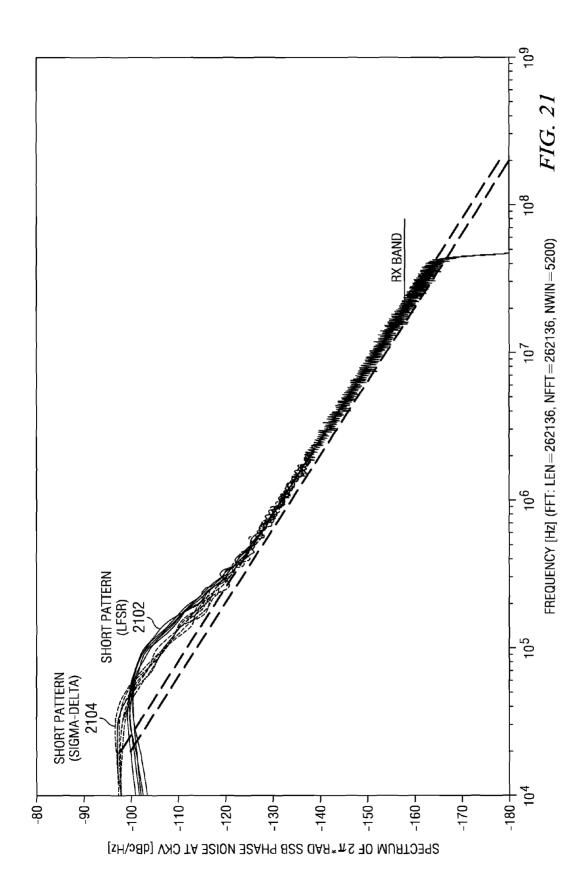

FIG. 21 is a plot illustrating a comparison of phase error spectrums for FREF dithering in a low noise environment;

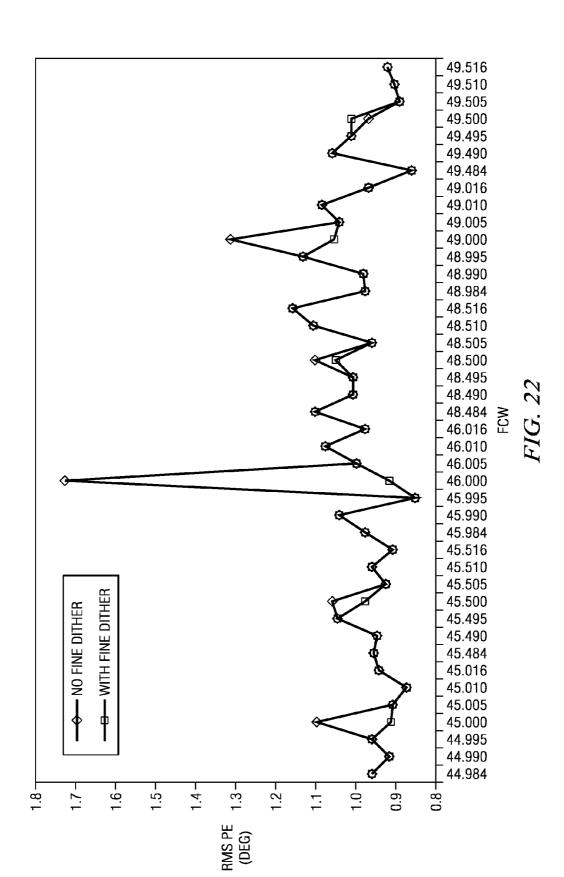

FIG. 22 is a plot illustrating effects of fine dithering on 25 integer and half-integer channels with neighboring channels for high band (DCS, PCS);

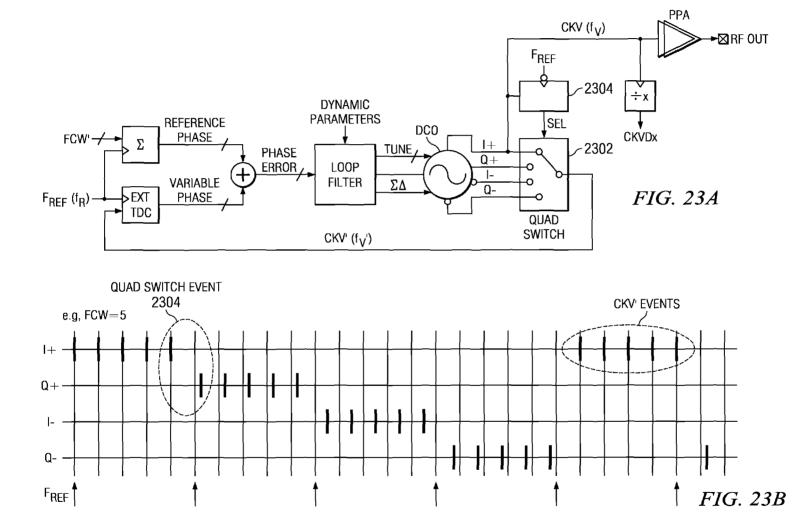

FIG. 23A is a conceptual block diagram illustrating quadrature CKV rotation in the iADPLL of FIG. 2;

FIG. 23B is a plot illustrating quadrature CKV rotation 30 when a frequency control work (FCW) has a value of integer five;

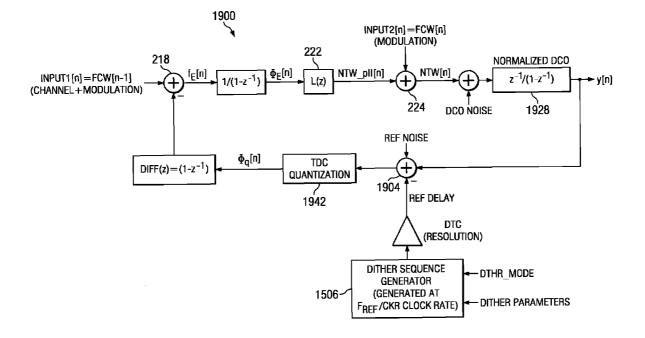

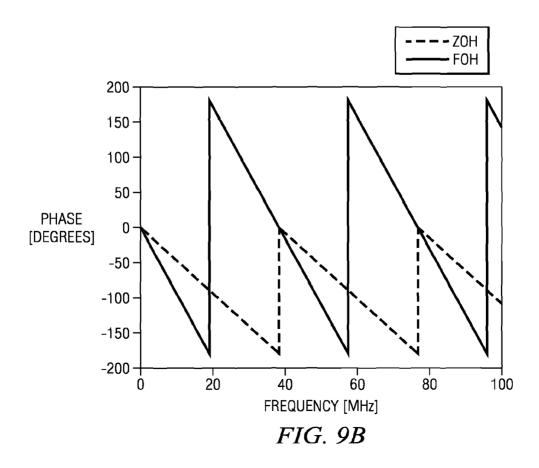

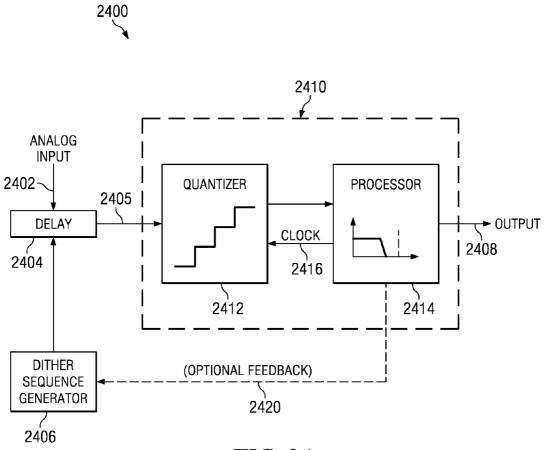

FIG. 24 is an alternative embodiment of an analog to digital system with dithering;

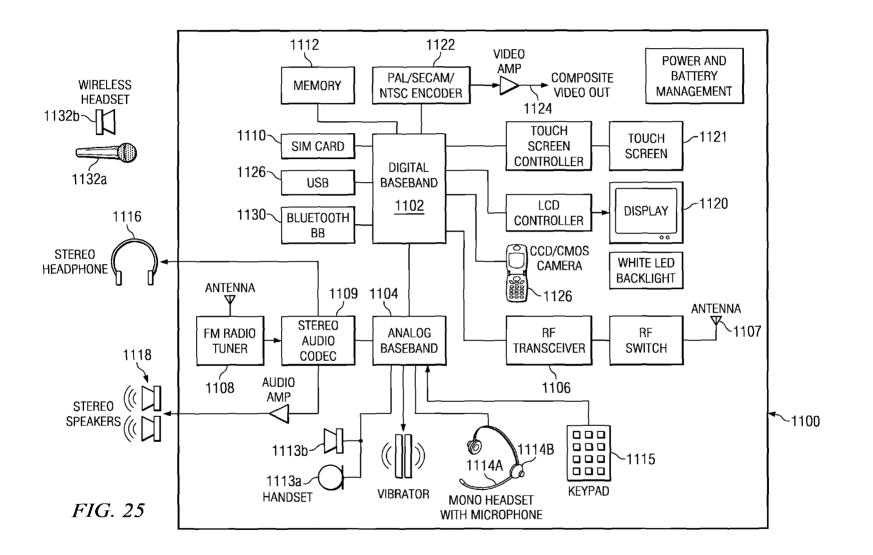

FIG. 25 is a block diagram of a digital system with an 35 embodiment of an iADPLL within a digital radio transceiver.

#### DETAILED DESCRIPTION OF EMBODIMENTS OF THE INVENTION

The notation is used throughout this document is listed in Table 1.

TABLE 1 Glasser

| Glossary    |                                                                                                                                                                             |    |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| Term        | Definition                                                                                                                                                                  |    |  |

| ADPLL       | All Digital Phase Locked Loop                                                                                                                                               | -  |  |

| ASIC        | Application Specific Integrated Circuit                                                                                                                                     |    |  |

| CDMA        | Code Division Multiple Access                                                                                                                                               | 50 |  |

| CKR         | Retimed Reference Clock                                                                                                                                                     |    |  |

| CKV         | Variable Oscillator Clock, (~2 GHz) equals channel                                                                                                                          |    |  |

|             | frequency in HB and twice the channel frequency in LB                                                                                                                       |    |  |

| CMOS        | Complementary Metal Oxide Semiconductor                                                                                                                                     |    |  |

| DCO         | Digitally Controlled Oscillator                                                                                                                                             | 55 |  |

| DECT        | Digital Enhanced Cordless Telecommunications                                                                                                                                |    |  |

| DPLL        | Digital Phase Locked Loop                                                                                                                                                   |    |  |

| DRP         | Digital RF Processor or Digital Radio Processor                                                                                                                             |    |  |

| EDGE        | Enhanced Data rates for GSM Evolution                                                                                                                                       |    |  |

| EDR         | Enhanced Data Rate                                                                                                                                                          |    |  |

|             |                                                                                                                                                                             | 60 |  |

| FCW         | $\label{eq:Frequency Command Word is the ratio between variable clock frequency and the reference frequency, \\ FCW = \frac{Variable clock frequency}{Reference Frequency}$ | 00 |  |

| FDD<br>FPGA | Frequency Division Duplex<br>Field Programmable Gate Array                                                                                                                  | 65 |  |

#### TABLE 1-continued

| Glossary                                                                       |                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Term                                                                           | Definition                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| FREF<br>FSK<br>GFSK<br>GPRS<br>GSM<br>HB<br>HDL<br>IEEE<br>IIR                 | Frequency Reference<br>Frequency Shift keying<br>Gaussian Frequency Shift Keying<br>General Packet Radio Service<br>Global System for Mobile communications<br>High Band<br>Hardware Description Language<br>Institute of Electrical and Electronic Engineers<br>Infinite Impulse Response                                                              |  |  |  |

| KDCOINV                                                                        | DCO Gain Normalization multiplier is the reciprocal<br>of the DCO gain step normalized with the input<br>sampling frequency,<br>$KDCOINV = \frac{Datapath Sampling Frequency}{Estimated DCO Gain}$                                                                                                                                                      |  |  |  |

| LB<br>LDO<br>LFSR<br>MOSCAP                                                    | Low Band<br>Low Drop-Out regulator<br>linear feedback shift register<br>Metal Oxide Semiconductor Capacitor                                                                                                                                                                                                                                             |  |  |  |

| OTW                                                                            | Oscillator Tuning Word is the normalization of the DCO<br>modulation frequency ratio by the DCO gain,<br>$OTW = \frac{Modulation Frequency}{Estimated DCO Gain}$                                                                                                                                                                                        |  |  |  |

| PERINV                                                                         | Period Normalization multiplier is the ratio between<br>the nominal DCO clock frequency and an<br>average inverter delay of the TDC,<br>$PERINV = \frac{Variable \ clock \ time \ period}{TDC \ Inverter \ Delay}$                                                                                                                                      |  |  |  |

| PHE<br>PLL<br>PVT<br>RF<br>RTL<br>TDC<br>UMTS<br>VCO<br>WCDMA<br>WiMAX<br>WLAN | Phase Error<br>Phase Locked Loop<br>Process, Voltage, Temperature<br>Radio Frequency<br>Register Transfer Logic<br>Time to Digital Converter<br>Universal Mobile Telecommunications System<br>Voltage Controlled Oscillator<br>Wideband Code Division Multiple Access<br>Worldwide Interoperability for Microwave Access<br>Wireless Local Area Network |  |  |  |

An Interpolative All-Digital Phase Locked Loop (iAD-PLL) is an enhanced version of the All-digital PLL (ADPLL) frequency synthesizer, which is described in U.S. Pat. No. 7,145,399 entitled "Type-II all digital phase locked loop (PLL)" as well as U.S. Pat. No. 7,183,860 entitled "Gain Calibration of a Digital Controlled Oscillator" each of which are incorporated by reference herein in their entirety. Also, U.S. Patent Publication No. 200610038710A1, published Feb. 23, 2006, Staszewski et al., entitled "Hybrid Polar/Cartesian Digital Modulator" and U.S. Pat. No. 6,809,598, to Staszewski et al., entitled "Hybrid of Predictive And Closed-55 Loop Phase-Domain Digital PLL Architecture," each of which are incorporated herein by reference in their entirety. This advanced all-digital frequency synthesizer possesses two-point digital, i.e., reference and direct, frequency modulation capability. iADPLL, like its predecessor, uses digital signal processing and efficient circuit design techniques. A 4 or 8 GHz digitally-controlled oscillator (DCO) is at the heart of iADPLL, where fine frequency resolution is achieved through high-speed sigma-delta ( $\Sigma \Delta$ ) dithering. This setup allows for iADPLL loop control circuitry to be implemented 65 in a fully digital manner using Infinite Impulse Response (IIR) filters and a digital Proportional-Integral (PI) controller. For the feedback of DCO phase in the time-domain, very fine time resolution  $(\sim 20 \text{ ps})$  is achieved by employing a Time-to-Digital Converter (TDC) comprising a chain of digital inverters.

The iADPLL architecture is distinct in that the loop filter and bulk of the logic operates on an RF derived variable clock 5 domain. Due to the common RF based clock source for the major digital components, convenient digital handoff is achieved in the signal paths. The architecture uses two resamplers (one linear and the other a simple zero-order hold) for the exchange of data from and to the reference clock domain 10 to the variable RF clock domain. In the variable clock domain, availability of several edge-aligned clock domains also facilitate physical register transfer logic (RTL) hardware sharing by time slicing. iADPLL can be embodied by more than one arrangement of the resampler and the other digital blocks. 15 While several embodiments will be described herein, these descriptions are not intended to be limiting.

iADPLL architecture enhancements included in the various embodiments that will be described in more detail below aim at improving the spectral and the phase-domain perfor-20 mance of the original ADPLL architecture. In particular, the architectural changes use the DRP silicon area more efficiently as well as tackle the following critical aspects of the ADPLL design:

1. A reduction in the magnitude of the reference spurs is 25 achieved by executing the loop filter in the iADPLL on a channel frequency derived clock. This significantly reduces the circuitry directly clocked by the reference clock or its retimed versions. Further, all the circuits interfacing to the DCO are being clocked at frequencies which are both higher 30 and asynchronous to the reference frequency. Note that this arrangement necessitates the use of resampling circuits to deal with the multi-rate operation of the iADPLL. Mathematical analysis ensures the stability of iADPLL with these resamplers. 35

2. By using a direct point injection rate of channel frequency divided by 16, any sampling replicas are pushed to frequencies greater than 100 MHz from the carrier, where they are greatly attenuated by the DCO phase noise and loop skirt. Essentially these spurs are below the noise floor and do 40 not appear in the simulations.

3. The use of a higher modulation injection rate also results in decreased spectral contribution of an iADPLL based transmitter in the GSM receive bands as described above. Further use of a higher direct-point injection frequency (>100 MHz) 45 theoretically reduces the possibility of multiple spurs in the RX band.

4. A KDCO inverse calibration algorithm based on the Hybrid Stochastic Gradient (HSG) has been incorporated into iADPLL. This new algorithm ensures better than 1% accu- 50 racy of KDCO inverse estimate after initial compensation before each GSM burst under PVT. This aspect is described in more detail in U.S. patent application Ser. No. 11/460,221 entitled "Hybrid Stochastic Gradient Based Digital Controlled Oscillator Gain  $K_{DCO}$  Estimation", filed Jul. 7, 2006 55 and incorporated by reference herein in its entirety.

5. Improved dithering mechanisms are used to counter the TDC quantization dead-band impediments in the iADPLL phase feedback path, especially in case of integer-N channels, i.e., when channel frequency is a multiple of reference fre- 60 quency, as well as half-integer-N channels. Dithering has been improved to provide uniform phase-domain character-istics for all possible GSM channel frequencies.

6. A mechanism for quadrature phase rotation of the ADPLL feedback DCO variable frequency (CKV) at the input of the TDC. This forces the ADPLL to be operated in an offset feedback mode, where the frequency command word

(FCW) for integer channel frequencies will not be integer any more (due to the introduced offset).

To aid in understanding the principles of the present invention, a description is provided in the context of a digital RF processor (DRP) transmitter and receiver that may be adapted to comply with a particular wireless communications standard such as GSM, Bluetooth, WCDMA, etc. It is appreciated, however, that the invention is not limited to use with any particular communication standard and may be used in control, optical, wired and wireless applications. Further, the invention is not limited to use with a specific modulation scheme but is applicable to any modulation scheme including both digital and analog modulation.

Note that throughout this document, the term communications device is defined as any apparatus or mechanism adapted to transmit, or transmit and receive data through a medium. The communications device may be adapted to communicate over any suitable medium such as RF, wireless, infrared, optical, wired, microwave, etc. In the case of wireless communications, the communications device may comprise an RF transmitter, RF receiver, RF transceiver or any combination thereof. The notation DRP is intended to denote either a Digital RF Processor or Digital Radio Processor. References to a Digital RF Processor infer a reference to a Digital Radio Processor and vice versa.

A block diagram illustrating a single chip radio incorporating an interpolative all-digital local oscillator based polar transmitter and digitally-intensive receiver is shown in FIG. 30 1. For illustration purposes only, the transmitter, as shown, is adapted for the GSM/EDGE/WCDMA cellular standards. It is appreciated, however, that one skilled in the communication arts can adapt the transmitter illustrated herein to other modulations and communication standards as well without 35 departing from the spirit and scope of the present invention.

The radio circuit, generally referenced 130, comprises a radio integrated circuit 136 coupled to a crystal 152, antenna front end module 176 connected to antenna 180 and battery management circuit 132. The radio chip 136 comprises a script processor 146, digital baseband (DBB) processor 144, memory 142 (e.g., static RAM), transmit (TX) block 148, receiver (RX) block 150, digitally controlled crystal oscillator (DCXO) 154, slicer 156, power management unit 138, RF built-in self test (BIST) 140. Battery 134 and battery management circuit 132 are connected to radio chip 136 for providing power. The TX block comprises high speed and low speed digital logic block 158 including  $\Sigma\Delta$  modulators 160, 162, digitally controlled oscillator (DCO) 164, digitally controlled power amplifier (DPA) 174 or pre power amplifier (PPA), time-to-digital converter (TDC) circuit 170 and TDC quantization noise shaping block 166. The iADPLL and transmitter generate various radio frequency signals. The RX block comprises a low noise transconductance amplifier 182, current sampler 184, discrete time processing block 186, analog to digital converter (ADC) 188 and digital logic block 190

The radio also comprises TDC quantization noise shaping block **166** operative to reduce the quantization noise contribution of the TDC. It is noted that the TDC quantization noise shaping mechanism is especially applicable in an ADPLL circuit.

The interpolated all-digital phase-locked loop (iADPLL) based transmitter employs a polar architecture with all digital phase/frequency and amplitude modulation paths. The receiver employs a discrete-time architecture in which the RF signal is directly sampled and processed using analog and digital signal processing techniques.

-5

A key component is the digitally controlled oscillator (DCO) 164, which avoids any analog tuning controls. A digitally-controlled crystal oscillator (DCXO) generates a highquality base station-synchronized frequency reference such that the transmitted carrier frequencies and the received symbol rates are accurate to within 0.1 ppm. Fine frequency resolution is achieved through high-speed  $\Sigma\Delta$  dithering of its varactors. Digital logic built around the DCO realizes an interpolated all-digital PLL (iADPLL) that is used as a local oscillator for both the transmitter and receiver. The polar transmitter architecture utilizes the wideband direct frequency modulation capability of the iADPLL and a digitally controlled power amplifier (DPA) 174 for the amplitude modulation. The DPA operates in near-class-E mode and uses an array of nMOS transistor switches to regulate the RF amplitude and acts as a digital-to-RF amplitude converter (DRAG). It is followed by a matching network and an external antenna front-end module 176, which comprises a power amplifier (PA), a transmit/receive switch for the common 20 antenna 180 and RX surface acoustic wave (SAW) filters. Fine amplitude resolution is achieved through high-speed  $\Sigma\Delta$ dithering of the DPA NMOS transistors.

The receiver 150 employs a discrete-time architecture in which the RF signal is directly sampled at the Nyquist rate of 25 the RF carrier and processed using analog and digital signal processing techniques. The transceiver is integrated with a script processor 146, dedicated digital base band processor 144 (i.e. ARM family processor and DSP) and SRAM memory 142. The script processor handles various TX and RX calibration, compensation, sequencing and lower-rate data path tasks and encapsulates the transceiver complexity in order to present a much simpler software programming model.

The frequency reference (FREF) is generated on-chip by a 38.4 MHz (but could be 26.0 MHz or other in another embodiment) digitally controlled crystal oscillator (DCXO) 154 coupled to slicer 156. An integrated power management (PM) system is connected to an external battery management  $_{\Delta 0}$ circuit 132 that conditions and stabilizes the supply voltage. The PM comprises a switched mode power supply (SMPS) as well as multiple low drop out (LDO) regulators that provide internal supply voltages and also isolate supply noise between circuits, especially protecting the DCO. The SMPS 45 is used for efficient conversion of the battery voltage to a level that can be used by on-chip LDOs. The RF built-in self-test (RFBIST) 140 performs autonomous phase noise and modulation distortion testing, various loopback configurations for bit-error rate measurements and implements various DPA 50 calibration and BIST procedures. The transceiver is integrated with the digital baseband, SRAM memory in a complete system-on-chip (SoC) solution. Almost all the clocks on this SoC are derived from and are synchronous to the RF oscillator clock. This helps to reduce susceptibility to the 55 noise generated through clocking of the massive digital logic.

The transmitter comprises a polar architecture in which the amplitude and phase/frequency modulations are implemented in separate paths. Transmitted symbols generated in the digital baseband (DBB) processor are first pulse-shape 60 filtered in the Cartesian coordinate system. The filtered inphase (I) and quadrature (Q) samples are then converted through a COordinate Rotation Digital Computer (CORDIC) algorithm into amplitude and phase samples of the polar coordinate system. The phase is then differentiated to obtain 65 frequency deviation. The polar signals are subsequently conditioned through signal processing to sufficiently increase the

sampling rate in order to reduce the quantization noise density and lessen the effects of the modulating spectrum replicas

FIG. 2 is a more detailed block diagram of an iADPLL 200 used in the transceiver of FIG. 1 and constructed in accordance with the present invention. For illustration purposes only, the transmitter of the present embodiment is adapted for the GSM/EDGE cellular standard. It is appreciated, however, that one skilled in the communication arts can adapt the transmitter illustrated herein to other modulations and communication standards as well without departing from the spirit and scope of the present invention. For example, the transmitter illustrated in FIG. 1 can be extended for performing an arbitrary quadrature modulation scheme.

A description of the iADPLL, generally referenced 200, including the frequency/phase modulation path is provided herein below. The core of the iADPLL is a digitally controlled oscillator (DCO) 228 adapted to generate the RF oscillator clock CKV. The oscillator core (not shown) operates at twice the 1.6-2.0 GHz high frequency band or four times the 0.8-1.0 GHz low frequency band. The output of the DCO is then divided for precise generation of RX quadrature signals, and for use as the transmitter's carrier frequency. For GSM/ EDGE transceivers, a single DCO is shared between transmitter and receiver and is used for both the high frequency bands (HB) and the low frequency bands (LB). However, for modern 3G (WCDMA) or other duplex transmission systems, separate local oscillators might be needed to supply TX and RX carrier frequencies.

A digitally-controlled oscillator (DCO) lies at the heart of the interpolated all-digital PLL (iADPLL) frequency synthesizer. It deliberately avoids any analog tuning voltage controls and is realized as an ASIC cell with truly digital inputs and outputs. The DCO comprises tunable switchable varactor 35 elements, cross-coupled pairs of NMOS transistors, and a biasing circuit. The DCO varactors may be realized as n-poly/ n-well MOS capacitor (MOSCAP) devices that operate in the flat regions of their C-V curves. Current advanced CMOS process lithography allows creation of extremely small-size but well-controlled varactors. The switchable capacitance of the finest differential TB varactor is in tens of attofarads. This resolution, however, is still too coarse for wireless applications and requires high-speed  $\Sigma\Delta$  dithering to enhance the time-averaged frequency resolution, which is described in the following sections. The output of the DCO is input to the RF high band power amplifier 234. It is also input to the RF low band power amplifier 232 after divide by two in divider 230.

In case of transmit modulation, the symbols, (for example Gsm EDGE, wcdma, etc), in the form of in-phase and quadrature data streams are received from the digital baseband (DBB) circuit, not shown in this figure. The GSM symbols are passed through a pulse-shaping filter (PSF) within processor 212 that converts it to phase modulation. This phase modulation is interpolated in transmit data (DTX) processing circuit 250 and then passed on to the iADPLL after differentiation at the CKVD16 clock rate using differentiator 252. CKV is the iADPLL RF output digital variable clock in case of high-bands (HB>1 GHz) or twice the RF output clock in case of low-band (LB, <1 GHz).

For the case of EDGE, WCDMA, etc. the complex modulation I/Q data streams are fed to a COordinate Rotation Digital Computer (CORDIC) within processor 212, which converts it from Cartesian to polar representation. The amplitude modulation signal is passed through sigma-delta amplitude (SAM) signal processing blocks 214 before they are passed onto the on-chip digital pre-power amplifier (DPA) 234, while the phase modulation output of the cordic is passed onto iADPLL after the necessary interpolation and signal processing, which performs the phase modulation of the DCO.

Under no modulation conditions, iADPLL digitally controls the DCO to produce a stable variable clock (CKV) in the 5 targeted RF frequency band. In the feedback path, CKV is used for phase detection and reference retiming. The time to digital phase conversion in the feedback happens using a TDC inverter chain **242**.

The channel and data frequency control words are in the 10 frequency command word (FCW) format, which is defined as the fractional frequency division ratio N, with a fine frequency resolution limited only by the FCW word-length. For example, with 24 fractional FCW bits, the frequency granularity using a 38.4 MHz reference frequency is 38.4 MHz/ 15  $2^{24}$ =2.29 Hz. In this embodiment, the direct point frequency injection is at the CKVD16 (which is 1×HB/2×LB channel frequency divided by 16, i.e., CKVD16= $f_r/16$ ) rate, so the possible DCO frequency resolution is in the range of 6~7.5 Hz (computed as  $f_r/16/2^{24}$ ). 20

The frequency reference (FREF) clock contains the only reference timing information for the RF frequency synthesizer to which phase and frequency of the RF output are to be synchronized. The RF output frequency ( $f_{F}$ ) is related to the reference frequency  $f_{R}$  according to the following formula. 25

$$f_V = N f_R$$

(1)

#### where, $N=f_{\nu}/f_R$ =FCW.

Synchronous Phase-Domain Operation

The iADPLL operates in a digitally-synchronous fixedpoint phase domain. The variable phase  $R_{\nu}[i]$  is determined by counting the number of rising clock transitions of the DCO oscillator clock CKV using variable phase accumulator 236. The variable phase  $R_{\nu}[i]$  is sampled via sampler 238 to yield 35 sampled FREF variable phase  $R_{\nu}[k]$ , where k is the index of the FREF edge activity. The sampled FREF variable phase  $R_{\nu}[k]$  is fixed-point concatenated with the normalized timeto-digital converter (TDC) 242 output  $\epsilon$ [k]. The TDC measures and quantizes the time differences between the fre- 40 quency reference FREF and the DCO clock edges. The sampled differentiated (via block 240) variable phase is subtracted from the frequency command word (FCW) by a synchronous arithmetic phase detector 218. The reference phase  $R_R[k]$  (equivalent to PHR in FIG. 5) is conceptually obtained 45 by accumulating FCW with every cycle of the retimed frequency reference (FREF) clock input.

The frequency error  $f_E[k]$  samples are accumulated via the frequency error accumulator **220** to create the phase error  $\phi_E[k]$  samples. The digital phase error  $\phi_E[k]$  is filtered by a 50 digital loop filter **222** and then normalized by the DCO gain normalization circuit **270** in order to correct the DCO phase/ frequency in a negative feedback manner. The loop behavior due to its digital nature is independent of process, voltage and temperature variations. The FREF retiming quantization 55 error  $\epsilon[k]$  is determined by the time-to-digital converter (TDC) **242** and the DCO period normalization multiplier **244**. The TDC is built as a simple array of cascaded inverter delay elements and flip-flops, which produces time conversion resolution finer than 25 ps in the design process. 60

It must be recognized that the two clock domains, FREF and DCO, are not entirely synchronous and it is difficult to physically compare the two digital phase values without having to face meta-stability problems. During the frequency acquisition, their edge relationship is not known and during the phase lock the edges will exhibit rotation if the fractional FCW is non-zero. Consequently, the digital-word phase comparison is performed in the same clock domain. The synchronous operation is achieved by over-sampling the FREF clock using a higher-rate DCO derived clock (typically CKVD8) in reference retiming circuit **246**. The resulting retimed CKR clock is thus stripped of the FREF timing information and is used throughout the system. This ensures that the massive digital logic is clocked after the quiet interval of the phase error detection by the TDC.

The main advantage of representing the phase information in fixed-point digital numbers is that, after the conversion, it cannot be further corrupted by noise. Consequently, the phase detector could be simply realized as an arithmetic subtractor that performs an exact digital operation. Thus, having a single conversion place, where the continuously-valued clock transition edge delay is quantized within the TDC, the susceptibility to noise and quantization errors is minimized and well controlled. It should be emphasized that it is very advantageous to operate in the phase domain for several reasons. First, the phase detector used is not a conventional correlative 20 multiplier generating reference spurs. DRP architecture uses an arithmetic subtractor 218, which does not introduce any spurs into the loop. Second, the dynamic range of the phase error could be made arbitrarily large simply by the increasing word-length of the phase/frequency accumulators. Conventional three-state phase/frequency detectors are typically limited to only  $\pm 2\pi$  of the compare rate. Third, the phase domain operation is more amenable to digital implementations, contrary to the conventional approach.

High-Speed Direct Frequency Modulation Capability

As shown in FIG. **2**, the oscillating frequency deviation  $\Delta f$  is dynamically controlled by directly modulating the DCO frequency in a feed-forward manner. The iADPLL loop compensates by effectively removing the loop dynamics from the modulating transmit path (using the reference modulation injection). The remainder of the loop, including all error sources, operates under the normal closed-loop regime. This method is similar to the conventional two-point direct modulation scheme but because of the digital nature, it is exact and does not require any analog component matching, except for the DCO gain  $K_{DCO}=\Delta f/\Delta OTW$  calibration, which is achieved in using a robust hybrid stochastic-gradient algorithm implemented in digital domain, where OTW is the oscillator tuning word and is analogous to the voltage tuning of a VCO.

The fixed-point frequency modulating data FCW is oversampled in resampler 254 by the iADPLL DCO injection frequency  $f_r/16$  and normalized in multiplier 262 to the value of iADPLL DCO injection frequency  $f_{\nu}/16$ . Using the direct injection of the normalized FCW directly at the DCO impacts the oscillating frequency. The PLL loop will try to correct this perceived frequency perturbation integrated over the update period of  $1/f_R$ , which is then interpolated to the iADPLL operational frequency of  $f_{\nu}/32$  in resampling interpolator 256. This corrective action is compensated by the other (compensating) reference feed that is integrated by the reference phase accumulator. If the estimated DCO gain is accurate, i.e.,  $K_{DCO} \cong K_{DCO}$ , then the loop response to the modulation is flat from dc to  $f_{\nu}/64$  (or half of iADPLL operational frequency  $f_{\nu}/32$ ). The immediate and direct DCO frequency 60 control, made possible by accurate prediction of the DCO transfer function, is combined with the phase compensation of the PLL loop response. The two factors constitute the hybrid of predictive/closed PLL loop modulation method. Advantages of Using Higher Rate Direct-Point Modulation

One of the key advantages of using a direct point injection rate (say of channel frequency divided by 16) is that the phase

Injection

65

modulation can be presented to the DCO with a finer resolution. For example, the phase modulation in GSM has a BW of 200.00 kHz, while for a polar TX, in EDGE mode the phase modulation BW is approx. 2.0 MHz (LB) and 1.0 MHz (HB). The CKVD16 rate corresponds to an injection frequency 5 range of 103-124 MHz, which is at least three times higher than an FREF of 38.4 MHz, and 4 times higher than an FREF of 26 MHz. This implies that the phase modulation data update using a CKVD16 rate will be 3-4 times finer than the FREF rate used in the previous generations of ADPLL.

Furthermore, the data injection into the DCO comprises an integer and fractional parts, described in more detail below. The injection rate creates an effective zero order hold (ZOH) at resampler 254. The ZOH operation does not provide a large attenuation to the sampling replicas, which is only 13 dB 15 lower for 2nd harmonic and approx. 17 dB for 3rd harmonic,. As CKVD16 frequency is much higher than FREF, these replicas are correspondingly at 3-4 times higher frequency for CKVD16 (>100 MHz) vs. FREF (26-38.4 MHz). The DCO phase noise beyond the flicker corner of 1-2 MHZ has a 20 20 dB/decade slope, which implies that the residual sampling replicas after ZOH 254 sync filtering will receive an additional attenuation of 12 dB using CKVD16 injection rate as compared to FREF. In short, use of CKVD16 for direct point phase modulation injection results in pushing any sampling 25 replicas to frequencies greater than 100 MHz from the carrier, where they are greatly attenuated by the DCO phase noise and the spectral skirt of the loop filter. Essentially these signal processing spurs are below the noise floor and can not be seen in simulations or measurements.

Another important benefit of using CKVDx, where x=16 or 8 for direct point injection is that the quality of phase modulation injection becomes independent of the FREF frequency. The same iADPLL when used with different FREF's, say 26, 38.4 or 52 MHz will exhibit the same direct point 35 injection fidelity. However, note that there are other noise scaling terms that will be impacted by the FREF frequency change, but the iADPLL loop filters, modulation injection rates etc. will maintain their resolution across multiple possible reference frequencies.

It has been observed in previous versions of the ADPLL that the current spikes caused by clocking of bulk of the logic can be a source of spurious emissions. This is especially true for highly integrated transceivers targeted using DRP technology. For iADPLL, a significant part of the loop filter and 45 DCO interface logic executes on the LO derived clock domain. Since most of these frequencies are chosen to be higher than FREF, any such spurious products will have a larger intra-spur distance than FREF. For example, using CKVD32, the spurs (if present) will be 52-62 MHz apart as 50 compared to FREF frequencies. In retrospect, the current spikes due to the modulation injection rate into DCO have the highest impact, as the rush current to the boundary levelshifters might be supplied by the same LDO supply regulator, which powers DCO. The most critical among these spurs are 55 the ones that appear in the corresponding GSM/EDGE RX band during transmission. The widest GSM RX band is 65 MHz, and using CKVD16 at the interface at most one spur may appear in the RX band due to these parasitic supply regulation issues. Therefore, the use of a higher direct-point 60 injection frequency (>100 MHz) theoretically reduces the possibility of multiple spurs in the RX band.

FIG. 3 is a block diagram of the digitally controlled oscillator (DCO) of FIG. 2 illustrating tracking bits with dynamic element matching (DEM) of the integer part and sigma-delta 65 (SD) dithering of the fractional part. The digitally-controlled quantized capacitance of the LC tank is split into four major

varactor banks that are sequentially activated during frequency locking. Large 1.8-2.5 MHz steps are performed during a process-voltage-temperature (PVT) calibration modes using a MIM-capacitor PVT bank (PB). Smaller 250-450 kHz steps of the acquisition bank (AB) are used during a channel select. The finest tens of kHz steps of the tracking bank (TB) are used during the actual transmit and receive. The unit weighted tracking bank is further partitioned into 32 or more integer and 3 fractional varactors. The fractional varactors undergo high-speed  $\Sigma\Delta$  dithering via a 1<sup>st</sup> and 2<sup>nd</sup> order digital  $\Sigma\Delta$  dithering circuit 312.

FIG. 3 illustrates an oscillator tuning mechanism 227 that improves the DCO 228 frequency resolution beyond the basic 100 kHz frequency step of the TB varactors. The 15 fixed-bit oscillator tuning word (OTW) 302 is split into seven integer 304 and eight fractional bits 306. In other embodiments, based on the configuration of the DCO varactor banks, the integer bit can be scaled to be five or six, for example. The LSB of the integer part (TB varactor) corresponds to the minimum frequency step of the DCO. Within the DCO, the integer part is thermometer encoded to control the same-size DCO varactors. This guarantees monotonicity and helps to achieve adequate linearity. The switch matrix 308, together with the row and column select logic, operates as a binaryto-unit-weighted encoder in response to the integer part of the TB tuning word. To minimize the impact on DCO linearity due to TB varactor mismatches, dynamic element matching (DEM) mechanisms that perform rotation of the TB row varactors have been built into the design.

The fractional part, on the other hand, employs a timeaveraged dithering that produces a high-rate integer stream whose time-averaged value equals the lower-rate fractional TB input. The spurs due to sigma-delta ( $\Sigma \Delta$ ) idle tones are randomized using an linear feedback shift register (LFSR) 310 dithering of the fractional word. Use of the second order  $\Sigma \Delta$  312 and the high speed modulator clock speed (as high as CKVD1, i.e., 1.8 GHz), makes the in-band oscillator phase 40 noise degradation almost immeasurable. With eight fractional bits and an integer bit size of 100 kHz, the effective open-loop DCO resolution will be 100 kHz/2<sup>8</sup>=390.625 Hz, which is sufficient for GSM applications.

The fractional path of the DCO tracking bits is entirely separated from the lower-rate integer part. It even has a dedicated DCO input just to avoid "contamination" of the rest of the tracking bits with frequent transitions. The  $\Sigma\Delta$  modulator 312 is responsive to only the fractional part of the tracking tuning word. Under certain operational conditions, especially when the input of the  $\Sigma\Delta$  modulator 312 is a small but constant fraction, the  $\Sigma\Delta$  output may exhibit spurs due to the cyclic pattern being generated by the modulator. These spurious products are called idle tones, which can be avoided by enabling an LFSR 310 output which gets added to raw input to create a dithered input to the  $\Sigma\Delta$  modulator. The  $\Sigma\Delta$  output becomes free of these idle tones by using the described mechanism.

The actual merging of both parts is performed inside the oscillator through time-averaged capacitance summation at the LC tank. Thus the critical high-speed arithmetic operations are performed in the "analog domain" through the additions of capacitance inside the DCO.

FIG. 4 is a normalized abstraction layer of the DCO of FIG. 3. At a higher level of abstraction, the DCO oscillator 228 together with the equivalent DCO gain normalization multiplication, results in a gain of:

$$\frac{f_{\nu}/16}{\hat{K}_{DCO}} = \frac{f_{\nu}/16}{f_R} \cdot \frac{f_R}{\hat{K}_{DCO}}$$

The above equation logically comprises the normalized DCO (nDCO) **400**, as illustrated in FIG. **4** for the data modulating path. The DCO gain normalization circuitry **270** (referring to FIG. **2**) conveniently decouples the phase and frequency information throughout the system from the process, 10 voltage and temperature variations that normally affect the  $K_{DCO}$ . The frequency information is normalized to the value of the CKVD16 (1×HB/2×LB CKV frequency divided by 16,  $f_p/16$ ) injection frequency from the DTX **250/252**. The DCO interface is updated at the CKVD16 rate (which is also the <sup>15</sup> direct point frequency modulation injection rate) via multiplier **258** at the adder **224**. The decomposition of the

$$\frac{f_v/16}{\hat{K}_{DCO}}$$

DCO normalization factor, shown above, accounts for the interpolation already done on the digital frequency modula- <sup>25</sup> tion data.

For clarity, note that the iADPLL phase accumulation **220** happens at the CKR (or FREF) rate, the remainder of the loop filters operates at the CKVD32 rate, see FIG. **2**. The phase-domain resampling **256** from the CKR to CKVD32 rate serves to translate the data from one clock domain to the other using embedded interpolative filtering. This does not change the phase accumulation rate (which is CKR), which requires the correct DCO normalization to be

$$\frac{f_R}{\hat{K}_{DCO}}.$$

However, in order to derive this reference signal normalization from the

$$\frac{f_v/16}{\hat{K}_{DCO}}$$

factor, which is precisely estimated by adaptation, a scaled version of

$$\frac{f_{\nu}/16}{\hat{K}_{DCO}}$$

is used for the scaling **226** of the iADPLL loop correction applied to the DCO. For a scaling **260** by 2, the missing factor of

$$\frac{f_R}{f_v/32}$$

is considered as a part of the PI controller tuning parameters  $_{65}$  (i.e., proportional gain,  $\alpha$  and integral gain,  $\rho$ ). This avoids the use of an additional multiplier in the architecture.

The digital input to the Normalized DCO (nDCO) is a fixed-point normalized tuning word (NTW), whose integer part LSB bit corresponds to CKVD16. The quantity  $K_{DCO}$  should be contrasted with the process-temperature-voltageindependent oscillator gain  $K_{nDCO}$  which is defined as the frequency deviation (in Hz units) of the DCO in response to the 1 LSB change of the integer part of the NTW input. If the DCO gain estimate is exact  $K_{nDCO}=f_{p'}/(16\times LSB)$ , where  $f_{p'}/16$  is the direct point modulation injection rate. If there is a 10  $K_{DCO}$  estimation error, then

$$K_{nDCO} = \frac{f_V}{16 \times LSB} \cdot \frac{K_{DCO}}{\hat{K}_{DCO}} = \frac{f_V}{16 \times LSB} \cdot r$$

<sup>(2)</sup>

The dimensionless ratio  $r=K_{DCO}/\hat{K}_{DCO}$  is a measure of the accuracy of the DCO gain estimate.

FIG. 5 illustrates a general block diagram of the phase  $_{20}$  detection mechanism that can be mathematically captured as:

$$\Phi_{E}[k] = R_{R}[k] - R_{v}[k] + \epsilon[k] \tag{3}$$

The operation consists of the phase detector **218** itself (see also FIG. **2**, which shows a mathematically equivalent version), which operates on the three phase sources: reference phase RR[k] from adder **216**, variable phase Rv[k] from sampler **238**, and the fractional error correction  $\epsilon$ [k] from DCO period normalizer **244**. The actual variable phase Rv [i] from accumulator **236** is clocked by the CKV clock of index k. After the PHV resampling, all the three phase sources are synchronous to the CKR clock which guarantees the resulting phase error  $\phi_E$ [k] to be also synchronous. An extra output bit from the fractional phase error correction comprising TDC 35 and PF is due to metastability avoidance and is explained in the following sections.

The measurement of variable phase (i.e., the phase of the DCO output, CKV) is carried out in two steps. The integer part (i.e., the integer number of the CKV clock cycles) is do determined using a non-resettable CKV edge counter called Variable Phase Accumulator **236**. The remainder is the fractional part of the phase, which is the estimation of the sub-CKV clock period estimation of phase between FREF and the nearest CKV edge. This step is carried out by the time-to-d5 digital converter (TDC) **242** described in the next section. Integer Variable Phase Accumulation

The integer part of the variable phase comprises a count of the complete CKV clock cycles. The variable phase accumulator **236** implements the DCO clock count incrementing with 50 the rollover effect as described in the following equation.

$$R_{\nu}(i \cdot T\nu) \equiv R_{\nu}[i] = \sum_{l=0}^{i} 1$$

55

The deep submicron CMOS process is fast enough to perform an 8-bit binary incrementer at 2 GHz clock in one cycle using a simple carry-ripple structure. Critical timing of this operation would comprise a chain of seven half-adders and an inverter. However, for a commercial application it was necessary to add an extra timing margin in order to guarantee robust operation with acceptable yield for all the process and environmental conditions, as well as anticipated clock distribution skew statistics. This extra margin was obtained by increasing the maximum operational speed through topological means. The carry-ripple binary incrementer was trans-

45

formed into two separate smaller incrementers, not shown. The first high-speed incrementer operates on the two lowerorder bits and triggers the higher order increment whenever its count reaches "11". The second incrementer operates on the same CKV clock, but the 6-bit increment operation is allowed now to take four clock cycles. The long critical path of the 8-bit carry-ripple incrementer has thus been split into smaller parts allowing for the necessary timing margin.

## Time-To-Digital Converter (TDC)

FIG. 6 is a block diagram of the time-to-digital converter (TDC) 242 of FIG. 2. The TDC estimates the fractional part of the variable phase between the reference frequency edge and the next nearest edge of the DCO CKV clock. The TDC 15 operates by passing the DCO clock through a chain of inverters 602. The delayed clock vector is then sampled by the FREF clock using an array of registers 604 whose outputs form a pseudo-thermometer code. The decoded binary TDC output is normalized 244 by the DCO clock period  $T_{V}$  before feeding it to the loop. The combination of the arithmetic phase detector and the TDC is considered to be a replacement of the conventional phase/frequency detector. The number of TDC taps, L=56, has been determined as the count of inverters needed to cover the full DCO period under the strong process 25 corner (min t<sub>inv</sub>=15 ps) plus some margin. Other embodiments may possess a different TDC topology and have fewer or more taps, depending on process parameters.

TDC resolution is a single inverter delay,  $\Delta t_{inv}$ , which in this deep-submicron CMOS process is considered the most 30 stable logic-level regenerative delay and in the 65 nm process node is approximately 20-25 ps. This results in a quality phase detection mechanism, as evidenced by the close-in and rms phase noise measurement results of the DRP architecture. 35 While other TDC architectures can achieve the TDC resolution that is better than one inverter delay, they are quite complex and analog intensive. They simply appear not needed for GSM applications in this deep-submicron CMOS process when  $\Delta t_{inv}$ =25 ps can be easily achieved 40

The phase quantization resolution of the variable phase accumulator 236, as described in the preceding section, is limited to

$$\pm \frac{1}{2}$$

of the DCO CKV clock cycle,  $T_{\nu}$ . For wireless applications, 50 a finer phase resolution is required. This is achieved using time-to-digital converter (TDC). The TDC measures the fractional delay difference  $\epsilon$  between the reference clock and the next rising edge of the DCO clock. Using the TDC, the integer clock-domain quantization error is corrected by means of the 55 fractional error correction term computed by the TDC, where the time between the rising and falling edges of CKV and FREF follow the relationship below

$$\frac{T_V}{2} = \begin{cases} \Delta t_r - \Delta t_f & \Delta t_r \ge \Delta t_f \\ \Delta t_f - \Delta t_r & \text{otherwise} \end{cases}$$

(4)

Therefore, the total variable phase in the feedback path is 65  $R_{\nu}[k] - \epsilon[k]$ . As the iADPLL phase comparator is implemented in the frequency domain, which is mathematically

16

equivalent to the pure phase domain operation, the variable phase is differentiated 240 to estimate the variable frequency error. i.e..

$$f_{e}^{V}[k] = (R_{V}[k] - \epsilon[k]) - (R_{V}[k-1] - \epsilon[k-1])$$

(5)

FIGS. 7A and 7B illustrate normalization and edge skipping operation of the TDC. The dimensionless TDC normalizing factor output from inversion circuit 702 is represented as follows:

$$N_{TDC} = \frac{2^{W_F}}{\overline{T}_V / \Delta I_{ver}}$$

(6)

$N_{TDC}$  is a fixed-point representation of the inverse of the expected DCO period T<sub>V</sub> in units of inverter delays  $\Delta t_{res} = t_{inv}$ . It is obtained through long-term averaging 704 of  $T_{r}=2|\Lambda t - \Lambda t|$

(in inverter units) followed by inversion 702.

The averaging time constant could be as slow as the expected drift of the inverter delay, possibly due to temperature and supply voltage variations. The instantaneous value of the clock period  $T_{\nu}=2|\Delta t_r-\Delta t_r|$  is an integer but averaging results in addition of significant fractional bits to the integer estimate with longer operations.

$$\overline{T}_V = \frac{1}{N_{avg}} \sum_{k=1}^{N_{avg}} T_V[k]$$

<sup>(7)</sup>

Note that each doubling of the accumulation length  $N_{avg}$ would add one bit to the  $T_V$  resolution.

It was experimentally confirmed that accumulating 128 clock cycles would produce accuracy within 1 ps of the inverter delay. The length of the operation is chosen to be a power of 2 since the division by the number of samples  $N_{avg}$  could now be replaced with a simple shift-right operation. Of course, other embodiments using a different technology or process point may use a different number of accumulations. Resampling Operation in the iADPLL

FIGS. 8A and 8B illustrate a conceptual view of data resampling using a sample rate converter 802. This section describes the resampling operations done in the iADPLL on the reference path and the phase error feeding into the loop filters. The sample rate conversion (SRC) or resampling is the mechanism with which data can be handed-off between digital systems (or circuits) which can have independent asynchronous clocks, such as example system-1 804 and system-2 806. The choice of the resampling mechanism determines the fidelity of the signal as it is passed from one clock domain to the other. The resampling operation can be as simple as a having a set of boundary registers on both the clock-domains, known as zero-order hold, ZOH; may contain linear polynomial interpolation, known as first-order hold; or more advanced polynomial filtering schemes such as Gardner, Lagrange, or Cubic Spline interpolations to name a few. For a resampler, the maximum difference in sample times indicated by 808 and the rate of change in the sampled signal determine how faithfully the output signal  $d_{OUT}[k]$  tracks the input 60 signal d<sub>IN</sub>[n].

In case of iADPLL, the two clock domains around the resampling domains are either the reference clock (FREF) or the retimed reference clock (CKR) and the CKV-derived clock. Although these two clocks are in general asynchronous to each other, the CKV being the output of iADPLL has a known relationship with FREF, which is tracked by the variable phase in the feedback path of the iADPLL. This infor-

mation is used to efficiently resample the data between the above mentioned clock domains.

FIG. 9A is a magnitude response plot and FIG. 9B is a phase response plot for the zero-order hold (ZOH) 254 and first-order hold (FOH) 256 resamplers of the iADPLL of FIG. 5 2. The resampling operation in a closed loop control system such as the iADPLL, designed with a focus on cellular RF systems is challenging as sophisticated higher-order interpolation schemes can become very expensive to implement. On the other hand, a control system utilizing a resampler essen- 10 tially becomes a multi-rate system, whose mathematical analysis is quite complicated. Therefore, for the iADPLL design, different resampling schemes were carefully analyzed and it was determined that due to very heavy filtering in the iADPLL loop filter, linear resampling (or FOH) is adequate for the iADPLL phase domain resampling. FIG. 9A shows the frequency response of both the ZOH 254 and the FOH 256 resamplers for a data injection rate of FREF (38.4 MHz in this case). The FOH has been implemented as a symmetric delayed interpolator with its co-efficient  $\eta = \frac{1}{2}$ . It can be seen that the FOH provides much more in-band filtering as compared to ZOH. The 3-dB cut-off frequency for ZOH is approx 17 MHz, while for FOH, it is approx 12 MHz. This reduces the possible impact of any aliasing that might be present in the iADPLL phase error due to the many noise sources that can potentially contaminate the DCO spectrum, <sup>25</sup> such as the processor clock, current spikes in the power management system, etc. Moreover the minimum rejection above FREF is -13.26 dB for ZOH and -26.5 dB for FOH. Please, note that the IIR filters which are a part of the iADPLL loop filter are typically set in the range of 1-2 MHz, therefore for a 30 spectral offset of 10 MHz, the phase error noise gets suppressed by 18.3 dB for ZOH and 19.5 dB for FOH, while the in-band aliased noise will be only 12 dB down for ZOH>24 dB lower for FOH.

Resampling of the Reference Feed Modulation

In this two point modulation scheme, the reference modulation input is the phase modulation compensation input, i.e., the reference modulation input cancels the phase modulation in the DCO output being feedback to the phase detector. Recall that the DCO was modulated using the direct point input. The reference modulation FCW is received from the DTX **250** at the LO-derived clock rate and needs to be resampled to the FREF domain at which the frequency/phase detector of the iADPLL operates, see FIG. **2**. After careful analysis and to preserve area, it was deemed adequate that ZOH resampling is adequate on the FCW signal.

In various embodiments, two different ZOH implementations may be used. In option I, the resampling is done in the phase domain, the impact of differentiation (which is a highpass filter to convert phase to frequency) is evident in the output spectrum. This can be problematic in case the phase 50 modulation has tonal content, which may get amplified. Therefore option II, in which the ZOH resampling 254 takes place after differentiation 252 was adopted for the present embodiment. In this case the resampler output spectrum is flat. Note that use of ZOH at the reference modulation input 55 introduces some aliasing. Note that the iADPLL variable phase accumulation also integrates the DCO variable phase over a period of reference frequency, which also produces aliasing in the feedback to the phase detector. The two aliased signals cancel each other substantially up to Fref/2, beyond 60 which the residual aliasing is below the sensitivity floor for the iADPLL and gets attenuated by the phase error signal processing of the iADPLL.

Resampling of the iADPLL Phase Error

FIG. **10**A is a simple block diagram and FIG. **10**B is a more detailed schematic of phase error resampler **256** of FIG. **2**. <sup>65</sup> The frequency error detector and the phase error accumulator operate on fixed rate retimed reference clock i.e. CKR. The

iADPLL loop filter **222** operates on an LO-derived clock domain, ie CKV. Therefore, the phase error needs to be resampled from this fixed rate clock domain into an RF-derived variable rate clock domain (CKV) before it is sent to the digital loop filter. The iADPLL output carries phase modulation in a polar TX. Phase resampler **256** helps to accomplish this functionality by using PLL variable phase information. Variable phase signals **1014** from the PLL carries the phase relationship information between the reference clock FREF and variable clock CKV. In Mu generator **1002**, this information is used to calculate Mu values required for interpolating the phase error to a higher frequency variable rate clock, as illustrated in FIG. **10**C.

The phase resampler performs 1<sup>st</sup> order linear interpolation on phase error signal **1006** in interpolator **1004**. The phase error resampler is implemented using a pair of FIFO's **1016**, **1018** to correctly interpolate phase error from fixed rate reference clock (CKR) **1010** to RF derived variable rate clock (CKVDx) **1012**. FIFO depth is set appropriately to support multiple variable rate clock domains for LOOP\_FILTER blocks of CKV/32, CKV/64, CKV/128 and also to support any reference clock frequency between 8 MHz and 38.4 MHz. Using FIFO's also eliminates the effects of CKR jitter on iADPLL performance.

MEM\_DLO\_RATE is set according to the desired division factor of the variable rate clock frequency for the LOOP\_FIL-TER blocks. MEM\_DLO\_RFCW is a normalization which needs to be calculated and set for the resampler to correctly calculate Mu values, based on the measured variable phase. This is a fractional value which represents the ratio between the divide factor of loop filter clock rate from CKV and FCW. For example, for a division factor of 32, this value will be 32/FCW.

This linear interpolation resampler can be configured to operate as a zero order hold resampler by setting MEM\_RE-SAMPLER\_EN=0.

When the spectrum of phase error carries a tone, resampling using a ZOH resampler may result in spectral regrowth. This spectral regrowth will be somewhat mitigated by the IIR filters in the higher-order iADPLL loop filter. However, as mentioned above, the cumulative attenuation using ZOH is approximately 13 dB less than FOH. On the contrary, using FOH for phase error resampling there is no spectral regrowth for the same input signal. Moreover the phase error noise also gets more attenuation in this mode. Note that after resampling of the PHE, the sampling frequency (or rate) for the signal gets translated to an RF-derived clock domain. Since PHE signal was originally accumulated at the FREF (or CKR) rate, its magnitude needs to be appropriately adjusted for the change of sampling rate. An explicit scaling to this effect is avoided in the resampler to save area. This scaling is incorporated later into the proportional and integral gain co-efficients of the PI controller in the iADPLL.

FIG. 11 is a block diagram of loop filter 222 for the iAD-PLL of FIG. 2. The Loop Filter's main input is the PHA-SE\_ERR signal 1008 output from the RESAMPLER block 256. Its main function is to first filter the phase error signal and then feed the filtered phase error signal to the proportional-integral controller (equivalent of type-II operation in an analog PLL) of the DCO. Note that the applied proportional and integral gains include DCO gain normalization for each of the DCO capacitor banks. The loop filter outputs TUNE\_PLL, which is the tuning word contribution due to the PLL. This is added (not shown on FIG. 11, but shown on FIG. 2 by adder 224) with TUNE\_TX (the feed-forward modulation injection) in the DCO interface (DCOIF) block to produce the composite OTW word (as shown in FIG. 2).

The proportional part **1192** of the iADPLL loop has a gain alpha, which is used in both type-I (used for the DCO PVT and Acquisition bank tuning) and type-II (used for DCO tracking bank tuning) operational modes of iADPLL. iAD-PLL can have different programmable alpha coefficients that can be used based on the operational mode.

The four IIR filters **1196** exist to filter the noisy PHA-SE\_ERR signal. All four IIR stages are similar with following 5 first-order transfer function:

$$y[n] = 2^{-\lambda} *x[n] + (1 - 2^{-\lambda}) *y[n - 1]$$

(8)

where lambda is a programmable value and can take any value from 0 to 7.

The integral loop **1194** is intended to only work in tracking mode once the proportional loop is already quite close to the desired channel frequency. This is followed to minimize the overall settling time of iADPLL, otherwise, there is no hardware limitations forcing this to only be used during tracking. <sup>15</sup> By adding an integrator to the loop, the loop will work to zero out the phase error. To prevent this long settling, the integral loop samples the current IIR filtered PHASE\_ERR and uses the result to subtract **1198** from subsequent phase error samples. This results in a new offset error signal that can be <sup>20</sup> forced to zero deviation by the integral control. The offset error value is then accumulated by the digital integrator and multiplied by the integral gain, rho, before it is added to the proportional correction.

FIG. **12**A shows a z-domain, frequency mode model of the <sup>25</sup> iADPLL, i.e., the input and the output of the iADPLL are in terms of frequency units. The model includes phase detector module **1218**, loop filter module **1222**, normalized DCO module **1270** and feedback TDC/PVL module **1242**. The loop filter **1222** for iADPLL comprises four independently con-<sup>30</sup> trolled IIR stages and a proportional-integral (PI) controller. Eq. (9) is a linearized z-domain model that includes the four cascaded single-stage IIR filters, each with an attenuation factor  $\lambda_i$ , where i=0... 3 as well as the proportional and integral parts of the loop. The loop filter operates at the <sup>35</sup>  $f_{VD} \cong f_V/32$  rate, where  $f_V$  is the DCO output frequency.

$$H_{loop}(z) = \overline{\alpha} \cdot \prod_{l=0}^{3} \frac{\lambda_i}{1 + (1 - \lambda_i)z^{-1}} + \overline{\rho} \cdot \frac{z^{-1}}{1 - z^{-1}}$$

(9)

40

FIGS. **12**B and **12**C are open-loop amplitude and phase transfer functions of the iADPLL of FIG. **12**A with default loop settings,  $\alpha = 2^{-7}$ ,  $\rho = 2^{-16}$ ,  $\lambda = [2^{-3} 2^{-5} 2^{-5} 2^{-5}]$  and integral gain operating on resampled PHE signal.

Alternately, iADPLL also supports a mode in which the integral part of the PI controller also operates on filtered phase error computed by operating a set of cascaded IIR filters on the resampled PHE signal. The main advantage of this mode is that as the integral part operates on an error signal, which has undergone low pass filtering after resampling (identical to the proportional part) resulting in better group delay equalization of the two paths. Note that in this mode the phase margin of the iADPLL under similar conditions will be sacrificed. In this mode, the loop filter can be expressed as 55 follows:

$$H_{loop}(z) = \left(\overline{\alpha} + \overline{\rho} \cdot \frac{z^{-1}}{1 - z^{-1}}\right) \cdot \prod_{l=0}^{3} \frac{\lambda_i}{1 + (1 - \lambda_i)z^{-1}} \tag{10}$$

FIGS. **12**D and **12**E are plots of z-domain phase response with open-loop amplitude and phase transfer functions of the iADPLL of FIG. **12**A with default loop settings,  $\alpha = 2^{-7}$ ,  $\rho = 65$  $2^{-16}$ ,  $\lambda = [2^{-3} 2^{-5} 2^{-5} 2^{-5}]$  and integral gain operating on filtered PHE signal.

$$\frac{\phi_R^n}{2\pi}, \frac{\phi_V^n}{2\pi}$$

and  $\frac{\phi_{TDC}^n}{2\pi}$

are the reference, variable (DCO) and the TDC error source contributions, respectively. For simplicity, the feedforward path comprises of the DCO represented only as the frequency scaling factor  $K_{DCO}$ . For simplicity, the phase accumulation of the DCO has been modeled as a discrete integrator running at  $f_{VD}$  rate in the feedback path. Note that the DCO integration can also be represented using the Bilinear/Tustin transformation. This is equivalent to running the DCO at the  $f_V$  rate and then scaling the phase accumulation at the output to the  $f_{VD}$  rate.

$$H_{DCO}(z) = \frac{z^{-1}}{1 - z^{-1}} \cdot \frac{1}{f_{VD}}$$

(11)

The simplified feedforward transfer function of the loop is

$$H_{FF}(z) = \frac{z^{-1}}{1 - z^{-1}} \cdot \left(\overline{\alpha} \cdot \prod_{l=0}^{3} \frac{\lambda_i}{1 + (1 - \lambda_i)z^{-1}} + \overline{\rho} \cdot \frac{z^{-1}}{1 - z^{-1}}\right) \cdot \frac{f_{VD}}{f_R} \cdot r$$

(12)

where r is the dimensionless ratio representing the DCO gain estimation error.

The transfer function of the feedback components is

ŀ

ŀ

$$I_{FB}(z) = \frac{z^{-1}}{1 - z^{-1}} \cdot \frac{1}{f_{VD}} \cdot 1 - z^{-1} = \frac{z^{-1}}{f_{VD}}$$

(13)

The closed loop transfer function for the reference is lowpass with the gain multiplier N=FCW, i.e.,

$$H_{cl,REF}(z) = N \cdot \frac{H_{FF}(z)}{1 + H_{FF}(z) \cdot H_{FB}(z)}$$

(14)

The closed loop transfer function for the TDC is lowpass. Neglecting the accumulation and the differentiation operations in the feedback path, we can write the closed-loop transfer function for TDC as

$$H_{cl,TDC}(z) = \frac{H_{FF}(z)}{1 + H_{FF}(z)}$$

(15)

The closed loop transfer function for the direct-point injection into the DCO is highpass in nature and is given by

$$A_{cl,DCO}(z) = \frac{1}{1 + H_{FF}(z) \cdot H_{FB}(z)}$$

(16)

FIG. 12F is a block diagram of the iADPLL loop filter 1222 with alpha gear-shifting. The amplitude and phase transfer function differences using the iADPLL loop filters in the configurations as captured in Eq. (9) and (10), also see FIGS. 12B-12E, impacts the ADPLL closed loop performance as well. FIG. 12G is a plot showing the closed loop iADPLL transfer function magnitude response when using a raw PHE

20

10

signal **1280** for integral control, and when using a filtered PHEF signal **1282** for integral control. FIG. **12**H is a plot showing the closed loop iADPLL transfer function phase response using both a raw PHE signal and a filtered PHEF signal for integral control;

Essentially the use of filtered phase error for the integral control part of the iADPLL loop filter eliminates the amplitude and phase transfer function abruption (introduced due to resampling in raw PHE signal). However, note that physically the kink **1284** shown in the reference iADPLL transfer function is 80 dB below the PLL unity gain and as such does not produce any stability concerns for iADPLL loop bandwidth extending up to a few hundreds of kilohertz. Note, that under typical operating conditions, iADPLL loop bandwidth will be in the range of 20-60 kHz only.

Note that all the transfer functions are a function of the DCO frequency  $f_V$  or its derivatives, such as CKVDx

The primary advantage of operating the iADPLL on the  $f_{VD}$  frequency is the improved spectrum and better rejection of the reference spurs. However, this results in the iADPLL loop response to vary as a function of DCO frequency for fixed iADPLL tuning parameters. Although this iADPLL BW variation is quite small, it can be taken care of by optimal tuning of the iADPLL loop parameters as a function of the DCO output frequency. Note that for the entire GSM/EDGE tuning range this variation is less than 4% of PLL BW and less than 2% of the iADPLL phase margin.

Some operating points computed for GSM modulation using the model presented in equations (9)~(16) are shown in Table 2.

| TABLE | 2 |

|-------|---|

|-------|---|

| iADPLL Loop Parameters - Channel Frequency = 1800 MHz |         |         |         |       |     |                          |                        |                          |                             |                              |                            |