# DIGITAL DEEP-SUBMICRON CMOS FREQUENCY SYNTHESIS FOR RF

# WIRELESS APPLICATIONS

# APPROVED BY SUPERVISORY COMMITTEE:

Poras T. Balsara, Chair

Dinesh Bhatia

William Frensley

William Krenik

Mehrdad Nourani

© Copyright 2002

Robert Bogdan Staszewski

All Rights Reserved

To my parents: Kazimierz and Irena

and my wife Sunisa

# DIGITAL DEEP-SUBMICRON CMOS FREQUENCY SYNTHESIS FOR RF WIRELESS APPLICATIONS

by

Robert Bogdan Staszewski, B.S.E.E., M.S.E.E.

## DISSERTATION

Presented to the Faculty of

The University of Texas at Dallas

in Partial Fulfillment

of the Requirements

for the Degree of

# DOCTOR OF PHILOSOPHY IN ELECTRICAL ENGINEERING

The University of Texas at Dallas

August, 2002

#### ACKNOWLEDGEMENTS

My sincere thanks and regards to my advisor Prof. Poras T. Balsara, whose constant support and patient guidance provided a clear path for my research. His original suggestion to work on an all-digital phase-locked loop architecture was, in retrospect, extremely valuable in both my academic and professional careers.

My thanks to Prof. Dinesh Bhatia, Prof. William Frensley and Prof. Mehrdad Nourani for serving on my committee, reading my dissertation and making useful comments. My thanks to Prof. Murat Torlak for originally serving on my committee.

Special thanks to Dr. Bill Krenik for serving on my committee, sponsoring the project at Texas Instruments, and providing very useful feedback throughout from the very days the idea was conceived.

I would like to acknowledge and thank Dr. Dirk Leipold, a physicist and my colleague at Texas Instruments, for many long and fruitful discussions leading to refinements of the digital RF architecture. His orthogonal thinking and expertise in process technology are unparalleled.

I would also like to acknowledge and thank Dr. Chih-Ming Hung for his detailed circuit design and layout supervision of the digitally-controlled oscillator and the RF power amplifier. Many thanks to Ken Maggio, manager of the RF-CMOS group in Texas Instruments for his feedback and day-to-day activities to make this testchip a success.

I wish to acknowledge valuable technical discussions with Stanley Goldman, a recognized PLL expert at Texas Instruments.

I wish to give special thanks to my wife, Sunisa, for her love, support and patience without which I could not have endured.

Finally, I would like to thank Prof. Dale Byrne for encouragement and guidance in my last undergraduate year at UT Dallas when he was my senior project advisor.

# DIGITAL DEEP-SUBMICRON CMOS FREQUENCY SYNTHESIS FOR RF

## WIRELESS APPLICATIONS

Publication No. \_\_\_\_\_

Robert Bogdan Staszewski, Ph.D. The University of Texas at Dallas, 2002

Supervising Professor: Poras T. Balsara

Traditional designs of commercial frequency synthesizers for multi-GHz mobile RF wireless applications have almost exclusively employed the use of a charge-pump *phase-locked loop* (PLL), which acts as a *local oscillator* (LO) for both transmitter and receiver. Unfortunately, the circuits and techniques required are extremely analog intensive and utilize a process technology which is incompatible with a digital baseband.

The author's research related to low-power and low-cost radio solutions has led to a novel *all-digital* synthesizer architecture that exploits strong advantages of a deep-submicron digital CMOS process technology as well as advances in digital *very large scale of integration* (VLSI) field. Its underlying theme is to maximize digitally-intensive implementation by

operating in a synchronous phase domain. Chief benefit obtained with this architecture is to allow to integrate the RF front-end with the digital back-end onto a single silicon die.

The presented frequency synthesizer naturally combines the transmitter modulation capability implemented in an all-digital manner. The pulse-shaping transmit filter and a class-E power amplifier are included to demonstrate the use of the proposed synthesizer in a targeted RF application.

The ideas developed in this research project have been implemented in a Texas Instruments' deep-submicron CMOS process and demonstrated in a working silicon of BLUETOOTH transmitter for short-range communications.

# TABLE OF CONTENTS

| ACKNC   | WLED    | GEMENTS                                                   | v    |

|---------|---------|-----------------------------------------------------------|------|

| ABSTR   | ACT     |                                                           | vii  |

| LIST OI | F FIGUI | RES                                                       | XV   |

| LIST O  | F TABL  | ES                                                        | xxii |

| СНАРТ   | ER 1    | INTRODUCTION                                              | 1    |

| 1.1     | Motiva  | ation                                                     | 1    |

|         | 1.1.1   | CMOS vs. Traditional RF Process Technologies              | 1    |

|         | 1.1.2   | Deep-Submicron CMOS                                       | 2    |

|         | 1.1.3   | Digitally-Intensive Approach                              | 4    |

|         | 1.1.4   | System Integration                                        | 6    |

|         | 1.1.5   | System Integration Challenges for Deep-Submicron CMOS     | 8    |

| 1.2     | Freque  | ency Synthesizer as an Integral Part of an RF Transceiver | 9    |

|         | 1.2.1   | Noise in Oscillators                                      | 11   |

|         | 1.2.2   | Transmitter                                               | 15   |

|         | 1.2.3   | Receiver                                                  | 17   |

| 1.3     | Toward  | ds the Direct Transmit Modulation                         | 19   |

| 1.4     | Freque  | ency Synthesis                                            | 24   |

|         | 1.4.1   | Definition                                                | 24   |

|         | 1.4.2   | Frequency Synthesis Techniques                            | 25   |

|         | 1.4.3   | Frequency Synthesizers for Mobile Communications          | 30   |

|         | 1.4.4   | All-Digital PLL Approach                                  | 39   |

| 1.5     | Main (  | Contributions of this Work                                | 42   |

| 1.6   | Organization of the Dissertation                            | 45  |

|-------|-------------------------------------------------------------|-----|

| СНАРТ | ER 2 DIGITALLY-CONTROLLED OSCILLATOR (DCO)                  | 47  |

| 2.1   | Discrete-Time Oscillator                                    | 47  |

| 2.2   | Digital Control of Oscillating Frequency                    | 48  |

| 2.3   | Open-Loop Narrowband Digital-to-Frequency Conversion        | 59  |

| 2.4   | Implementation                                              | 66  |

| 2.5   | Time-Domain Mathematical Model of the DCO                   | 70  |

| 2.6   | Summary                                                     | 74  |

| СНАРТ | ER 3 NORMALIZED DCO                                         | 75  |

| 3.1   | Overview                                                    | 75  |

| 3.2   | Oscillator Transfer Function and Gain                       | 76  |

| 3.3   | DCO Gain Estimation                                         | 77  |

| 3.4   | DCO Gain Normalization                                      | 77  |

| 3.5   | Principle of Synchronously-Optimal DCO Tuning Word Retiming | 79  |

| 3.6   | Time Dithering of the DCO Tuning Input                      | 81  |

|       | 3.6.1 Oscillator Tune Time Dithering Principle              | 81  |

|       | 3.6.2 Direct Time Dithering of the Tuning Input             | 82  |

|       | 3.6.3 Update Clock Dithering Scheme                         | 86  |

| 3.7   | Implementation of PVT and Acquisition DCO Bits              | 87  |

| 3.8   | Implementation of Tracking DCO Bits                         | 92  |

|       | 3.8.1 High-speed Dithering of the Fractional Varactors      | 93  |

|       | 3.8.2 Dynamic Element Matching of the Varactors             | 99  |

|       | 3.8.3 DCO Varactor Rearrangement                            | 101 |

| 3.9   | Time-Domain Model                                           | 104 |

| 3.10  | Summary                                                     | 105 |

| СНАРТ |                                                             | 107 |

| 4.1   | Overview                                                    | 107 |

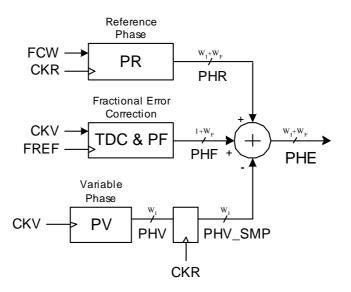

| 4.2   | Phase Domain Operation                                      | 108 |

| 4.3   | Reference Phase Retiming                                    | 111 |

| 4.4  | Phase Detection                                                  |

|------|------------------------------------------------------------------|

| 4.5  | Integer-Domain Operation                                         |

| 4.6  | Modulo Arithmetic of the Reference and Variable Phases           |

| 4.7  | Variable Phase Accumulator                                       |

| 4.8  | Fractional Error Estimator – Time-to-Digital Converter           |

| 4.9  | Fractional Division Ratio Compensation                           |

| 4.10 | Frequency Reference (FREF) Retiming by the DCO Clock             |

|      | 4.10.1 Sense-amplifier-based Flip-flop                           |

|      | 4.10.2 General Idea of Clock Retiming                            |

|      | 4.10.3 Implementation                                            |

| 4.11 | TDC Resolution Effect on the Estimated Frequency Resolution      |

| 4.12 | Loop Gain Factor                                                 |

| 4.13 | Phase Error Dynamic Range                                        |

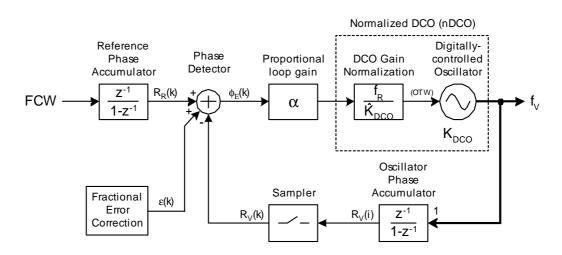

| 4.14 | Phase-Domain ADPLL Architecture                                  |

| 4.15 | PLL Frequency Response                                           |

|      | 4.15.1 Conversion between s-domain and z-domain                  |

| 4.16 | Noise and Error Sources                                          |

| 4.17 | Type-II ADPLL loop         157                                   |

|      | 4.17.1 PLL Frequency Response of Type-II Loop                    |

| 4.18 | Higher-order ADPLL Loop                                          |

| 4.19 | Non-linear Differential Term of the ADPLL Loop                   |

| 4.20 | DCO Gain Estimation by Using the PLL Loop                        |

| 4.21 | Gear-shifting of the PLL Loop Gain                               |

|      | 4.21.1 Proposed Idea                                             |

|      | 4.21.2 Autonomous Gear-shifting Mechanism                        |

|      | 4.21.3 Extended Gear-shifting Scheme with Zero-Phase Restart 170 |

|      | 4.21.4 Zero-Phase Restart Mechanism                              |

|      | 4.21.5 Simulation Runs                                           |

| 4.22 | Summary                                                          |

| СНАРТ |                                                                     |       |

|-------|---------------------------------------------------------------------|-------|

|       | ATION                                                               | 178   |

| 5.1   | Overview                                                            | . 178 |

| 5.2   | Oscillator Frequency Modulation                                     | . 179 |

|       | 5.2.1 Hybrid of Predictive/Closed PLL Loop Operation                | . 180 |

|       | 5.2.2 Prior Art                                                     | . 180 |

|       | 5.2.3 Direct Oscillator Modulation with the PLL Loop Compensation . | . 181 |

|       | 5.2.4 Partially-Direct Oscillator Modulation                        | . 184 |

|       | 5.2.5 Improved Structure                                            | . 184 |

|       | 5.2.6 Generalized Architecture                                      | . 185 |

| 5.3   | GFSK Pulse Shaping of the Transmit Data                             | . 186 |

| 5.4   | Just-in-time DCO gain calculation                                   | . 193 |

| 5.5   | Power Amplifier                                                     | . 195 |

| 5.6   | Digital Amplitude Modulation                                        | . 199 |

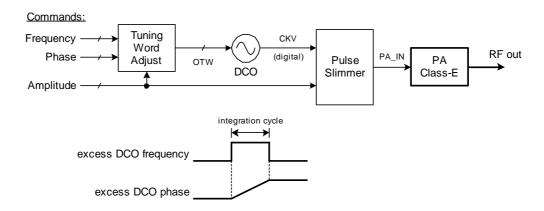

|       | 5.6.1 Discrete Pulse Sliming Control                                | . 202 |

|       | 5.6.2 Regulation of Transmitting Power                              | . 204 |

|       | 5.6.3 Tuning Word Adjustment                                        | . 205 |

|       | 5.6.4 Advantages                                                    | . 206 |

| 5.7   | Summary                                                             | . 207 |

| CHAPT |                                                                     |       |

| TIO   |                                                                     | 208   |

| 6.1   | Overview                                                            |       |

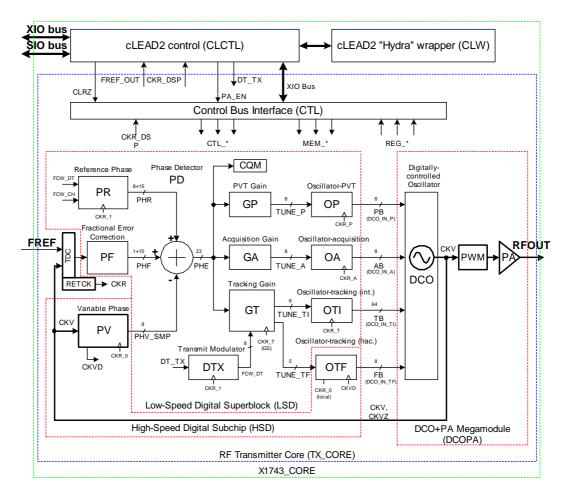

| 6.2   | Transmitter Core Implementation                                     |       |

| 6.3   | CMOS Process Parameters                                             |       |

| 6.4   | Chip                                                                | . 212 |

| 6.5   | Evaluation Board                                                    | . 212 |

| CHAPT | ER 7 BEHAVIORAL MODELING AND SIMULATION                             | 217   |

| 7.1   | Behavioral Modeling                                                 | . 217 |

| 7.2   | Simulation Methodology                                              | . 218 |

| 7.3   | Random Number Generator                                             | . 219 |

| 7.4   | Clock Jitter and Wander Effects                   | . 220 |

|-------|---------------------------------------------------|-------|

| 7.5   | Modeling of Metastability in Flip-Flops           | . 224 |

| 7.6   | Digital Blocks                                    | . 228 |

| 7.7   | Support of Digital Stream Processing              | . 229 |

| 7.8   | Simulation Results                                | . 230 |

|       | 7.8.1 Time-domain Simulations                     | . 230 |

|       | 7.8.2 "Frequency-deviation" Simulations           | . 232 |

|       | 7.8.3 Phase-domain Simulations of the Transmitter | . 234 |

|       | 7.8.4 Synthesizer Phase Noise Simulations         | . 235 |

| СНАРТ | ER 8 EXPERIMENTAL RESULTS                         | 240   |

| 8.1   | Overview                                          | . 240 |

| 8.2   | Measurement Equipment                             | . 240 |

| 8.3   | GFSK Transmitter Performance                      | . 241 |

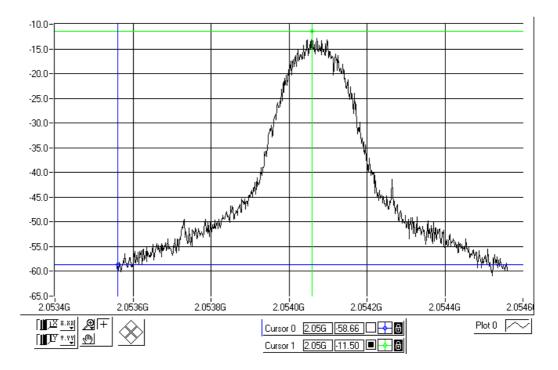

| 8.4   | Synthesizer Performance                           | . 245 |

| 8.5   | Synthesizer Switching Transients                  | . 248 |

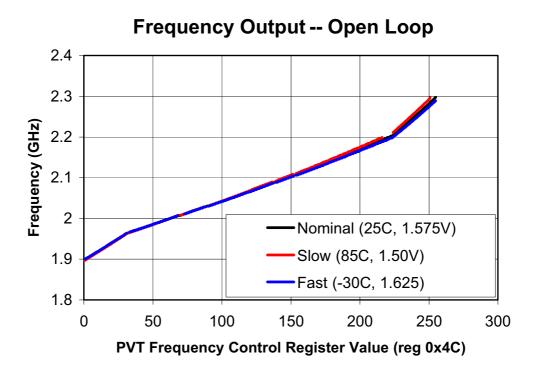

| 8.6   | DCO Tuning Characteristic                         | . 249 |

| 8.7   | DSP-driven Modulation                             | . 251 |

| 8.8   | Performance Summary                               | . 253 |

| 8.9   | Summary                                           | . 254 |

| СНАРТ | ER 9 CONCLUSION AND FUTURE RESEARCH               | 255   |

| 9.1   | Conclusion                                        | . 255 |

| 9.2   | Future Research                                   | . 257 |

| APPEN | DIX A SPURS DUE TO DCO SWITCHING                  | 259   |

| A.1   | Spurs Due to DCO Modulation                       | . 260 |

|       | A.1.1 Example I                                   | . 261 |

|       | A.1.2 Example II                                  | . 262 |

|       |                                                   |       |

| APPENDIX B OPERATION OF THE SYNCHRONOUS PHASE-DOMAIN ALL- |                                                             |       |

|-----------------------------------------------------------|-------------------------------------------------------------|-------|

| DIG                                                       | ITAL PLL SYNTHESIZER                                        | 263   |

| B.1                                                       | Basic definitions                                           | . 263 |

| B.2                                                       | Integer phase estimator                                     | . 265 |

|                                                           | B.2.1 Approximation bound of the timing interpolation error | . 265 |

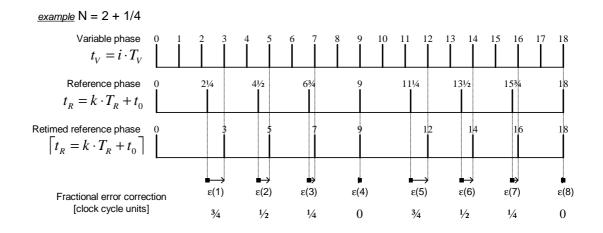

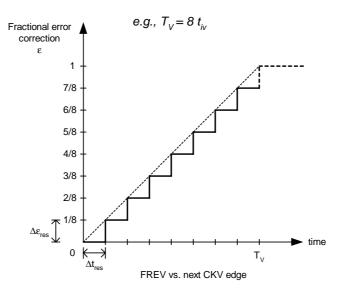

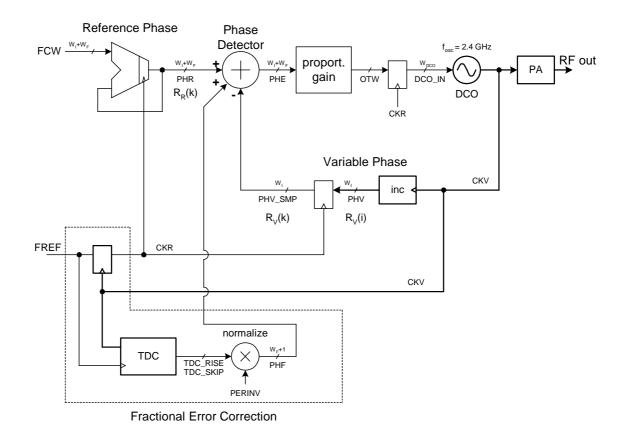

| B.3                                                       | Fractional error correction                                 | . 267 |

| B.4                                                       | Hardware implementation                                     | . 267 |

| APPEN                                                     | DIX C GAUSSIAN PULSE-SHAPING FILTER                         | 268   |

| APPEN                                                     | DIX D EXAMPLE VHDL SOURCE CODE                              | 270   |

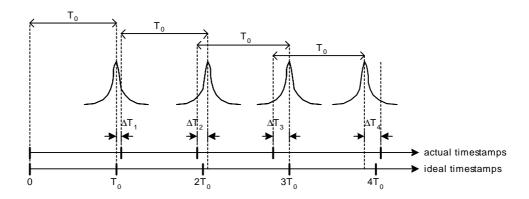

| D.1                                                       | DCO Level-2                                                 | . 270 |

| D.2                                                       | Period-controlled Oscillator (PCO)                          | . 274 |

| D.3                                                       | Tactical Flip-Flop                                          | . 278 |

| D.4                                                       | TDC Pseudo-thermometer Output Decoder                       | . 282 |

| REFERI                                                    | ENCES                                                       | 289   |

VITA

# LIST OF FIGURES

| 1.1  | Example in ultimate mobile wireless integration: single-chip BLUETOOTH | _  |

|------|------------------------------------------------------------------------|----|

|      | radio                                                                  | 7  |

| 1.2  | Channel hopping of a transmitted signal                                | 10 |

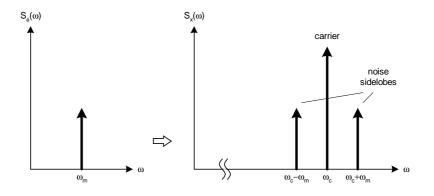

| 1.3  | Output spectrum of ideal and actual oscillators                        | 11 |

| 1.4  | Phase noise spectrum of an actual oscillator                           | 12 |

| 1.5  | Equivalence between PSD and single-sided phase noise                   | 14 |

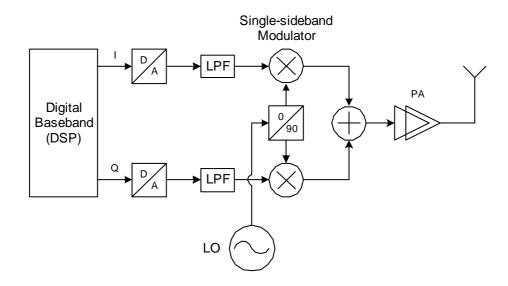

| 1.6  | Conventional direct up-conversion transmitter                          | 15 |

| 1.7  | The effect of LO phase noise in a transmitter                          | 16 |

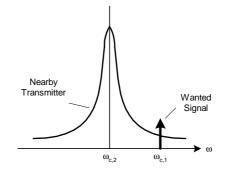

| 1.8  | Zero-IF receiver topology                                              | 17 |

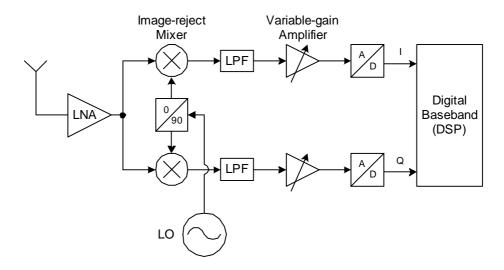

| 1.9  | The effect of LO phase noise in a receiver                             | 18 |

| 1.10 | PAM modulation with complex signals                                    | 19 |

| 1.11 | PAM modulation with I and Q baseband signals                           | 20 |

| 1.12 | PAM modulation with a direct phase and amplitude modulation            | 21 |

| 1.13 | GFSK modulation as a PAM modulation with constant envelope             | 22 |

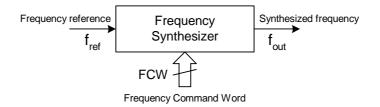

| 1.14 | Frequency synthesis                                                    | 24 |

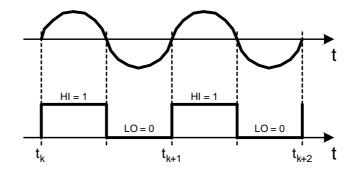

| 1.15 | Possible digital waveforms of a synthesizer                            | 24 |

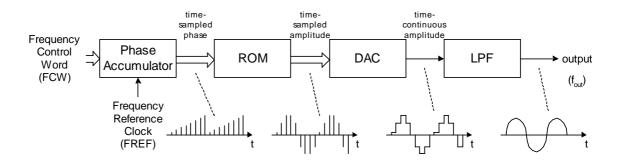

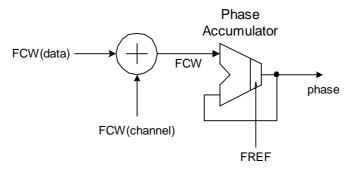

| 1.16 | Direct digital frequency synthesis (DDFS)                              | 26 |

| 1.17 | Phase accumulator front-end of the DDFS with frequency modulation ca-  |    |

|      | pability                                                               | 27 |

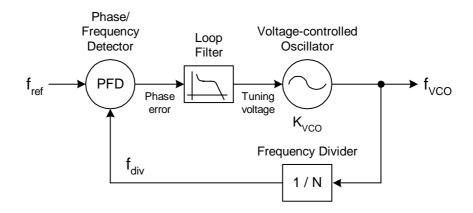

| 1.18 | Phase-locked loop (PLL)                                                | 28 |

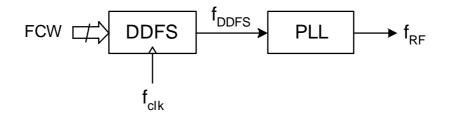

| 1.19 | Hybrid of DDFS and PLL                                                 | 29 |

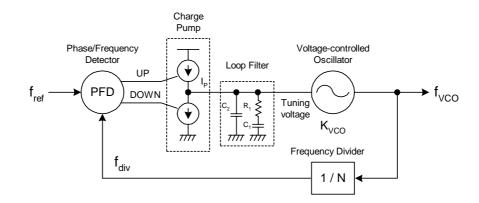

| 1.20 | Typical charge-pump-based PLL for RF wireless applications             | 31 |

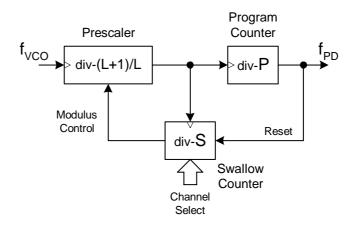

| 1.21 | Pulse swallow frequency divider                                        | 32 |

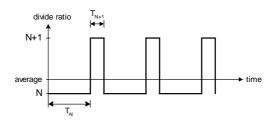

| 1.22 | Alternating divide ratio of fractional-N PLL                           | 34 |

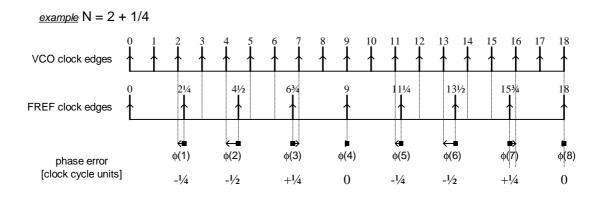

| 1.23 | Periodic and deterministic phase error in a fractional-N PLL           | 35 |

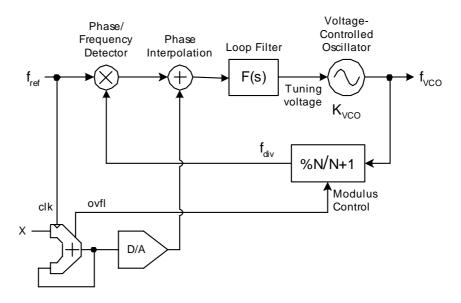

| 1.24 | Fractional-N PLL incorporating phase interpolation                                                                                                                                                  | 35 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

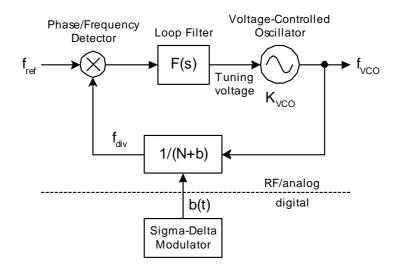

| 1.25 | Fractional-N synthesizer using a $\Sigma\Delta$ modulated clock divider                                                                                                                             | 36 |

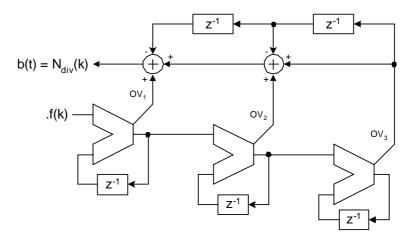

| 1.26 | MESH-3 $\Sigma\Delta$ digital modulator divider                                                                                                                                                     | 36 |

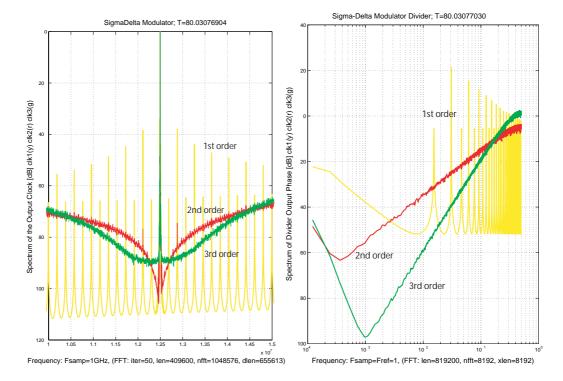

| 1.27 | $\Sigma\Delta$ divided clock: clock output spectrum (left), phase spectrum (right)                                                                                                                  | 37 |

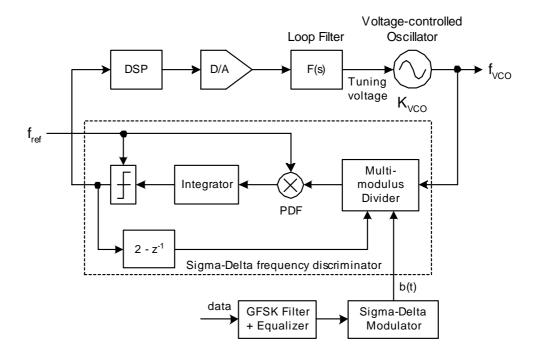

| 1.28 | Modulating wideband fractional-N synthesizer [34]                                                                                                                                                   | 39 |

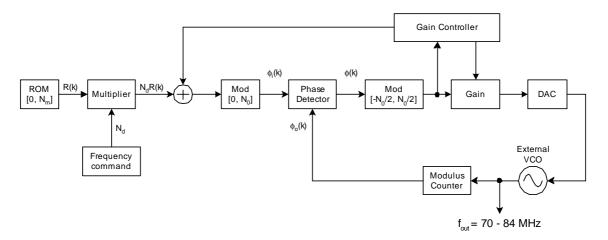

| 1.29 | Phase-domain PLL based on Kajiwara et al. [40]                                                                                                                                                      | 40 |

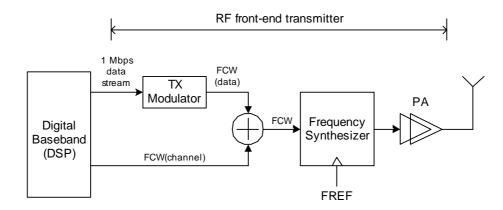

| 1.30 | Research scope: RF front-end of the synthesizer-based transmitter                                                                                                                                   | 43 |

| 2.1  | Idealized capacitance vs. voltage curves of a MOS varactor                                                                                                                                          | 49 |

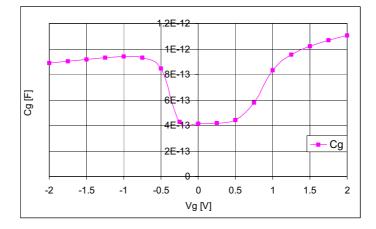

| 2.2  | Gate capacitance vs. gate voltage of a measured PMOS varactor: C035.a process, PPOLY/NWELL, inversion type, single-contacted gate, L=0.5 $\mu$ m, W=0.6 $\mu$ m, N=8 fingers x 12 x 2, freq=2.4 GHz | 49 |

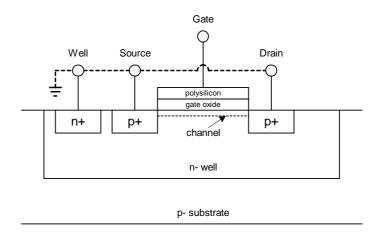

| 2.3  | Physical structure of a PMOS transistor used as a varactor when the source, drain and well tie-offs are tied to ground                                                                              | 50 |

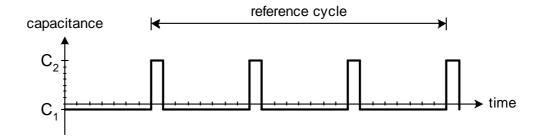

| 2.4  | DCO dithering by changing the discrete capacitance at high rate                                                                                                                                     | 53 |

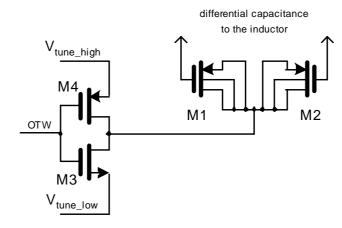

| 2.5  | Differential varactor and an inverting driver                                                                                                                                                       | 54 |

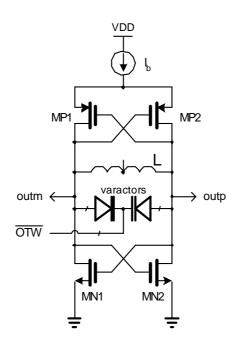

| 2.6  | Ideal schematic of the DCO oscillator                                                                                                                                                               | 55 |

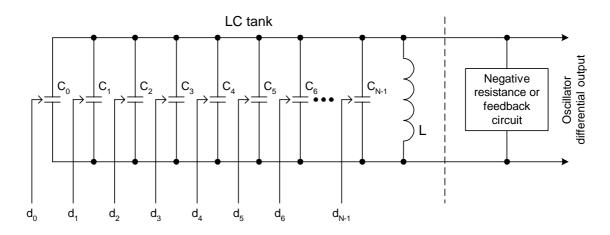

| 2.7  | LC-tank-based oscillator with switchable capacitors                                                                                                                                                 | 56 |

| 2.8  | Binary-weighted switchable capacitor of index $k$                                                                                                                                                   | 58 |

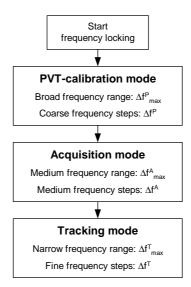

| 2.9  | Progression flowchart of the DCO operational modes                                                                                                                                                  | 61 |

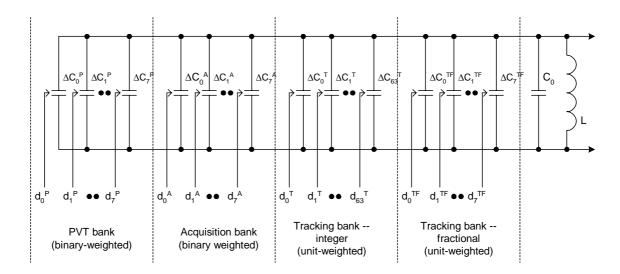

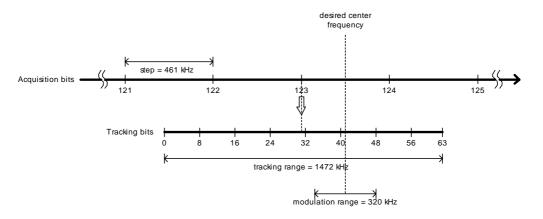

| 2.10 | LC-tank with dedicated capacitor banks                                                                                                                                                              | 63 |

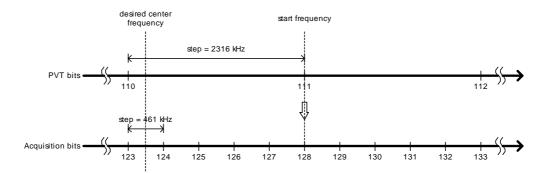

| 2.11 | Frequency transversal example for the implemented DCO: PVT to acquisition                                                                                                                           | 68 |

| 2.12 | Frequency transversal example for the implemented DCO: acquisition to tracking                                                                                                                      | 68 |

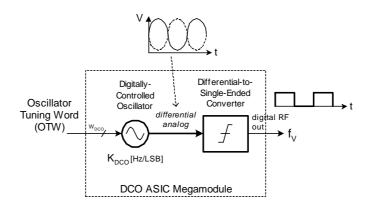

| 2.13 | DCO as an ASIC cell with digital I/O's                                                                                                                                                              | 69 |

| 2.14 | Frequency deviation as a clock period deviation                                                                                                                                                     | 70 |

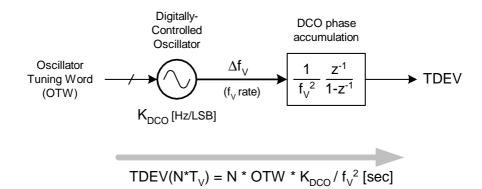

| 2.15 | Development of an accumulative timing deviation (TDEV)                                                                                                                                              | 72 |

| 2.16 | DCO time-domain model                                                                                                                                                                               | 73 |

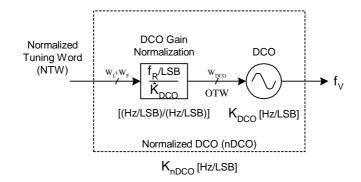

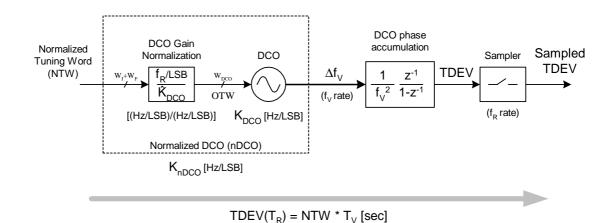

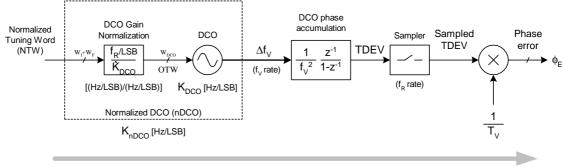

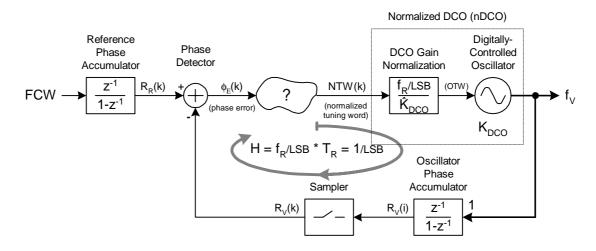

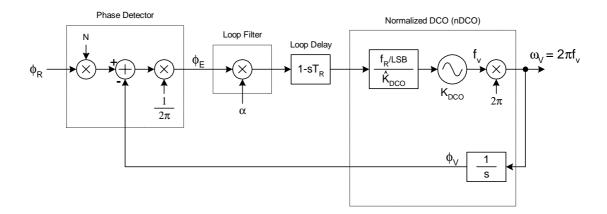

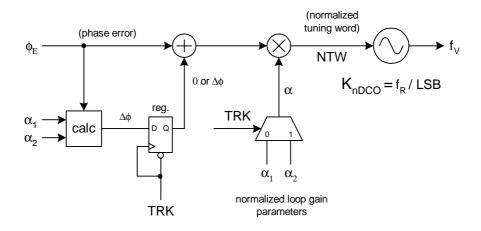

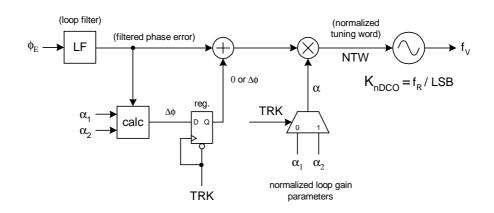

| 3.1  | Normalized DCO                                                                                                                                                                                      | 78 |

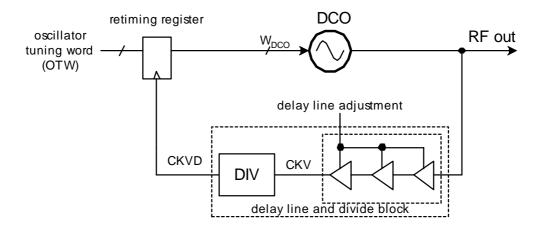

| 3.2  | Synchronously-optimal sampling and timing adjustment of the DCO input .                                                                                                                             | 79 |

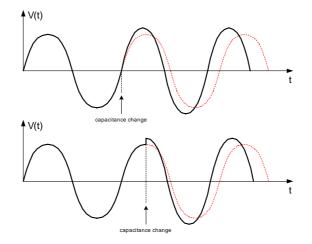

| 3.3  | Waveforms for capacitance change of an LC-tank oscillator                                                                                                                                           | 80 |

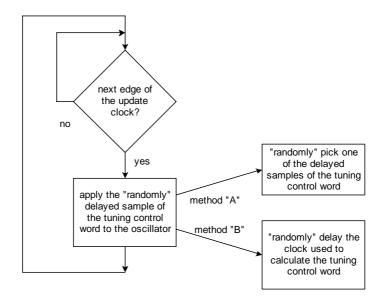

| 3.4  | Flowchart of the oscillator tune time dithering                                                                                                                                          | 82  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

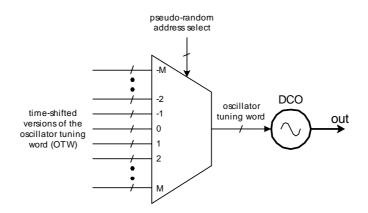

| 3.5  | Basic idea of discrete time dithering of the DCO tuning input                                                                                                                            | 82  |

| 3.6  | Time dithering method of the DCO tuning input through a multiplexer                                                                                                                      | 83  |

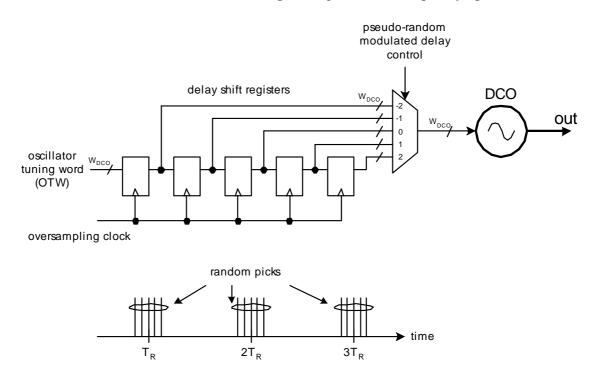

| 3.7  | Time dithering with the DCO synchronous tuning input retiming                                                                                                                            | 84  |

| 3.8  | Time dithering with an additional frequency reference retiming                                                                                                                           | 85  |

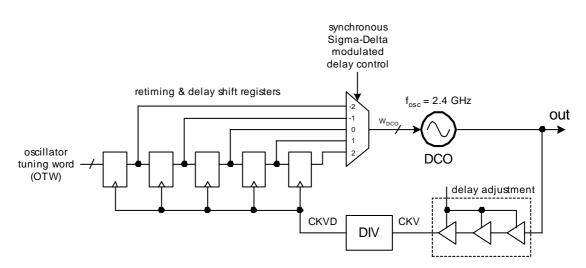

| 3.9  | Time dithering implementation of the update clock                                                                                                                                        | 86  |

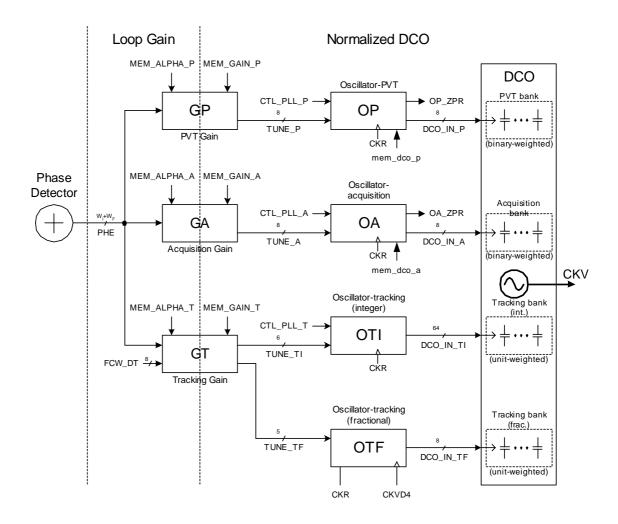

| 3.10 | DCO gain paths – implementational block diagram                                                                                                                                          | 88  |

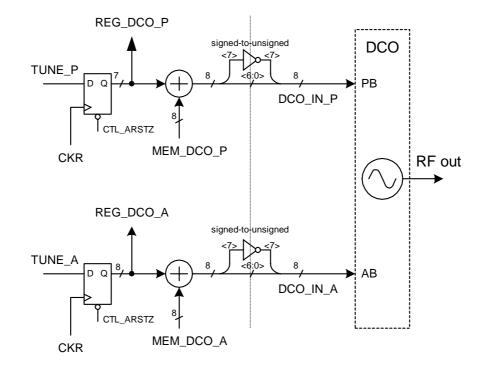

| 3.11 | Oscillator interface with the PVT and acquisition bits                                                                                                                                   | 89  |

| 3.12 | Control circuit of the oscillator PVT bits (OP)                                                                                                                                          | 90  |

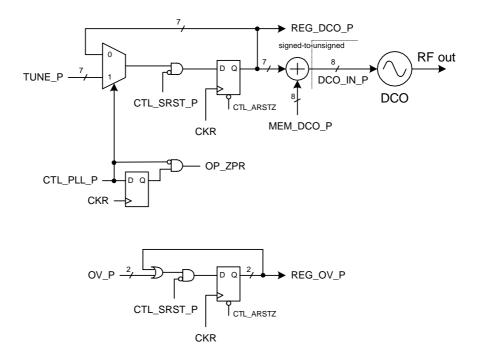

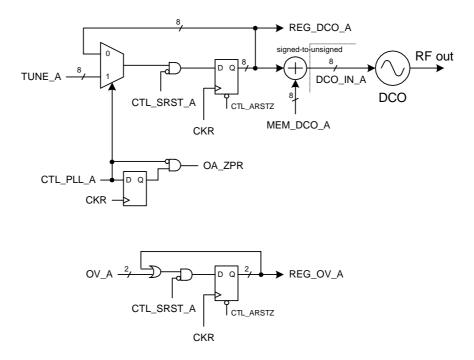

| 3.13 | Control circuit of the oscillator acquisition bits (OA)                                                                                                                                  | 91  |

| 3.14 | Improving frequency resolution with $\Sigma\Delta$ dither of DCO tracking bits $\ .\ .\ .$                                                                                               | 93  |

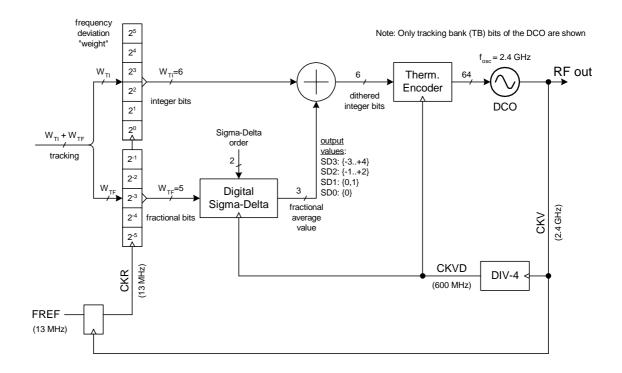

| 3.15 | MESH-3 $\Sigma\Delta$ digital modulator structure                                                                                                                                        | 96  |

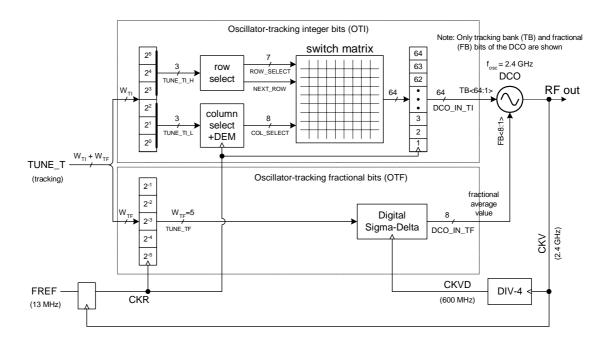

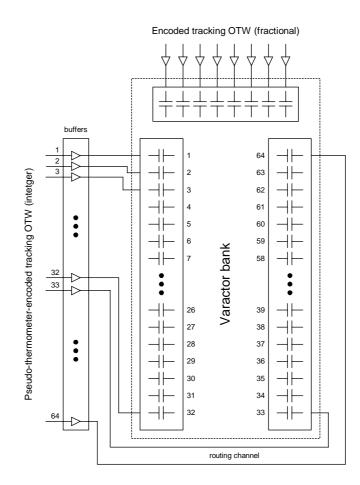

| 3.16 | Implementation block diagram of the DCO tracking bits (OTI + OTF) with DEM of the integer part and $\Sigma\Delta$ dithering of the fractional part                                       | 97  |

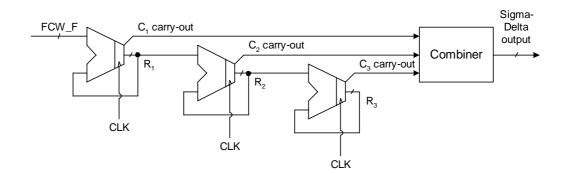

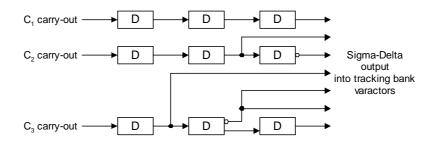

| 3.17 | $\Sigma\Delta$ modulator carry-out combiner structure                                                                                                                                    | 97  |

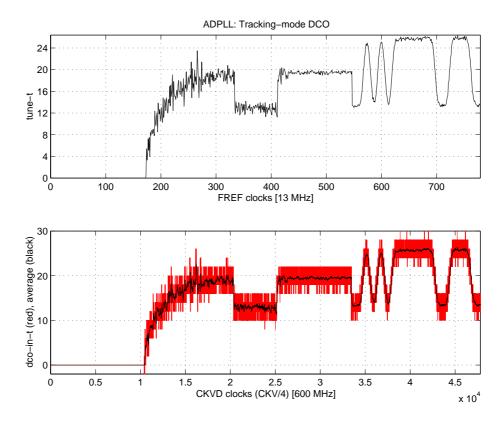

| 3.18 | Simulation plot using the $\Sigma\Delta$ modulation of the fractional part of the track-<br>ing tuning word; (top: fixed-point tuning word; bottom: decoded merged<br>DCO integer input) | 98  |

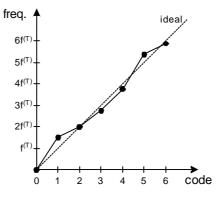

| 3.19 | Cumulative nonlinearity of the DCO tracking bits                                                                                                                                         | 99  |

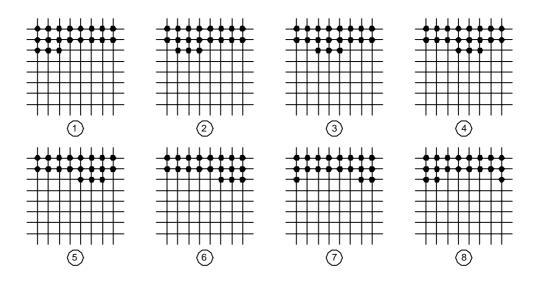

| 3.20 | Dynamic element matching through cyclic shift within a matrix row 1                                                                                                                      | 00  |

| 3.21 | Layout diagram of the tracking capacitors                                                                                                                                                | 02  |

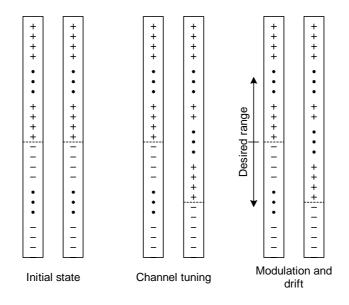

| 3.22 | Tracking capacitors rearrangement                                                                                                                                                        | 03  |

| 3.23 | nDCO time-domain model                                                                                                                                                                   | 04  |

| 3.24 | nDCO time-domain model with phase detection                                                                                                                                              | 05  |

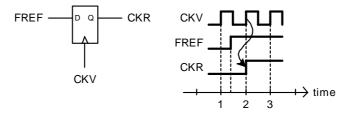

| 4.1  | Concept of synchronizing the clock domains by retiming the frequency reference (FREF)                                                                                                    | 111 |

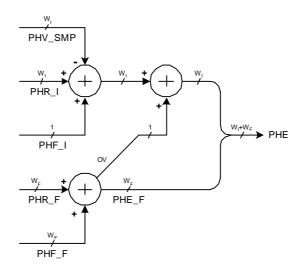

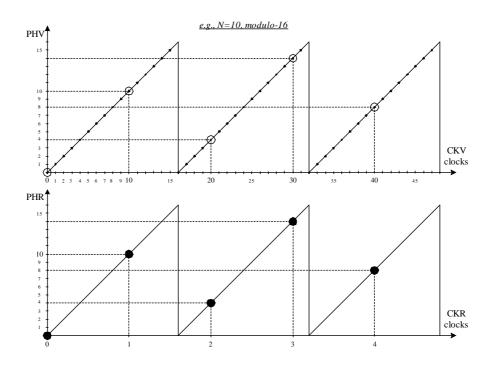

| 4.2  | Fractional-N division ratio timing example                                                                                                                                               | 12  |

| 4.3  | General block diagram of the phase detection                                                                                                                                             | 16  |

| 4.4  | Phase detector structure                                                                                                                                                                 | 17  |

| 4.5  | Modulo arithmetic of the reference and variable phase registers with zero phase alignment                                                                                                | 19  |

| 4.6  | Modulo arithmetic for phase offset $\phi_E$ of $3 \dots \dots \dots \dots \dots \dots \dots$                            | 121 |

|------|-------------------------------------------------------------------------------------------------------------------------|-----|

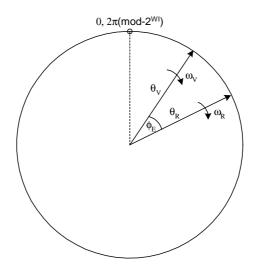

| 4.7  | Rotating vector interpretation of the reference and variable phases                                                     | 122 |

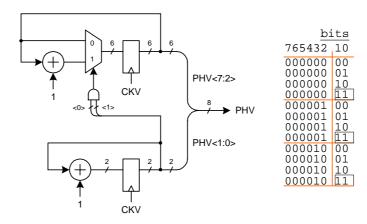

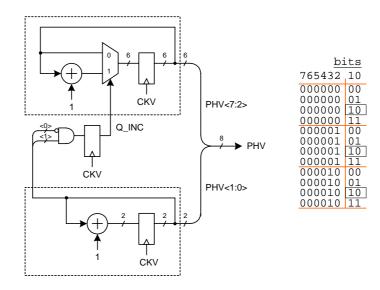

| 4.8  | Variable phase incrementer with separate calculation between lower and higher order bits                                | 123 |

| 4.9  | Implementation of the variable phase incrementer with higher order incre-<br>ment retiming                              | 124 |

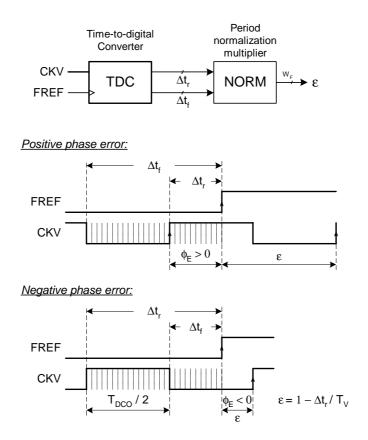

| 4.10 | Fractional (sub- $T_V$ ) phase error estimation                                                                         | 125 |

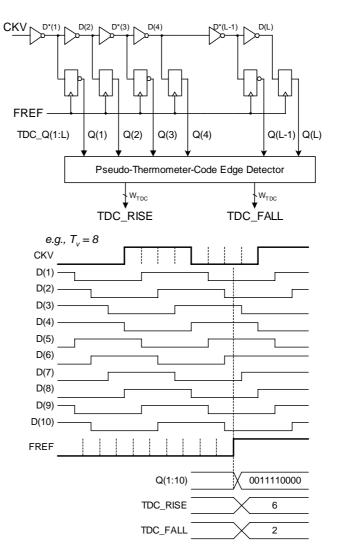

| 4.11 | Time-to-digital Converter (TDC)                                                                                         | 126 |

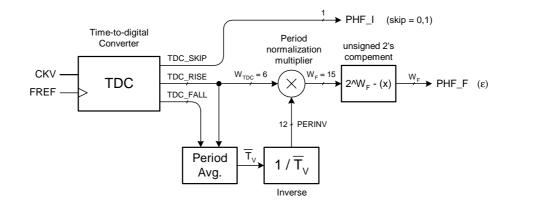

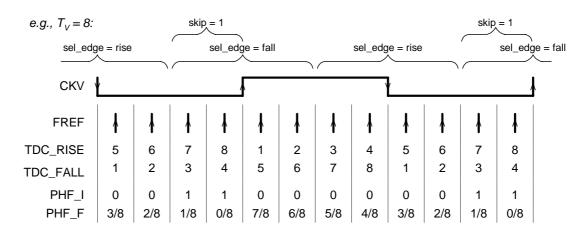

| 4.12 | TDC normalization and edge-skipping operation                                                                           | 129 |

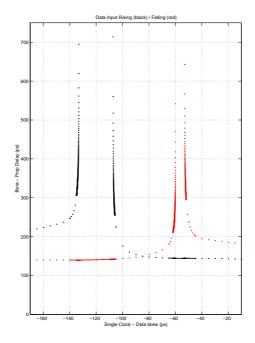

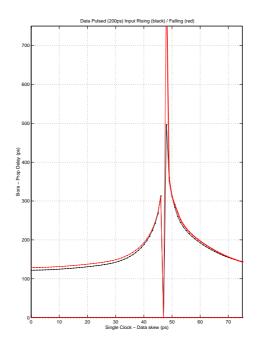

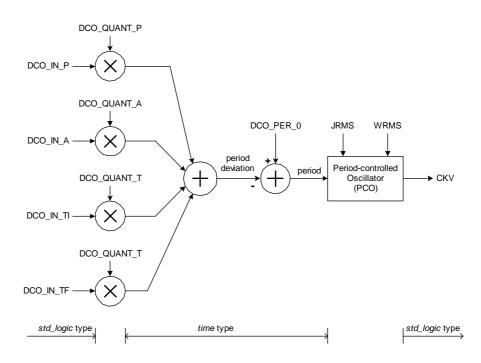

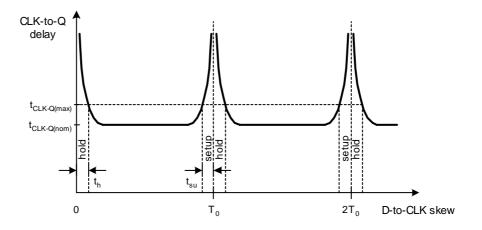

| 4.13 | CLK-to-Q delay as a function of data-clock timing skew relationship – high performance standard-cell flip-flop (DTN20P) | 132 |

| 4.14 | CLK-to-Q delay as a function of data-clock timing skew relationship – tactical flip-flop ("Bora")                       | 133 |

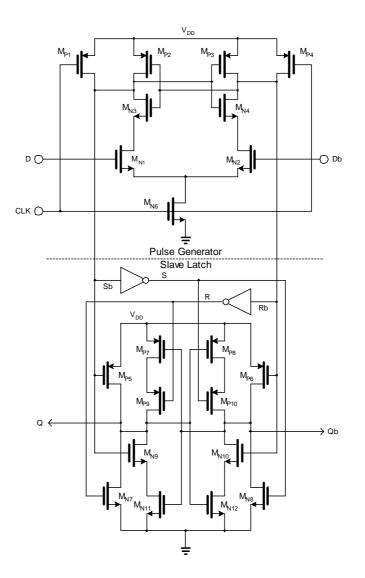

| 4.15 | Schematic of the tactical "Bora" flip-flop                                                                              | 135 |

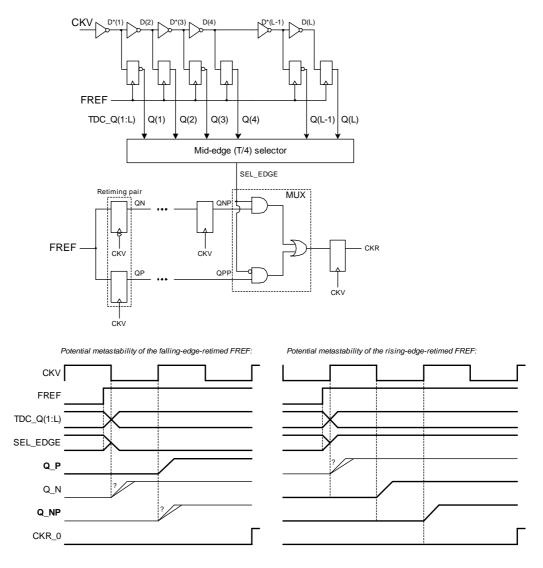

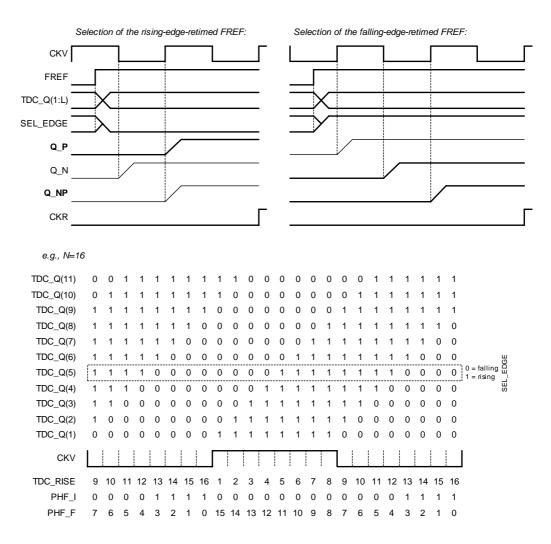

| 4.16 | FREF retiming by the DCO clock                                                                                          | 139 |

| 4.17 | DCO clock retiming details                                                                                              | 142 |

| 4.18 | TDC quantized transfer function                                                                                         | 143 |

| 4.19 | Calculating closed-loop gain of the ADPLL (assuming $K_{DCO} = \widehat{K}_{DCO}$ )                                     | 145 |

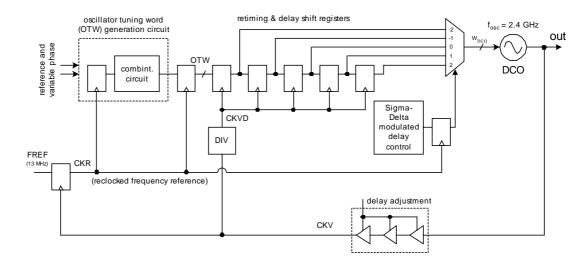

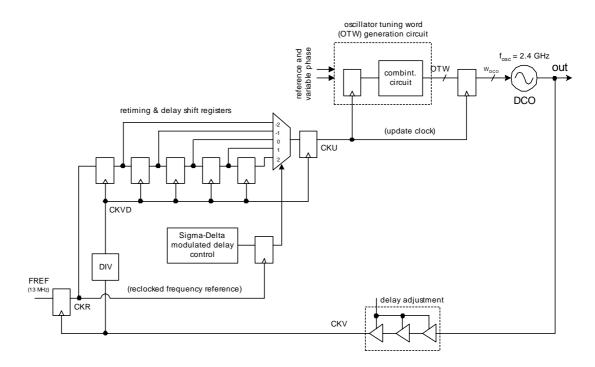

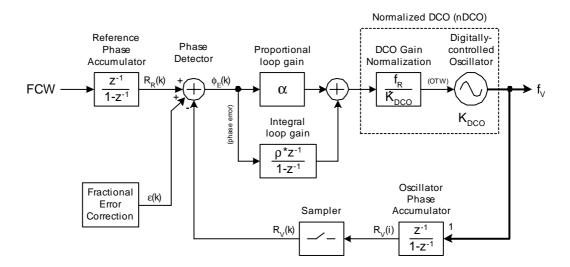

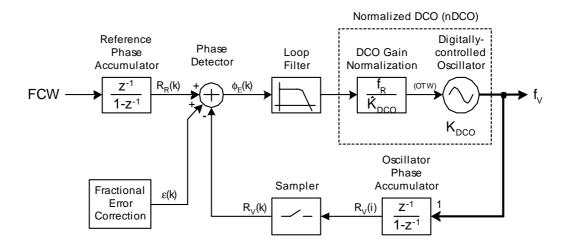

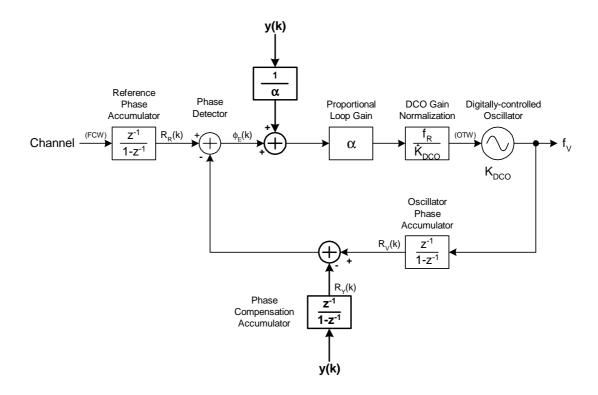

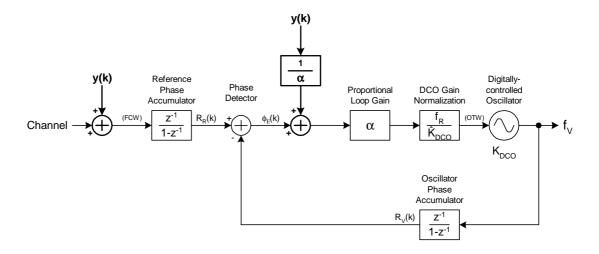

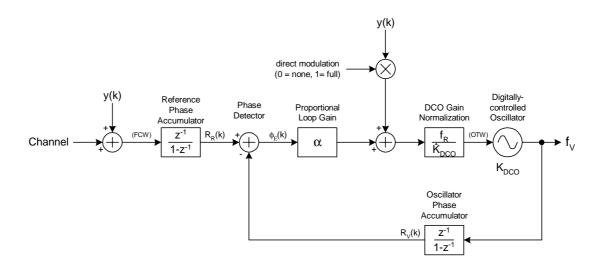

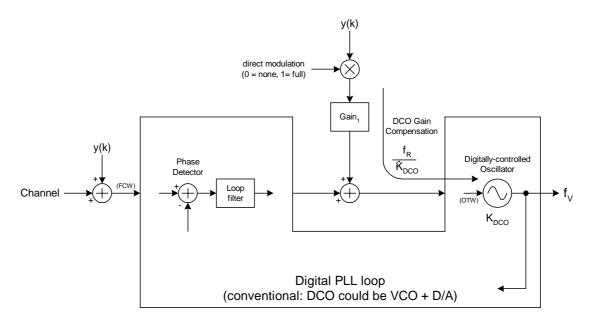

| 4.20 | Phase-domain all-digital synchronous PLL synthesizer                                                                    | 148 |

| 4.21 | Phase-domain all-digital synchronous PLL synthesizer (a different perspec-<br>tive)                                     | 150 |

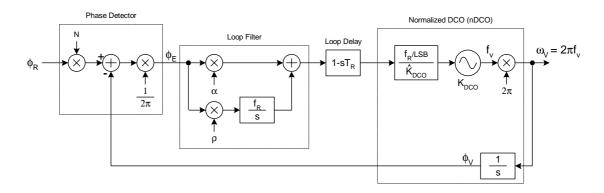

| 4.22 | Linearized equivalent s-domain model of the ADPLL                                                                       | 152 |

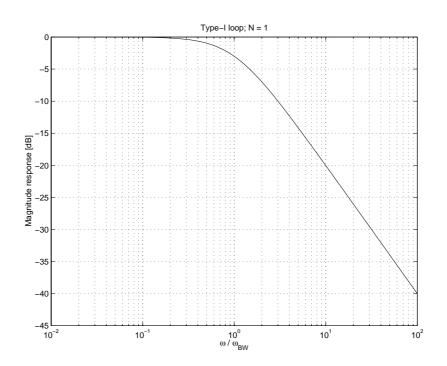

| 4.23 | Magnitude response of the type-I PLL loop for normalized frequencies                                                    | 154 |

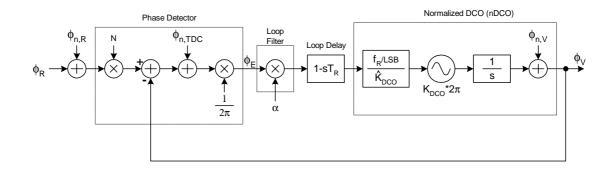

| 4.24 | Linear s-domain model with noise sources added                                                                          | 156 |

| 4.25 | Type-II phase-domain all-digital synchronous PLL synthesizer                                                            | 157 |

| 4.26 | Linearized equivalent s-domain model of the type-II ADPLL                                                               | 159 |

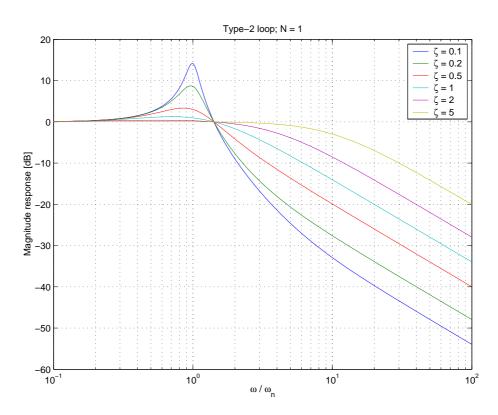

| 4.27 | Magnitude response of the type-II PLL loop for normalized frequencies<br>and for various values of $\zeta$              | 160 |

| 4.28 | Higher-order phase-domain all-digital synchronous PLL synthesizer                                                       | 161 |

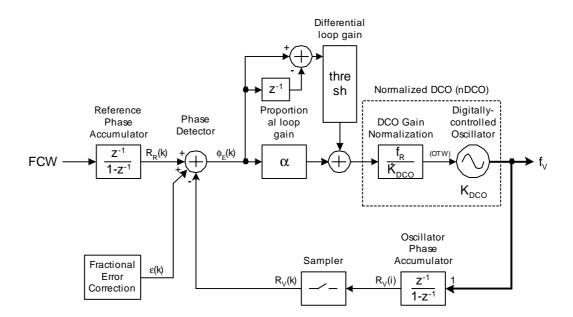

|      | Phase-domain ADPLL synthesizer with non-linear differential term                                                        |     |

| 4.30 | Gear-shifting mechanism of type-I PLL loop                                                                              | 168 |

| 4.31 | Gear-shifting mechanism of higher-order PLL loops                                                                       | 168 |

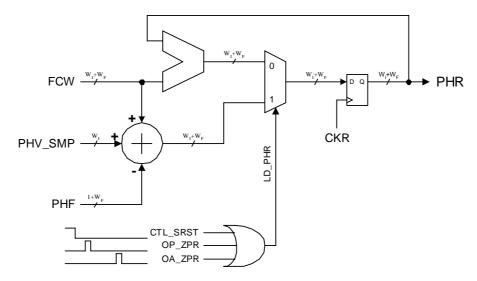

| 4.32 | Reference phase accumulator (PR) with zero-phase restart                                                                                                                                      | 2 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 4.33 | Simulation plots demonstrating the zero phase restart                                                                                                                                         | 4 |

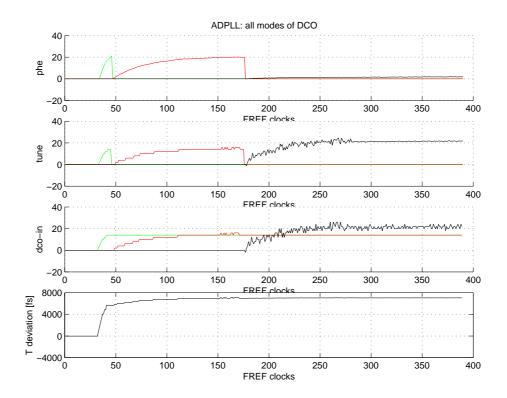

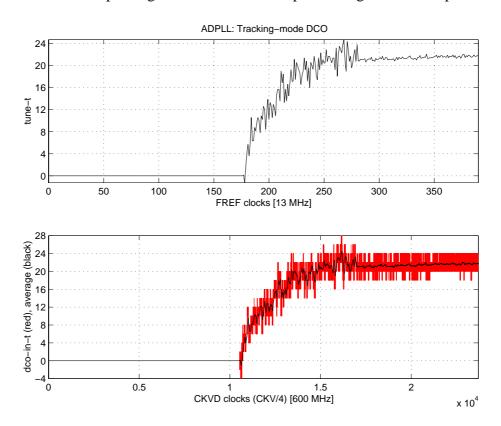

| 4.34 | Simulation plots demonstrating correctness the gear-shifting                                                                                                                                  | 6 |

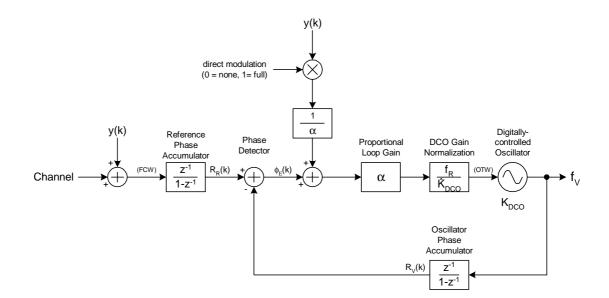

| 5.1  | Direct oscillator modulation with a straightforward PLL loop compensation scheme                                                                                                              | 2 |

| 5.2  | Direct oscillator modulation with an improved PLL loop compensation scheme                                                                                                                    | 3 |

| 5.3  | Partially-direct oscillator modulation with a PLL loop compensation scheme 18                                                                                                                 | 4 |

| 5.4  | An improved structure without the $1/\alpha$ operation $\ldots \ldots \ldots$ | 5 |

| 5.5  | Oscillator modulation scheme with a PLL loop compensation within a gen-<br>eral digital PLL architecture                                                                                      | 6 |

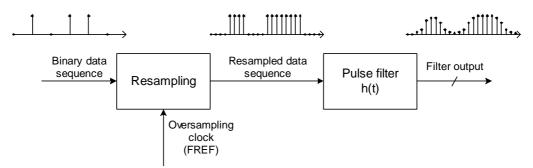

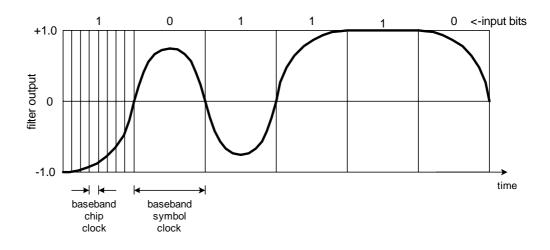

| 5.6  | Operation principle of the digital transmit filter                                                                                                                                            | 7 |

| 5.7  | Output waveform of a transmit filter                                                                                                                                                          | 8 |

| 5.8  | Top-level structure of the transmit filter                                                                                                                                                    | 9 |

| 5.9  | Curves for various state transitions based on previous symbol values 19                                                                                                                       | 0 |

| 5.10 | Trellis a GFSK transmit filter                                                                                                                                                                | 2 |

| 5.11 | DCO gain estimate by measuring tuning word change in response to a fixed frequency jump                                                                                                       | 4 |

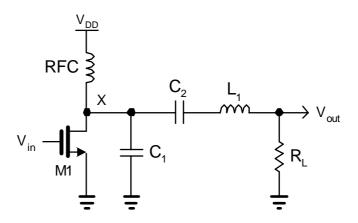

| 5.12 | Class-E power amplifier                                                                                                                                                                       | 5 |

| 5.13 | Waveforms of the class-E PA                                                                                                                                                                   | 7 |

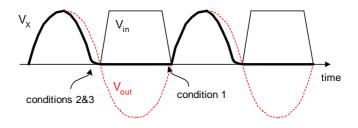

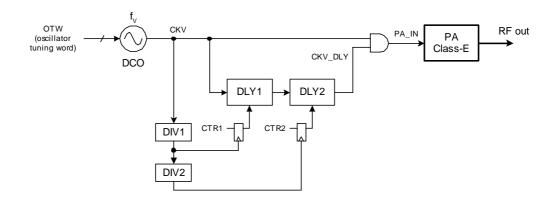

| 5.14 | Output power control through duty cycle of the class-E PA input 19                                                                                                                            | 9 |

| 5.15 | Digital amplitude control through pulse-width modulation                                                                                                                                      | 0 |

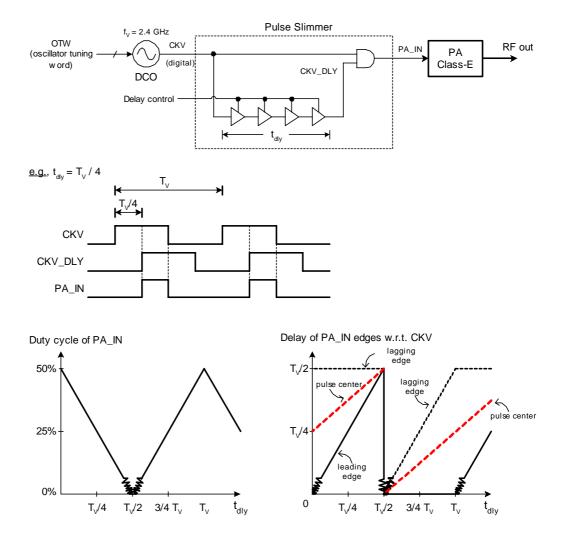

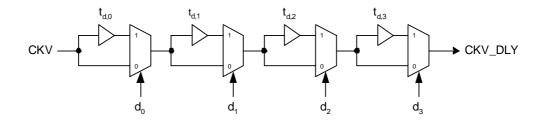

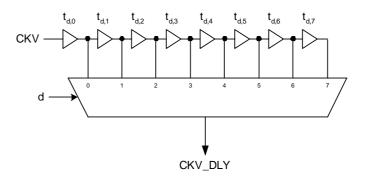

| 5.16 | Discrete delay control of the delay path                                                                                                                                                      | 2 |

| 5.17 | Discrete delay control of the delay path with a larger mux                                                                                                                                    | 3 |

| 5.18 | Discrete delay of PWM with additional high-speed dithering                                                                                                                                    | 4 |

| 5.19 | PAM modulation through tuning word adjustment                                                                                                                                                 | 5 |

| 6.1  | ADPLL-based "X1743" transmitter core                                                                                                                                                          | 9 |

| 6.2  | Micrograph of the X1743 testchip                                                                                                                                                              | 3 |

| 6.3  | Micrograph of the RF transmitter area                                                                                                                                                         | 4 |

| 6.4  | Photograph of the evaluation board                                                                                                                                                            | 5 |

| 6.5  | Evaluation board schematic                                                                                                                                                                                | . 216 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

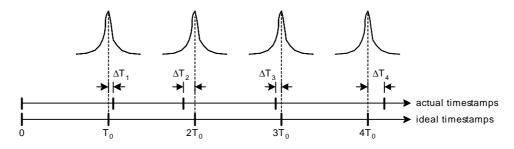

| 7.1  | Development of a non-accumulative timing deviation                                                                                                                                                        | . 220 |

| 7.2  | Development of an accumulative timing deviation                                                                                                                                                           | . 221 |

| 7.3  | DCO time-domain model in VHDL                                                                                                                                                                             | . 223 |

| 7.4  | Timing diagram of a flip-flop                                                                                                                                                                             | . 226 |

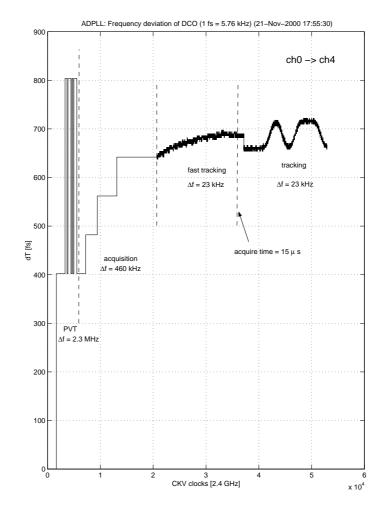

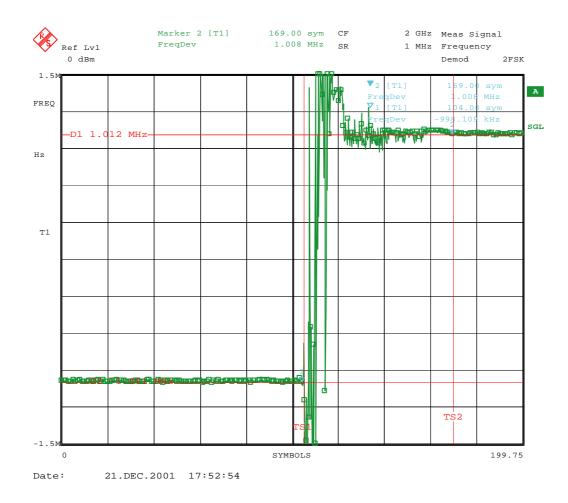

| 7.5  | Simulation plot of the transmit modulation at @2.4 GHz RF output; x-axis:<br>$\Delta f$ in femptosecond time units (1 fs = 5.75 kHz); y-axis: time in 417 ps RF clock periods                             | . 230 |

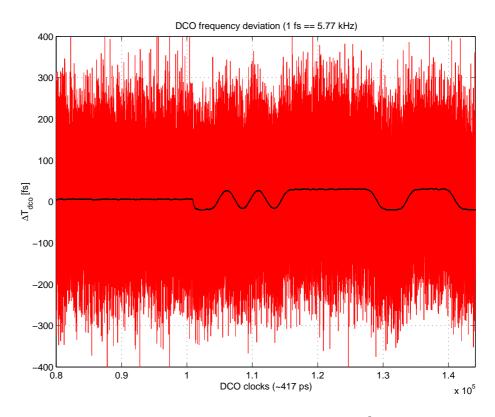

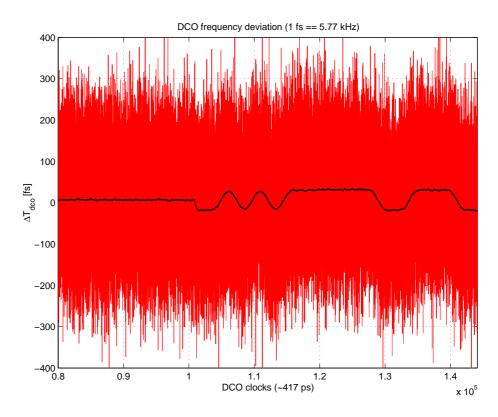

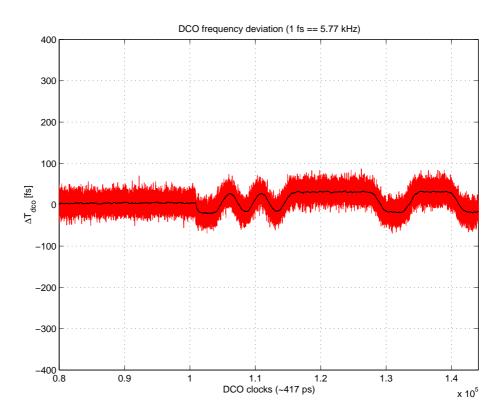

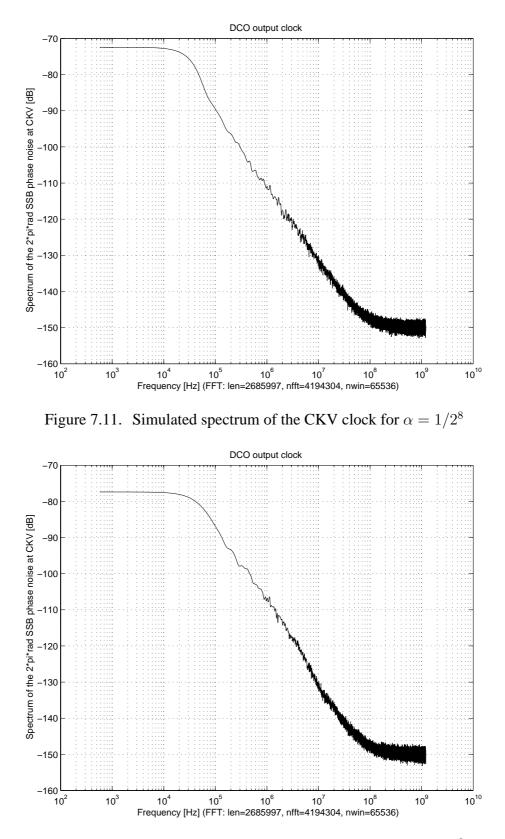

| 7.6  | Instantaneous period deviation of CKV for $\alpha = 1/2^8$ with only the phase noise floor of -150 dBc; black thick line is a "leaky" integration                                                         | . 233 |

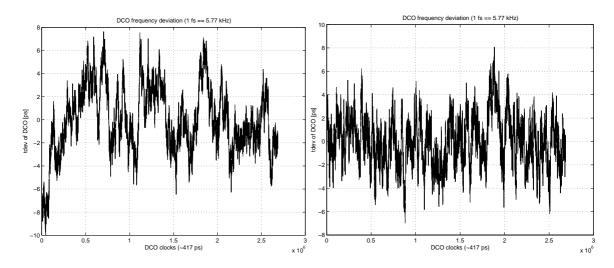

| 7.7  | Instantaneous period deviation of CKV for $\alpha = 1/2^8$ with the phase noise<br>floor of -150 dBc and $1/f^2$ noise of -105 dBc at 500 kHz; black thick line<br>is a "leaky" integration               | . 234 |

| 7.8  | Instantaneous period deviation of CKV for $\alpha = 1/2^8$ with only the $1/f^2$ noise of -105 dBc at 500 kHz; black thick line is a "leaky" integration                                                  | . 235 |

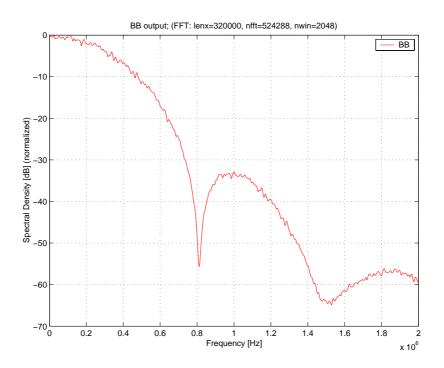

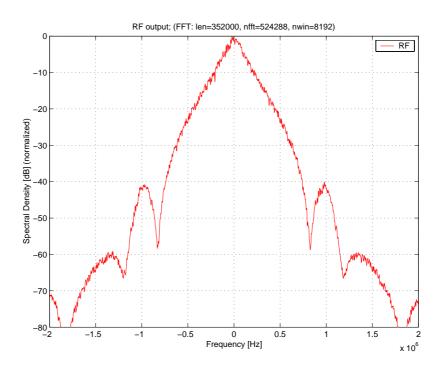

| 7.9  | Power spectrum of the GFSK filter output                                                                                                                                                                  | . 236 |

| 7.10 | Output power spectrum of GFSK-modulated RF carrier; center is at the carrier frequency                                                                                                                    | . 237 |

| 7.11 | Simulated spectrum of the CKV clock for $\alpha = 1/2^8$                                                                                                                                                  | . 238 |

| 7.12 | Simulated spectrum of the CKV clock for $\alpha = 1/2^6$                                                                                                                                                  | . 238 |

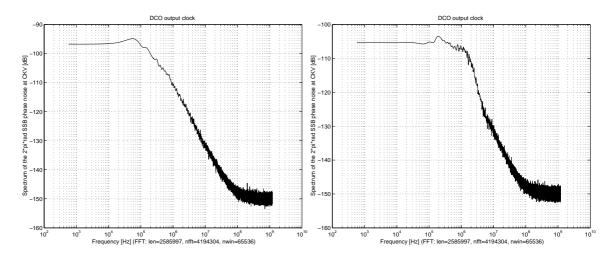

| 7.13 | Simulation plot of TDEV for $\alpha = 1/2^8$ (left) and $\alpha = 1/2^6$ (right)                                                                                                                          | . 239 |

| 7.14 | Simulated spectrum of the CKV clock for $\alpha = 1/2^8$ and $\alpha = 1/2^6$ (right) when FREF noise is turned off $\ldots \ldots \ldots$ | . 239 |

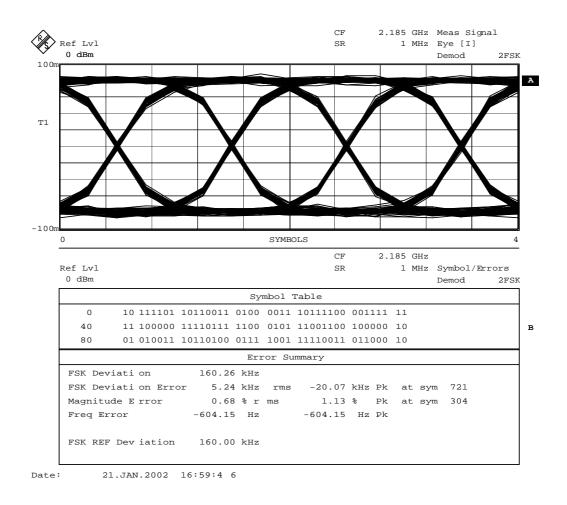

| 8.1  | Eye diagram of a PN9 pseudo-random data at 2185 MHz, BW=4 kHz and room temperature with the measured statistics                                                                                           | . 241 |

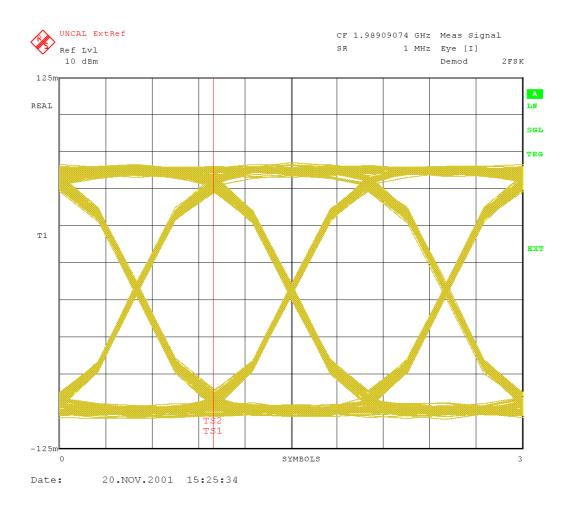

| 8.2  | Eye diagram of a pseudo-random data. Measured peak zero crossing error is $\pm 2.6\%$ or 4.8 deg; RMS phase error is 2.06 deg.                                                                            | . 242 |

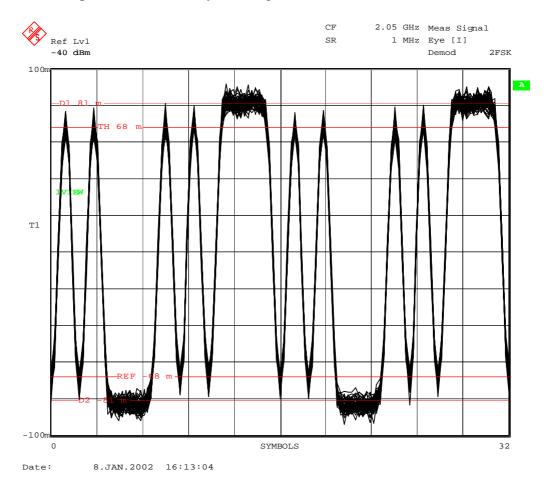

| 8.3  | Demodulated diagram of the 111101010000 repetitive pattern. The ratio of $f_{2,avg}$ and $f_{1,avg} = 84\% \ge 80\%$ .                                                                                    | . 243 |

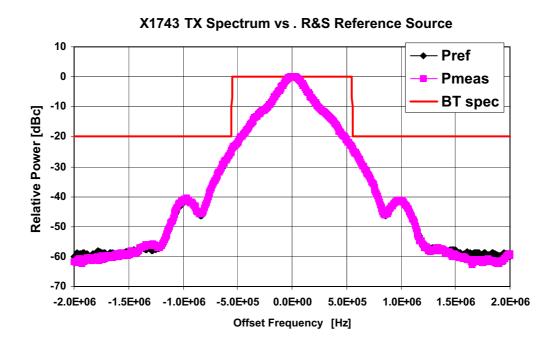

| 8.4  | Measured output power spectrum of GFSK modulated pseudo-random data with a 1950.0 MHz carrier frequency                                                                                                   | . 244 |

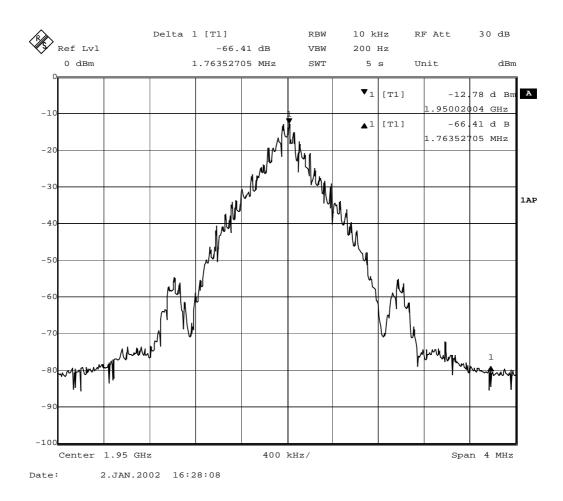

| 8.5  | Measured GFSK spectrum superimposed on the Rohde&Schwarz FSIQ-7 internal source reference and the BLUETOOTH spec                                                                                          | . 245 |

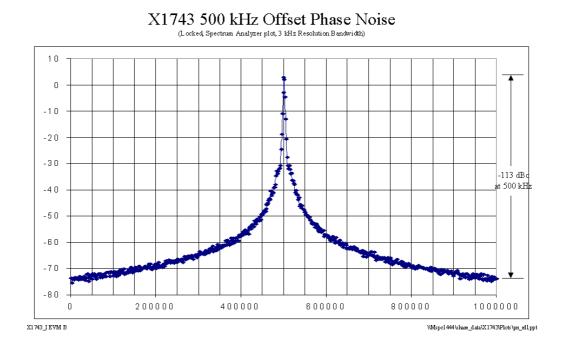

| 8.6  | Measured synthesizer output spectrum (wide), resolution bandwidth RBW=3 kHz; center at 500 kHz offset mark                |

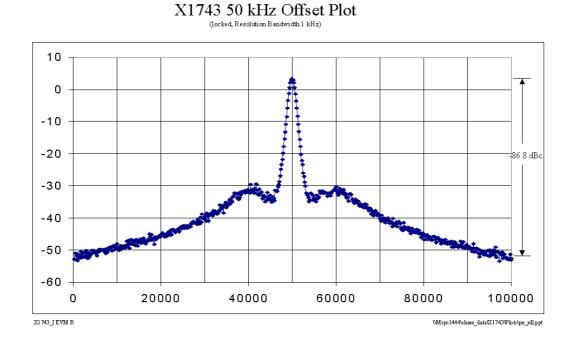

|------|---------------------------------------------------------------------------------------------------------------------------|

| 8.7  | Measured synthesizer output spectrum (close-in); resolution bandwidth RBW=1 kHz; center at 50 kHz offset mark             |

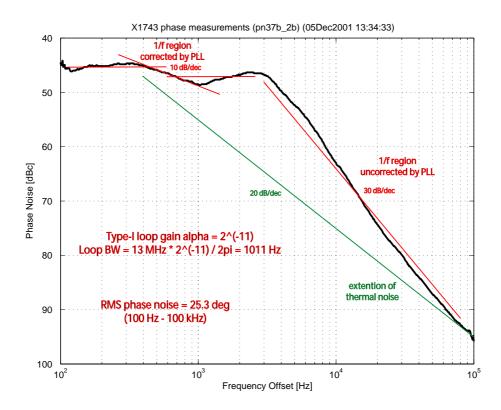

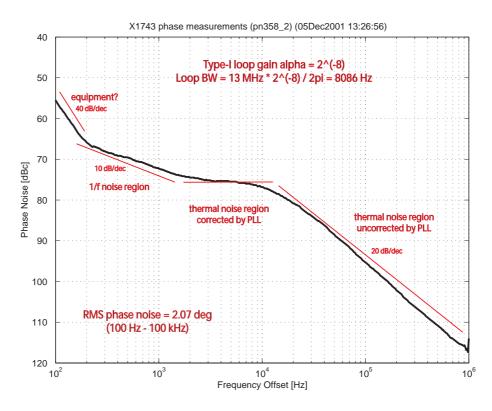

| 8.8  | Measured synthesizer phase noise: narrow bandwidth                                                                        |

| 8.9  | Measured synthesizer phase noise: wide bandwidth                                                                          |

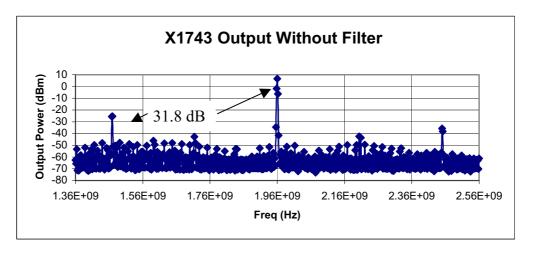

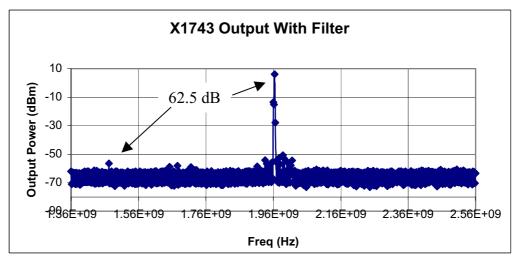

| 8.10 | Measured spurious tone level at the RF output without (top) and with a standard 2-pole antenna filter (bottom)            |

| 8.11 | Observed settling time of the ADPLL                                                                                       |

| 8.12 | Open-loop frequency transfer of the oscillator                                                                            |

| 8.13 | Measured output power spectrum of the DSP-driven GSM modulation, but with loop attenuation of higher-frequency components |

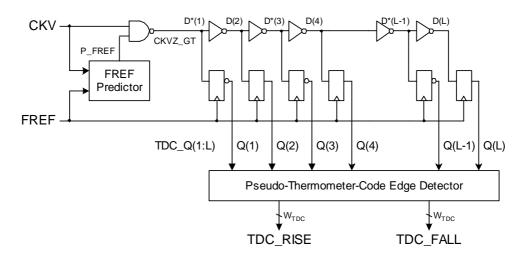

| 9.1  | Time-to-digital Converter (TDC) with FREF prediction                                                                      |

# LIST OF TABLES

| 1.1 | C035 process technology parameters                                                                                                                   |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1 | Timing deviation vs. frequency deviation at different points in a BLUE-<br>TOOTH band                                                                |

| 2.2 | Frequency resolution and corresponding DCO period deviation for the DCO modes at the middle of the BLUETOOTH band, $f_0 = 2440 \text{ MHz} \dots 72$ |

| 4.1 | ADPLL clock names                                                                                                                                    |

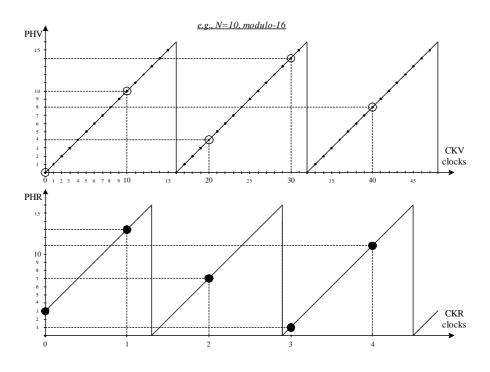

| 4.2 | Phase detection signal names cross-reference                                                                                                         |

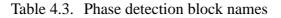

| 4.3 | Phase detection block names                                                                                                                          |

| 4.4 | TDC signal names cross-reference                                                                                                                     |

| 4.5 | DCO frequency quantization                                                                                                                           |

| 5.1 | Transmit filter output curves                                                                                                                        |

| 6.1 | Top-level transmitter core building blocks                                                                                                           |

| 6.2 | Key C035 process technology parameters                                                                                                               |

| 7.1 | VHDL modeling abstraction levels                                                                                                                     |

| 8.1 | Measured key transmitter performance                                                                                                                 |

| 8.2 | Current consumption at 1.55 V supply                                                                                                                 |

#### CHAPTER 1

## INTRODUCTION

## 1.1 Motivation

With the explosive growth of the wireless communication industry, research related to communication circuits and architectures has received great attention. The major issues being addressed are low-cost, low-voltage and low-power designs, which achieve necessary performance while being able to be economically manufactured in high volumes. Recently, there has been an additional emphasis on *integration* of heterogeneous parts that constitute a communication device.

## 1.1.1 CMOS vs. Traditional RF Process Technologies

The *radio frequency* (RF) front-end circuits have been traditionally implemented by Gallium Arsenide (GaAs) MESFET, Si-bipolar junction transistors (BJTs), III-V heterojunction bipolar junction transistors (HBTs) and Silicon-Germanium (SiGe) HBTs, while the baseband *digital signal processing* (DSP) and analog circuits are being implemented exclusively using CMOS technologies. As the emphasis of wireless applications moves towards the *personal communication systems* (PCS) and *wireless local area networks* (WLAN) as well as the wireless entertainment electronics, light-weight, small-dimension, low-cost, low-power and a higher level of integration are becoming ever critical. These have spurred the interests in low cost CMOS technologies. RF wireless systems using CMOS technologies are being intensively investigated mainly due to their low cost, high yield and higher level of integration including baseband circuits.

On the device physics side, there is a fundamental limitation of the bipolar technology that prevents from using it in low-voltage applications in favor of CMOS. Operation at 1 V power supply is difficult to achieve since the *base-emitter voltage*  $V_{BE}$  of bipolar transistors lies around 0.7 V and the base-to-collector junction must be reverse biased. By contrast, the MOS transistor can admit a *drain-source voltage*  $V_{DS}$  lower than the *gatesource voltage*  $V_{GS}$ , which in turn can be reduced by lowering threshold voltage of the MOS device. Therefore, if the saturation voltage is kept at a few hundred mV, there is enough room for some output dynamic range.

#### 1.1.2 Deep-Submicron CMOS

As the feature size of the digital logic CMOS technology becomes smaller, the frequency at which CMOS transistors can operate while delivering acceptable performance becomes higher [1] [2] [3] [4].

In terms of CMOS transistor application for RF circuits, there are several *figure-of-merit* (FOM) parameters: cutoff frequency  $f_T$ , maximum oscillation frequency  $f_{max}$ , minimum noise figure  $F_{min}$ , flicker noise (1/f), power-added efficiency PAE and power gain  $G_A$ . A conventional deep-submicron CMOS technology designed for logic applications has shown to exhibit useful RF device characteristics [3].

Scaling of CMOS devices increases the 1/f flicker noise, which is caused by carrier

trapping near the thin oxide-silicon interface. On the other hand, there is no such junction in bipolar transistors. The flicker noise could be converted into close-in phase noise of *voltage-controlled oscillators* (VCO) and appear at the output of down-conversion mixers. Fortunately, as shown in [1], this noise frequency translation mechanism can be avoided through half-circuit topological symmetry.

Both  $f_T$  and  $f_{min}$  peak values already exceed 100 GHz for sub-0.1  $\mu$ m deep-submicron CMOS logic devices and are predicted to double every three years [1]. Despite the continual RF performance lag behind the latest SiGe bipolar processes, at this point, their performance is adequate for wireless communication bands for up to 5 GHz.

This has opened the possibility for CMOS RF circuits that meet the stringent requirements of communication systems. Efforts have been made to show the feasibility of CMOS front-end circuits [5] [6] [7], and the performance has become comparable to those of BJT circuits. The ultimate goal is to take advantage of the CMOS process to implement a *single chip* radio by integrating the RF front-end, *intermediate frequency* (IF) modulation/demodulation circuits and analog baseband signal processing circuits with the digital baseband section.

In this research work, a fundamental property of the digital deep-submicron process is utilized as a *new paradigm*:

In a deep-submicron CMOS process, time-domain resolution of a digital signal edge transition is superior to voltage resolution of an analog signal.

This is in a clear contrast with the older process technologies, which rely on a large supply voltage (originally 15 V, then 5 V, and finally 3.3 V and 2.5 V) and a stand-alone configura-

tion with few extraneous noise sources in order to achieve a good signal-to-noise ratio and resolution in the voltage domain, often at a cost of long settling time. In a deep-submicron process with its low supply voltage (at and below 1.5 V), relatively high threshold volt-age (0.6 V and often higher due to the body effect) the available voltage headroom is quite small. Moreover, massive switching noise of a large digital circuitry around makes it harder to resolve signals in the voltage domain. At the same time, the switching characteristic of a MOS transistor are excellent with rise and fall times on the order of tens of picoseconds.

### 1.1.3 Digitally-Intensive Approach

| interconnection material   | copper                      |

|----------------------------|-----------------------------|

| minimum metal pitch        | 0.35 μm                     |

| transistor nominal voltage | 1.5 V                       |

| L drawn                    | 0.11 μm                     |

| L effective                | $0.08 \ \mu m$              |

| gate oxide                 | 29 A                        |

| substrate resistivity      | $\leq$ 50 $\Omega \cdot cm$ |

Table 1.1.

C035 process technology parameters

A great reduction of the transistor feature size in recently developed deep-submicron CMOS processes shifts the design paradigm towards more digitally-intensive techniques. In a monolithic implementation, the manufacturing cost of a design is measured not in terms of a number of devices used but rather in terms of the occupied silicon area, and is little dependent on the actual circuit complexity. The testing part of the overall cost does indeed depend on the circuit complexity, but a large number of digital gates typically have a higher test coverage and lower testing cost than even a small analog circuit.

Each new digital CMOS process advance occurs roughly 18 months while increasing

the digital gate density by a factor of two (known as the Moore's Law). A typical digital cellular phone on the market today contains over a million transistors. Analog and RF circuits, on the other hand, do not scale down very well. For example, the latest Texas Instruments' CMOS process (C035 [8] summarized in Table 1.1) with 0.08  $\mu$ m L-effective feature size achieves an astonishing digital gate density of 150K equivalent (2-input NAND) gates per mm<sup>2</sup>, which is an order of magnitude greater than with more traditional RF BiCMOS process technologies. An average-size inductor for an integrated LC oscillator occupies about 0.5 mm<sup>2</sup> of silicon area! A low-noise charge pump, or a low-distortion image-reject mixer, both good examples of classical RF transceiver components, occupy roughly about the same area, which could be traded for tens of thousands of digital gates, which is a lot of DSP power! Consequently, there are numerous incentives to look for digital solutions.

Migrating to the digitally-intensive RF front-end architecture could bring forth the following well-known advantages of a conventional digital design flow:

- Fast design turn-around cycle using automated CAD tools (VHDL or Verilog hardwarelevel description language, synthesis, auto-place and auto-route with timing-driven algorithms, parasitic backannotation and postlayout optimization).

- Much lower parameter variability than with analog circuits.

- Ease of testability.

- Lower silicon area and dissipated power that gets better with each CMOS technology advancement (also called a "process node").

- Excellent chances of first-time silicon success. Commercial analog circuits usually

require several design, layout and fabrication iterations to meet marketing requirements.

#### **1.1.4 System Integration**

There is a wide array of opportunities that integration presents. The most straightforward way would be to merge various digital sections into a single silicon die, such as DRAM or flash memory embedded into DSP or controller. More difficult would be integrating the analog baseband with the digital baseband. Care must be taken here to avoid coupling of digital noise into the high-precision analog section, usually through substrate or power/ground supply lines. In addition, the low amount of voltage headroom challenges one to find new circuit and architecture solutions. Integrating the analog baseband into RF transceiver section presents a different set of challenges: The conventional Bi-CMOS RF process is tuned for high-speed operation with a number of available passive components and does not fundamentally stress high precision.

Sensible integration of diverse sections results in a number of advantages:

- Lower total silicon area. In a deep-submicron CMOS design, the silicon area is often bond-pad limited. Consequently, it is beneficial to merge various functions onto a single silicon die to maximize the core to bond-pad ratio.

- Lower component count and thus lower packaging cost.

- Power reduction. There is no need to drive large external inter-chip connections.

- Lower printed-circuit board (PCB) area, thus saving the precious "real estate."

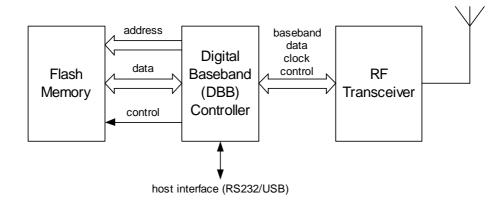

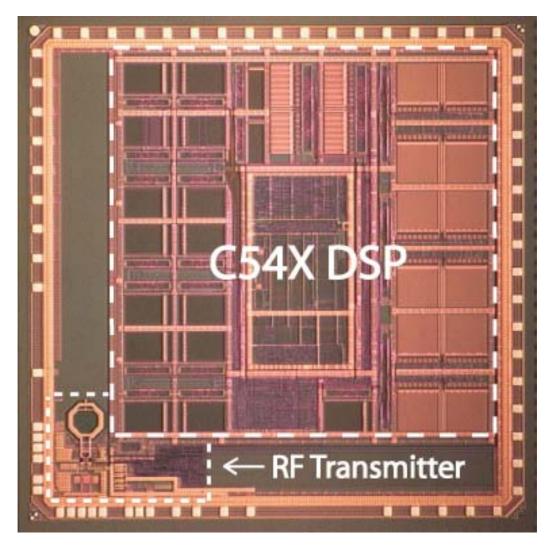

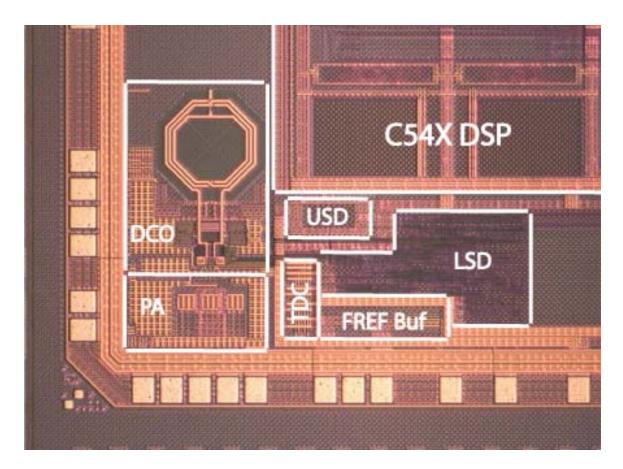

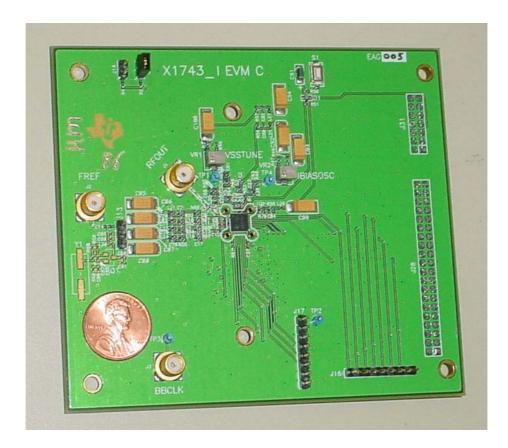

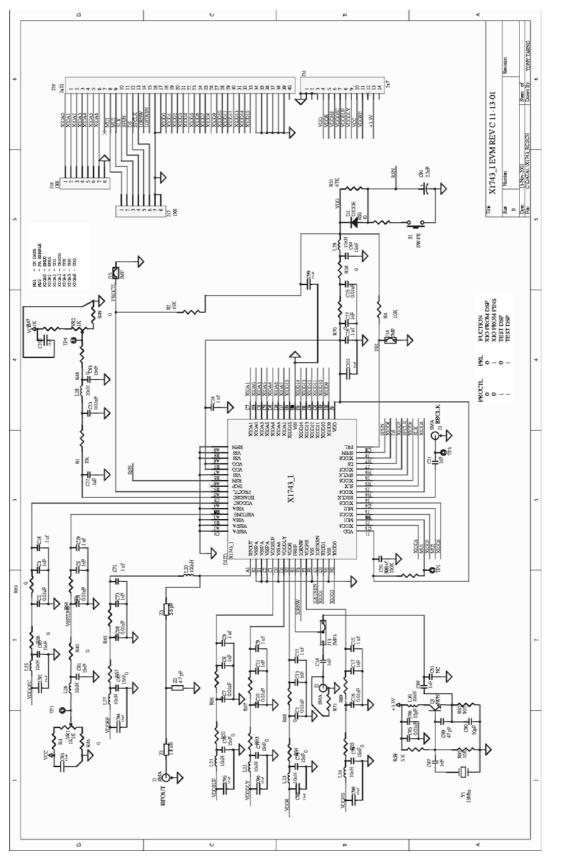

Figure 1.1. Example in ultimate mobile wireless integration: single-chip BLUETOOTH radio

The ultimate goal in mobile wireless integration is a single-chip digital radio as shown in Fig. 1.1. The *digital baseband controller* (DBB) is usually based on a *digital signal processor* (DSP) or the ARM7 microprocessor and is responsible for taking the digital data stream from the RF transceiver and performing any necessary digital signal processing on it to convert the digital data stream into a stream of user data. Examples of the processing performed by the DBB controller may include digital filtering, data encoding and decoding, error detection and correction. It also implements the GSM<sup>1</sup> cellular or BLUETOOTH [9] protocol layer stack which is controlled by a software program stored in a non-volatile flash memory. The RF transceiver module implements the physical layer by converting the information bits to/from the RF waveform. The advanced deep-submicron CMOS process total integration leads to an extremely compact and economic implementation of this sophisticated and highly functional communication system.

<sup>&</sup>lt;sup>1</sup>GSM originally stood for *Groupe spe'cial mobile* but later renamed to *Global System for Mobile communications* for marketing reasons

#### 1.1.5 System Integration Challenges for Deep-Submicron CMOS

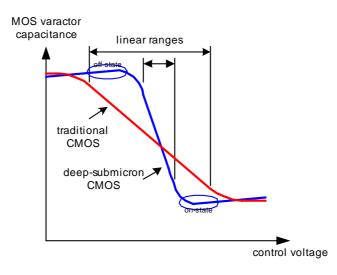

Deep-submicron CMOS processes present new integration opportunities on one hand, but make it extremely difficult to implement traditional analog circuits, on the other. For example, frequency tuning of a low-voltage deep-submicron CMOS oscillator is an extremely challenging task due to its highly nonlinear frequency vs. voltage characteristics and low voltage headroom making it susceptible to the power/ground supply and substrate noise. In such low supply voltage case, not only the dynamic range of the signal suffers but also the noise floor rises, thus causing even more severe degradation of the signal-to-noise ratio. At times, it is possible to find a specific solution, such as utilizing a voltage doubler [10]. Unfortunately, with each CMOS feature size reduction, the supply voltage needs also to be scaled down, which is inevitable in order to avoid breakdown and reliability issues [11].

Moreover, the high degree of integration leads to generation of substantial *digital switching noise* that is coupled through power supply network and substrate into noise sensitive analog circuits [12]. Furthermore, the advanced CMOS processes typically use low resistance P-substrate which is an effective means in combating latchup problems, but exacerbates substrate noise coupling into the analog circuits. This problem only gets worse with scaling down of the supply voltage. Fortunately, there is a serious effort today among major IC fabrication houses to develop CMOS processes with higher resistivity silicon substrates.

Circuits designed to ensure the proper operation of RF amplifiers, filters, mixers, and oscillators depend on circuit techniques that operate best with long-channel, thick-oxide devices with supply voltage of 2.5 V or higher. The process utilized for this work is optimized for short-channel, thin-oxide devices operating as digital switches at only 1.5 V.

In order to address the various deep-submicron RF integration issues, some new and radical system and architectural changes have to be discovered. In this research, alternative approach and architectures for RF front-end are explored. This will allow easy integration of RF section into digital baseband.

# 1.2 Frequency Synthesizer as an Integral Part of an RF Transceiver

RF synthesizers, specifically, remain one of the most challenging tasks in mobile RF systems because they must meet very stringent requirements of a low-cost, low-power and low-voltage monolithic implementation while meeting the phase noise and switching transient specifications. They are being selected and ranked according to the following set of criteria:

- Phase noise performance as any analog circuits, oscillators are susceptible to noise, which causes adverse affects in the system performance during receive and transmit.

- Discrete spurious noise performance unwanted frequency components to appear in the oscillator output spectrum.

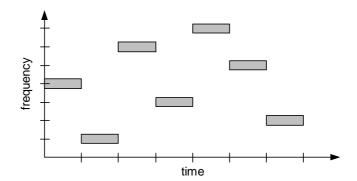

- Switching speed very important in modern communications systems which utilize channel and frequency hopping (see Fig. 1.2) in order to combat various wireless channel impairments (fading, interference, etc.). Since the system switches carrier frequency often (as fast as once every 1.6 ms in BLUETOOTH), a fast switching and stable frequency synthesizer is essential for proper operation. Switching speed is also important in a fixed-channel *time-division multiple access* (TDMA) systems for quick handoff.

- Frequency and tuning bandwidth the frequency range has to cover the operational band and have enough margin for process-voltage-temperature variations.

- Power consumption important for battery operated mobile communication units.

- Size important for mass production deployment.

- Integrateability utilizing the deep-submicron CMOS process technology in order to integrate with digital baseband.

- Cost no extra cost added to the process. Requires minimal amount of external components (so called "bill of materials").

- Portability ability to transfer the design from one application to another and from one process technology node to the next. An important issue in digital VLSI and for *intellectual property* (IP)-based applications. Designs described in a hardware description language (HDL) are very portable.

Figure 1.2. Channel hopping of a transmitted signal

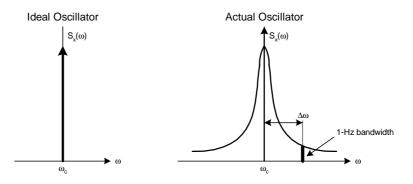

Figure 1.3. Output spectrum of ideal and actual oscillators

#### **1.2.1** Noise in Oscillators

Phase noise is normally characterized in the frequency domain [13] [14]. For an ideal oscillator operating at frequency  $\omega_c$ , the voltage output can be expressed as  $x(t) = A \cdot \cos(\omega_c t + \phi)$ , where A is an amplitude and  $\phi$  is an arbitrary, but fixed, phase reference. The power is concentrated at a single frequency  $\omega_c$ . Consequently, its spectrum  $S_x(\omega) = \frac{A^2}{2}\delta(\omega - \omega_c)$  is the shape of a Dirac impulse as depicted in Fig. 1.3. In a practical oscillator, however, both the amplitude and the phase are time-varying fluctuations and the spectrum will exhibit "skirts" around the carrier frequency and spread into nearby frequencies. In most cases, the disturbance in the amplitude is negligible or unimportant, since it could easily be removed by a limiter circuit, and, therefore, only a random deviation of the phase is considered:

$$x(t) = A\cos(\omega_c t + \phi(t)) \tag{1.1}$$

where  $\phi(t)$  is a small random excess phase representing variations in the period and is commonly called "phase noise." For a small value of the phase noise fluctuation  $|\phi(t)| \ll 1$ rad, Eq. 1.1 could be simplified to

$$x(t) \approx A \cos \omega_c t - A\phi(t) \sin \omega_c t \tag{1.2}$$

which means that the spectrum of  $\phi(t)$  is frequency-translated to  $\pm \omega_c$ .

To quantify this phase noise, we consider a 1-Hz unit bandwidth at an offset of  $\Delta \omega$  from the carrier, calculate the noise power in the band, and divide this result by the carrier power [14]. This is the single-sided spectral noise density in units of deciBell carrier per Hertz [dBc/Hz]. By convention, "c" in "dBc" means with "respect to carrier."

$$\mathcal{L}\{\Delta\omega\} = 10 \cdot \log\left(\frac{\text{noise power in a 1-Hz bandwidth at frequency }\omega_c + \Delta\omega}{\text{carrier power}}\right) \quad (1.3)$$

The single-sided phase noise of Eq. 1.3 is simply one-half of the phase noise spectrum, which contains both positive and negative frequency components:

$$\mathcal{L}\{\Delta\omega\} = \frac{S_{\phi}(\Delta\omega)}{2} \tag{1.4}$$

Figure 1.4. Phase noise spectrum of an actual oscillator

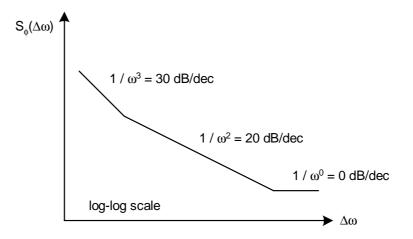

Fig. 1.4 shows a typical oscillator phase noise spectrum. In this log-log plot, phase noise normalized to dBc/Hz is plotted against the offset frequency  $\Delta \omega$  from the carrier  $\omega_c$ . The phase noise profile follows the curve shown, where it traverses through  $1/\omega^3$ ,  $1/\omega^2$  and

$1/\omega^0$  slope regions. The region  $1/\omega^2$  is generally referred to as the thermal noise region, since it is caused by white or uncorrelated timing fluctuations in the period of oscillation. The 1/f flicker noise of electronic devices is also substantial for lower offset frequencies. It gets upconverted to the  $1/\omega^3$  region. Finally, the  $1/\omega^0$  region is the thermal electronic noise added to the clock outside of the oscillator, such as in an output buffer, and which does not affect the oscillator time base.

Let us consider the effect of a single sinusoidal tone in the phase,  $\phi(t) = \phi_p \cdot \sin(\omega_m t)$ . Eq. 1.1 now becomes

$$x(t) \approx A \cos \omega_c t + A \frac{\phi_p}{2} \left[ \cos(\omega_c + \omega_m) t - \cos(\omega_c - \omega_m) t \right]$$

(1.5)

Therefore the oscillator output voltage *power spectral density* (PSD) is directly related to the phase noise PSD. Using single-sided spectral densities, we have

$$S_{\phi}(\omega) = \frac{\phi_p^2}{2} \cdot \delta(\omega - \omega_m) \tag{1.6}$$

$$S_x(\omega) = \frac{A^2}{2} \left[ \delta(\omega - \omega_c) + \frac{1}{2} S_\phi(\omega - \omega_c) + \frac{1}{2} S_\phi(\omega_c - \omega) \right]$$

(1.7)

Eq. 1.7 shows that the phase noise is directly shifted in frequency towards the carrier and put on the left and right side of the synthesized frequency. It is graphically depicted in Fig. 1.5.

Fig. 1.5 also demonstrates an *undesired* systematic fluctuation in the oscillator phase noise giving rise to a spurious tone. Spurious tones are normally caused by the phase/frequency

Figure 1.5. Equivalence between PSD and single-sided phase noise

detector and divider circuits in the classical PLL-based synthesizers. In the time domain, the presence of systematic timing fluctuations in an oscillator waveform represents a periodic timing error. In the frequency domain, it manifests as undesired tones in the frequency spectrum. Ideally, an oscillator output spectrum centers at a single frequency with no spurious tones. In reality, the presence of spurious tones causes other frequency components to appear in the oscillator output spectrum. Spurious tones are measured in dBc (or dB referenced to the carrier) at a specific frequency location in the spectrum. It is simply the power difference between the carrier and the spurious tone signals in dB.

At times, it is necessary to relate the PSD of the instantaneous frequency deviation  $\Delta\omega(t)$  to the phase noise PSD  $S_{\phi}(\omega)$  and to the single-sided phase noise  $\mathcal{L}\{\omega\}$ . Since frequency is the derivative of phase, we get

$$S_{\Delta\omega}(\omega) = \omega^2 S_{\phi}(\omega) = 2\omega^2 \mathcal{L}\{\omega_m\}$$

(1.8)

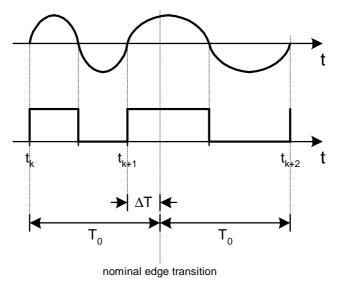

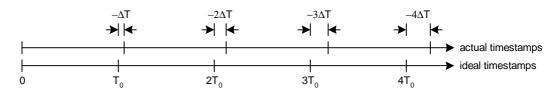

The oscillator perturbations seen in the frequency domain have the underlying cause in the time domain, where the exact time of one period of oscillation will differ from the other. The period has an average value  $T_0$  and a timing error  $\Delta T$ . The timing error variance  $\sigma_{\Delta T} = \sqrt{\Delta T^2}$  is called jitter. A first-order formula is given in [15] that relates jitter to phase noise

$$\mathcal{L}\{\Delta\omega\} = \frac{2\pi \cdot \omega_c}{\Delta\omega^2} \cdot \left(\frac{\sigma_{\Delta T}}{T_0}\right)^2 \tag{1.9}$$

The region modeled by Eq. 1.9 is the  $1/\omega^2$  upconverted thermal noise, which is the dominant noise mechanism in oscillators.

#### 1.2.2 Transmitter

Figure 1.6. Conventional direct up-conversion transmitter

The RF frequency synthesizer is used as a *local oscillator* (LO) in the transmitter to perform frequency translation. Fig. 1.6 shows a conventional direct up-conversion transmitter. The *in-phase* (I) and *quadrature* (Q) pulse-shaped digital baseband signals are converted into analog domain with *digital-to-analog* (D/A) converters. Due to their digital nature, the D/A outputs exhibit strong sampling-time harmonics and switching noise which have to be conditioned with *low-pass filters* (LPF) before being up-converted to the RF carrier by a modulator, which is a critical RF/analog block. The *power amplifier* (PA) is the last stage of the transmitter path. It performs antenna impedance matching and brings the emitted signal to the required power level. A major weakness of this mixer-based transmitter architecture is that even a small mismatch in phase shift or amplitude gain between the I and Q paths can significantly impair the system performance. Furthermore, because of a certain amount of inherent frequency shift between the modulator input and output (it performs frequency translation by design), the strong power amplifier signal can cause frequency pulling of the oscillator through injection locking. This mechanism finds parasitic paths, such as substrate, power and ground lines as well as electromagnetic radiation to feed strong PA signal into most sensitive parts of the oscillator.

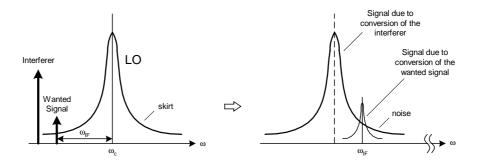

Figure 1.7. The effect of LO phase noise in a transmitter

The phase noise generated by the LO in the transmitter must be minimized due to the following reason. Fig. 1.7 indicates a problem when a noiseless receiver must detect a weak desired signal at frequency  $\omega_{c,1}$ , while a powerful, nearby transmitter generates a signal at frequency  $\omega_{c,2}$  with substantial phase noise. The wanted signal will be corrupted by the phase noise tail of the transmitter. This leads to a challenging noise requirement for the noise skirt of the RF LO. The tough standards for modern wireless communication systems result in very tight specifications on the close-in and far-out phase noise of synthesizers [16].

#### 1.2.3 Receiver

Figure 1.8. Zero-IF receiver topology

The RF frequency synthesizer is used as a *local oscillator* (LO) in the receiver to perform frequency translation and channel selection. Fig. 1.8 shows a modern zero-IF receiver architecture in which the LO is used to down-convert the RF signal directly into baseband without any *intermediate frequency* (IF) stages. Alternatively, due to dc-offset issues plaguing the true zero-IF architecture [17], the conversion could preferably be near-zero-IF. In this case, the IF signal does not get demodulated exactly to dc but a fraction of the signal bandwidth away.

The received RF signal at the antenna output port is immediately strengthen by a *low-noise amplifier* (LNA). It is then down-converted by an image-reject mixer into baseband. The *low-pass filters* (LPF) are used to keep the unwanted frequency components from being fed further in the receive chain. Variable-gain amplifiers bring the signal to the required level before it gets converted into digital form by the *analog-to-digital* (A/D) converter. The digital baseband processes both the *in-phase* (I) and *quadrature* (Q) parts and performs detection and other DSP processing.

This direct down-conversion architecture is considered to be the most suited for onchip integration since it does not rely on external high-Q tuning circuits for IF filtering. Unfortunately, it suffers from DC-offset problems due to LO leakage as well as self-mixing and various DSP-based cancellation methods must be used, which is an area of active research.

Figure 1.9. The effect of LO phase noise in a receiver

The requirement of the BLUETOOTH receiver is that a -70 dBm signal power in the 1 MHz bandwidth must be detected with a *bit error rate* (BER) of less than  $10^{-3}$ . The expected *signal-to-noise ratio* (SNR) at the non-coherent detector should be no less than 17 dB. The system must also be able to reject -10 dBm out-of-band single-tone blocking signals with a signal level of -67 dBm. The system must also pass an intermodulation test with a -39 dBm single-tone signal close to a -39 dBm BLUETOOTH-modulated interferer when the signal level is at -64 dBm. These impose stringent requirements on the RF LO. Figure 1.9 illustrates the effect of LO purity in a receiver. Since the wanted signal power is small and the interferer is large, the noise skirt of the LO must be low so that the wanted signal would not be corrupted after downconversion.

## **1.3** Towards the Direct Transmit Modulation

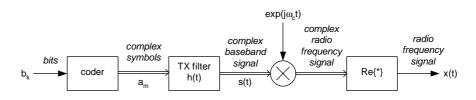

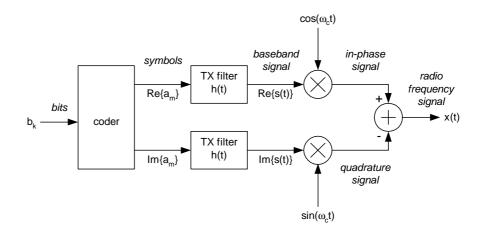

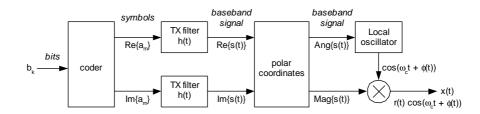

Figure 1.10. PAM modulation with complex signals

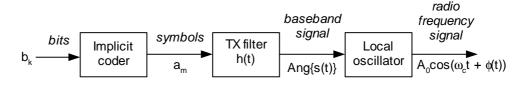

Fig. 1.10 illustrates a general block diagram of a transmit *pulse amplitude modulation* (PAM) using complex signals. It mathematically describes an arbitrary modulation process. The incoming bit stream  $b_k$  is fed to a coder, which converts the "0" or "1" digital bits into a stream of symbols  $a_m$ . A symbol assumes values from an alphabet. Since the coder may map multiple bits into a single data symbol, a distinction must be made between the symbol rate and the bit rate. In BLUETOOTH and GSM there is a one-to-one correspondence between the bits and symbols:  $\{0, 1\} \rightarrow \{-1, +1\}$ . More advanced encoding schemes, such as QPSK, for example, pack two bits into a symbol.

Symbols are applied to a transmit filter, which normally produces a continuous-time signal for transmission over the continuous-time channel. The main purpose of employing the baseband transmit filter is to properly and efficiently constrain the bandwidth occupied by the modulated RF spectrum. When rectangular pulses are passed through a bandlimited channel, the pulses will spread in time, and the pulse for each symbol will smear into the time intervals of succeeding symbols [18]. This causes *intersymbol interference* (ISI) and leads to increased probability of the receiver making an error in detecting a symbol. Out-of-band radiation in the adjacent channel in a mobile system should generally be 40 dB to 80 dB below that in the desired passband. Since it is difficult to directly manipulate the

transmitter spectrum at RF frequencies, spectral shaping is done through baseband.

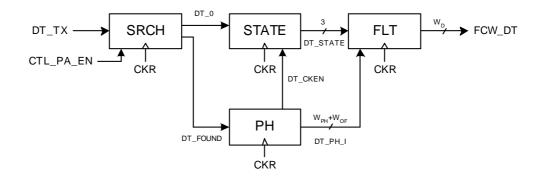

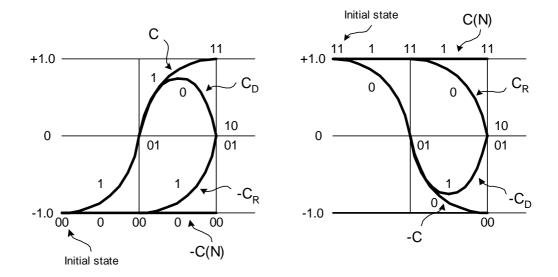

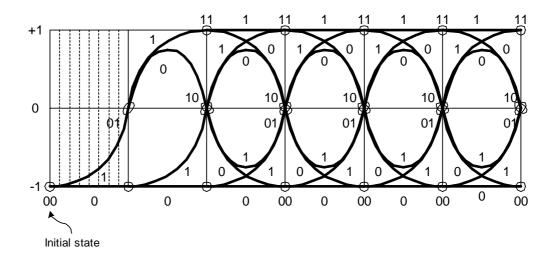

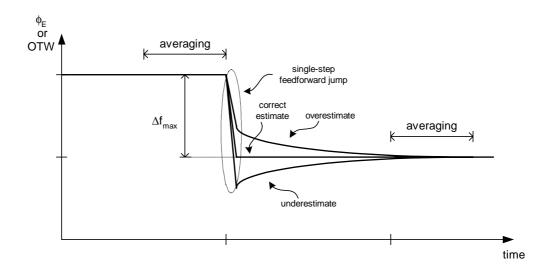

The impulse response h(t) of the transmit filter is called the pulse shape and could be raised-cosine or Gaussian. The raised-cosine rolloff filter belongs to the class of filters which satisfy the Nyquist criterion of no ISI at sampling instances. Gaussian filters, on the other hand, have a smooth transfer function but do not satisfy the Nyquist criterion and allow for a certain amount of ISI at zero-crossings. However, they can employ powerefficient non-linear amplifiers and are commonly used with frequency modulated signals.